Изобретение относится к технике передачи дискретной информации и может быть иснользовано при проектировании новой и модернизации существующей аппаратуры передачи дискретной информации, в которой применена решающая обратная связь (РОС).

Известное устройство анализа кодовых комбинаций состоит лишь из устройства обнаружения ошибок. В таких устройствах системы РОС не могут работать по каналам плохого качества.

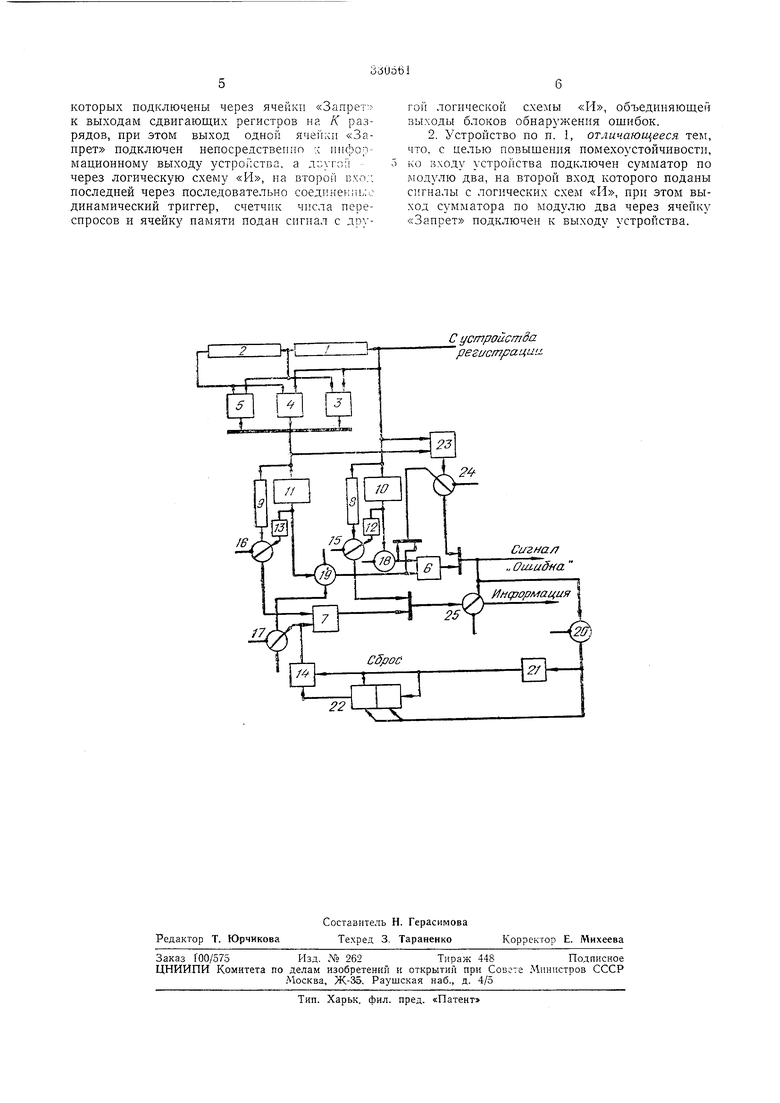

Цель изобретения - уменьшить среднее число переспросов и вероятность задержки сообщения при одновременном увеличении скорости передачи. Это достигается тем, что ко входу устройства подключены одповременпо вход сдвигающего регистра па К разрядов, вход блока обнаружения ошибок и вход одного из сдвигающих регистров на iih разрядов, нричем входы и выходы последних соединены со входами трех логических схем «И, выходы которых подключены ко входу второго регистра на /С разрядов и второму блоку обнаружения ошибок. Выходы блоков обнаружения ошибок через ячейки паашти подключены ко входу логической схемы «И п ко входу динамических триггеров, выходы которых подключены через ячейки «Запрет к выходам сдвигающих регистров на К раз- - f ifit,

рядов, при этом выход одной ячейки «Запрет подключен непосредственно к информационному выходу устройства, а другой - через логическую схему «И. На второй вход последней через последовательно соединенные динамический триггер, счетчик числа переспросов и ячейку памяти подан сигнал с дру,гой логпческой схемы «И, объединяющей выходы блоков обнаружения ошибок.

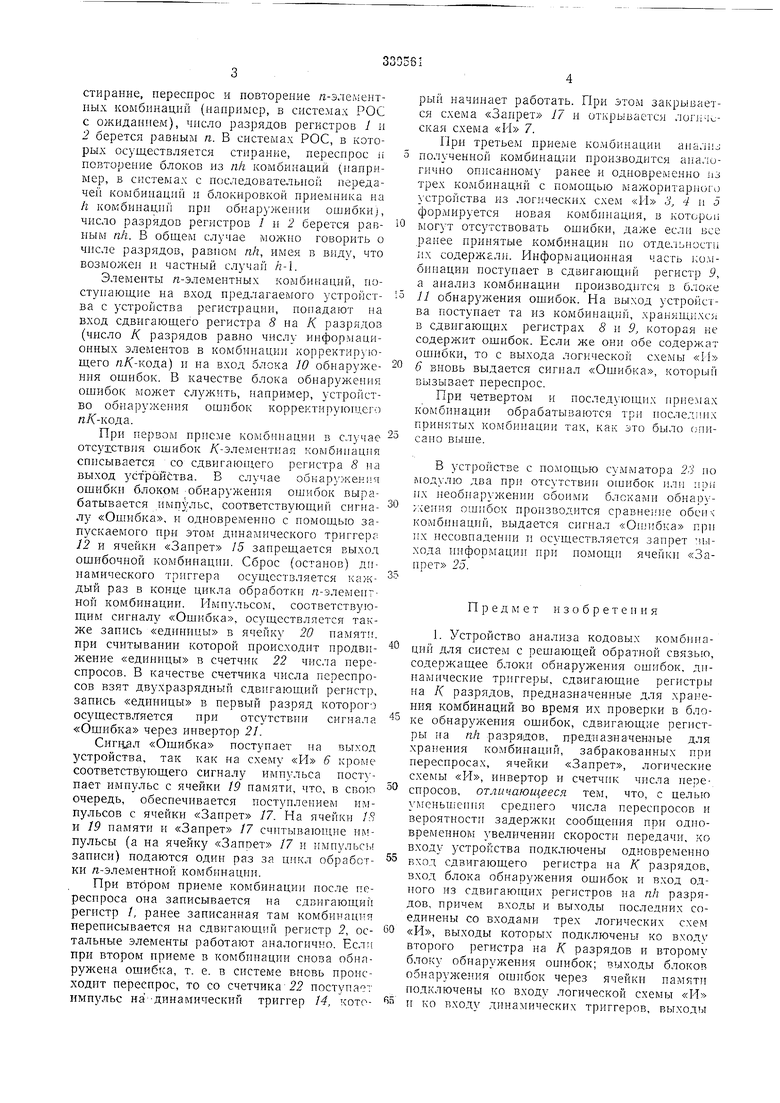

В целях повышения помехоустойчивости ко входу устройства подключен сумматор по модулю два, на второй вход которого поданы сигналы с логических схем «И, при этом выход сумматора по модулю два через ячей5 ку «Запрет подключен к выходу устройства. На чертеже прпведена блок-схема предлагаемого устройства.

Устройство состоит пз сдвигающих регпстров 7 п 2 на nh двоичных разрядов, логпческих схем «И 3-7, сдвигающих регистров S и 5 на К разрядов, блоков 10 п И обпаружения ошпбок, динамических триггеров /:. 13 п J4, ячеек «Запрет 75, 16 п 17, ячеек 18. 19 и 20 памяти, инвертора 21, счетчика 22

5 числа переспросов, сумматора 23 по модулю два, ячеек «Запрет п 25.

стирание, переспрос и повторение п-элементных комбинаций (например, в системах РОС с ожиданием), число разрядов регистров / и 2 берется равным п. В системах РОС, в которых осуществляется стирание, пересирос п повторение блоков нз iik комбинаций (например, в системах с носледовательной передачей комбинаций и блокировкой приемника на h кокбииаций при обнаружении ошибки, число разрядов регистров / и 2 берется равным nh. В общем случае можно говорить о чпсле разрядов, равном /г/г, имея в виду, что возможен ц чаетный случай /г-1.

Элементы п-элементных комбинацнй, ноступающие па вход предлагаемого устройства с устройства регистрации, попадают на вход сдвигающего регистра 8 ва К разрядов (число К разрядов равно числу информационных элементов в комбннацкп корректирующего п/С-кода) и на вход блока 10 обнаружения ошибок. В качестве блока обнаружения ошибок может служить, например, устройство обнаружения ошибок корректнруюп1,сг:) л/С-кода.

При первом приеме комбинации в случае отсухствия ошибок /С-элементпая комбинация списывается со сдвигающего регистра 8 на выход устройства. В случае обнаружения ошибки блоком обнаружения ошибок вырабатывается импульс, соответствующий сигналу «Ошибка, и одновременно с помощью запускаемого при этом динамического триггер 12 и ячейки «Занрет 15 запрещается выход ошибочной комбннации. Сброс (останов) динамического триггера осуществляется каждый раз в конЦе цнк.та обработкн л-элементной комбинации. Импульсом, соответствующим сигналу «Ошибка, осуществляется также запись «единицы в ячейку 20 памяти. при считывании которой нроисходнт нродвнжепие «единнцы в счетчнк 22 числа переспросов. В качестве счетчика числа переспросов взят двзхразрядный сдвнгающий регнстр, запись «единицы в первый разряд которого осуществляется при отсутствии сигнала «Ошибка через инвертор 2/.

Сигщл «Ошибка поступает на выход устройства, так как на схему «И 6 соответствующего сигналу импульса поступает импульс с ячейки 19 памяти, что, в свою очередь, обеспечивается поступлением импульсов с ячейки «Запрет 17. На ячейки 8 и 19 намятп и «Запрет 17 счптывающне нмпульсы (а на ячейку «Заноет 17 и импульсь записи) подаются один раз за цикл обработки /г-элементной комбннации.

При втбром приеме комбинации после переспроса она записывается на сдвигающий регнстр /, ранее записанная там комбинация переписывается на сдвигающий регнстр 2, остальные элементы работают аналогично. Есл1 при втором приеме в комбинации снова обнаружена ошибка, т. е. в системе вновь пронсходнт переспрос, то со счетчика 22 постунает импульс на -динамический триггер 14, который начинает работать. При этом закрывается схема «Занрет 17 и открывается лоп.чсская схема «И 7.

При третьем приеме комбинации анал1и полученной комбннации производится ана.югнчно описанному ранее и одновременно i3 трех комбинаций е помощью мажорнтариого устройства из логических схем «И и, 4 и 5 формируется новая комбннацня, в которои могут отсутствовать ошибкн, даже если все ранее нринятые комбинации ио отдельности их содержали. Информационная часть ;ол1бииации поступает в сдвигающий регистр 9, а аналнз комбннацни производится в блоке 11 обнаружения ошибок. Иа выход устройства ноступает та из комбинаций, хранящихся в сдвигающих регистрах 8 н 9, которая не содержит ошибок. Еслн же они обе содержат ошибки, то с выхода логической схемы «И 6 вновь выдается сигнал «Ошибка, который вызывает переенрос.

При четвертом и последующих приемах комбинации обрабатываются три носледних принятых комбииации так, как это было (;пнсано выше.

В устройстве с иолющью су.мматора 23 ио йюдулю два при отсутствии ошибок 1Л11 при их необнаружении обоими блоками обнару хе11ия ошибок производится сравиегне обей ч комбинаций, выдается сигнал «OHJu6Ka ири нх несовпадении и осуществляется запрет U:.iхода инфор.мацнн нри помощи ячейки «Запрет 25.

Предмет н з о б р е т е и н я

1. Устройство аналнза кодовых комбннацни для систем с решающей обратной связью, содержащее блоки обнаружения ошибок, дннамнческие триггеры, сдвигающие регистры на /( разрядов, предназначенные для хранения комбинаций во время их нроверки в блоке обнаруження ошибок, сдвигающие регистры на nh разрядов, предназначенные для хранения комбинацнй, забракованных при переспросах, ячейки «Запрет, логические схемы «И, инвертор н счетчик числа переепросов, отличающееся тем, что, с целью уменьнюпня средиего числа переспросов и вероятности задержки сообщения при одновременном увелнченнн скоростн передачи, ко входу зстройства подключены одновременно вход сдвигающего регистра на К разрядов, вход блока обнаруження ошибок н вход о.аного нз сдвигающих регистров на nh разрядов, причем входы и выходы последних соединены со входами трех логических схем «И, выходы которых подключены ко входу второго регистра на К разрядов н второму блоку обнаружения ошибок; выходы блоков обнаружения ошибок через ячейки намяти нодключены ко входу логической схемы «И н ко входу дннамнческнх трнггеров, выходы

которых подключены через ячейки «Запрет- к выходам сдвигающих регистров на /С разрядов, при этом выход одной ячейки «Запрет подключен непосредствеппп л информационному выходу устройства, а через логическую схему «И, на второй вхо.; последней через последовательно соединенные динамический триггер, счетчик числа иересиросов и ячейку памяти подан сигнал с дп гой логической схемы «И, объединяющей выходы блоков обнаружения ошибок.

2. Устройство по п. 1, отличающееся тем, что. с целью повышения помехоустойчивости, ко 15ходу устройства подключен сумматор по модулю два, на второй вход которого поданы сигналы с логических схем «Н, при этом выход сумматора по модулю два через ячейку «Запрет подключен к выходу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1979 |

|

SU866767A2 |

| Устройство для декодирования с защитой от ошибок | 1990 |

|

SU1765900A1 |

| УСТРОЙСТВО для ЭКСПЕРИМЕНТАЛЬНОГО ИССЛЕДОВАНИЯ | 1971 |

|

SU297963A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОДИНОЧНЫХ и ОБНАРУЖЕНИЯ МЯОЮКРАТНЫХ ОШИБОК | 1967 |

|

SU196441A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ КОММУТАЦИИ КАНАЛОВ | 2007 |

|

RU2341046C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК | 1973 |

|

SU363979A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

п$

Сигна/7

Даты

1972-01-01—Публикация