(54) АНАЛИЗАТОР КОДОВЫХ КОМБИНАЦИЙ ДЛЯ УСТРОЙСТВ

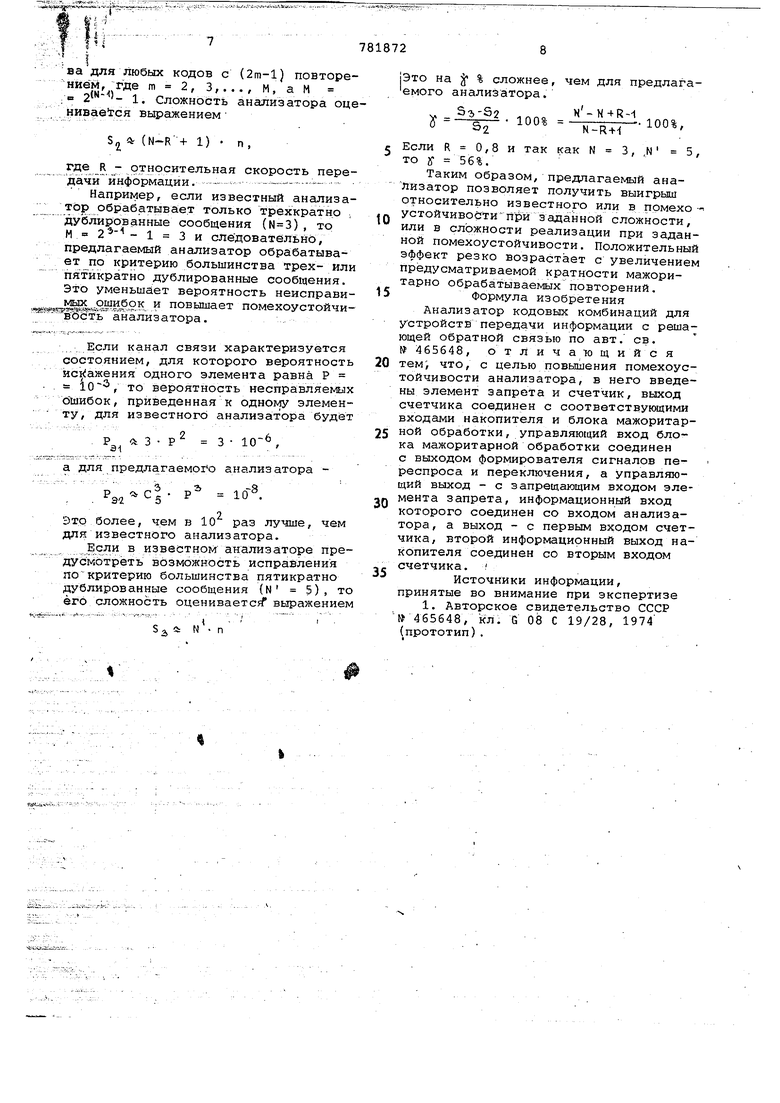

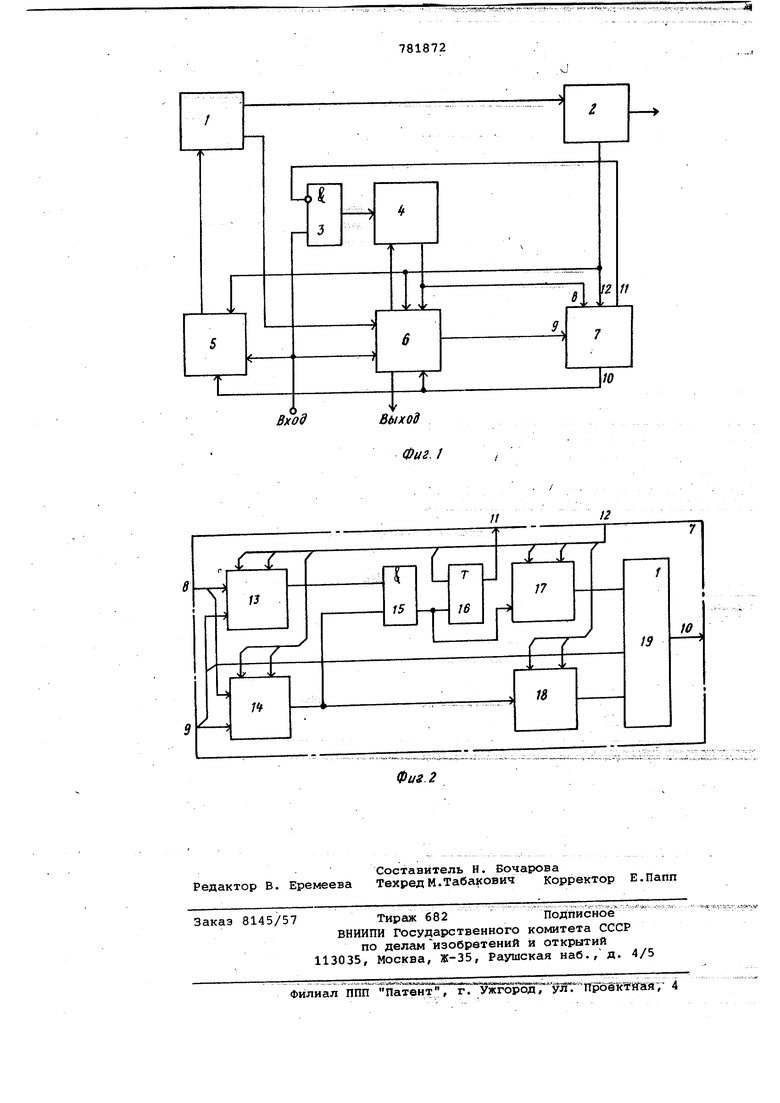

ПЕРЕДАЧИИНФОРМАЦИИ с РЙЯАЮЩЁЙ ОБРАТНОЙ связью Изобретение относится к области передачи данных, может использовать ся в устройствах защиты от ошибок. По основному авт. св. № 465648 . известно устройство, содержащее накопитель , первый информационный выход которого соединен со входом бло ка мажоритарной обработки, выход ко торогр соединен с первыми информаци онными входами накопителя и переклю чателя, вторые информационные входы которых соединены со входом анализатора, выход переключателя соединен со входом блока обнаружения ошибок, первый выход которого соединен с первым управляющим входом накопителя, второй выход - со входом формирователя сигналов переспроса и переключения , выход которого соединен с управляющим входом переключателя и вторым управляющим входом накопителя 1. Недостаток устройства - низкая поме хоустойчивость, обусловленная тем, что оно обеспечивает мажоритарную обработку только N - кратно дублированных сообщений при наличии (N-1) регистров сдвига для запомина.ния сообщений. Цель изобретения - повышение помехоустойчивости анализатора. Поставленная цель достигается тем, что в анализатор кодовых комбинаций для. устройств передачи информации с решающей обратной связью введены элемент запрета и счетчик, выход счетчика соединен с соответствую1цими входами накопителя и блока мажоритарной обработки, управлягаций вход блока мажоритарной обработки соединен с выходом формирователя сигналов переспроса и переключения, а управляющий выход - с запрещающим входом элемента запрета, информационный вход которого соединен со входом анализатора , а выход - с первым входом счетчика , второй информационный вход накопителя соединен со вторым входом счетчика. Этим достигается возможность исправления ошибок в любом наборе () дублированных сообщений с ошибками , где ,3, ..., М, аМ 2 - 1, что увеличивает исправляющие возможности анализатора. Если известный анализатор при Н 3 обрабатйвает по критерию большинства только трехкратно дублированные сообщения, то предлагаемый анализатор практически при той же сложности обеспечивает мажоритарную обработку, трех-, пятикратно дублированньах сообщений. На фиг. 1 изображена функциональная схема анализатора; на фиг, 2 варианта блока мажоритарной обработки. Анализатор кодовых комбинаций (фиг. 1) содержит блок 1 обнаружения ошибок, формирователь 2 сигналов перепроса и переключения, элемент 3 запрета, счетчик 4, переключатель 5, накопитель б и блок 7 мажоритарной обработки, дополнительный вход 8 бло ка 7, информационные вход 9 и вход 10 блока 7, управлягачие выход 11 и вход 12 блока 7. Блок 1 обнаружения ошибок обеспечивает проверку кодовых комбинаций обнаруживающего (п, k) - кода на наличие или отсутствие ошибок. Формиро ватель 2 вырабатывает сигнал переспр са при обнаружении ошибок в проверяе мых комбинациях, подсчитывает число переспросов и выдает управляющие сиг Р1алы на блоки анализатора. Элемент 3 запрета фиксирует насыщение счетчика 4, который подсчитывает число единиц в одйоименных элементах дублируемых кодовых комбинаций с ошибками. Число двоичных разрядов счетчика 4 равно N-1. Если использовать специальный счетчик с насыщением, то элемент 3 запрета отсутствует. Переключатель 5 подключает блок 1 обнаружения ошибок ко входу анализатора или к выходу блока 7 мажоритарной.обработки. Накопитель 6 содержит (N-l)n - разрядных регистров сдвига для записи цифровых кодов (зона цифровых кодов) соответствующих числу единиц в принимаемых (2т-1) повторениях, где m .2, 3,.,., И, а М 1. Таким образом., если в известном анализаторе накопитель служит для запоминания (N-1) повторений при мажоритарной об работке N повторений, то в предлагаемом анализаторе такое же чйВйб рё- гистров обеспечивает запоминание циЪ ровйх кодов числа единиц и мажоритар ную обработку (2т-1) повторений. Кро ме того, накопитель 6 содержит«один п-разрядный регистр сдвига для запоминания принимаемой в данный момент кодовой комбинации, а известный анализатор - К-разрядный регистр сдвига. Блок 7 обеспечивает формирование мгикоритарного результата из цифровых кодов, j34HTHBaeMbix из накопителя 6. Для возможного варианта при N . 3 блок 7 мажоритарной обработки (фиг.2 содержит переключатели 13 и 14, SJieмен,: И 15, триггер 16, ключи Л7 и 1 и элемент ИЛИ 19. При использовании счетчика 4 с насыщением о.тсутствует триггер 16, выход 11 и соответству ющЖя сйязь. Работает анализатор следующим об разом (при N . 3) . На вход анализатора поэлементно поступают п-элементные кодовые комбинации (п, k)-кoдa. Первая комбинация записывается в накопитель б и одновременно через переключатель 5 вводится в блок 1 обнаружения ошибок, элементы этой комбинации через элемент 3 запрета подаются на двухразрядный .() счетчик 4, который подсчитывает число единиц в одноименных элементах повторений. Цифровые коды, соответствующие числу принятых единиц, считываются со счетчика 4, запоминаются дополнительно в накопителе б и используются для начальной установки разрядов счетчика при приеме каждого элемента следующего повторения, что позволяет вести непрерывный счет числа единиц в одноименных элементах принимаемых повторений. По окончании приема первой комбинации она будет записана в накопителе б дважды в п-разрядном регистре и в зоне цифровых кодов. Если ошибка не обнаружена, сигнал с первого выхода блока 1 обнаружения ошибок подается на первый управляющий вход накопителя 6 и разрешает задачу информационных элементов получателю. В случае обнаружения ошибки сигнал с второго входа блока 1 обнаружения ошнг бок поступает на вход формирователя 2 сигналов переспроса и переключения, который выдает сигнал на формирование команды переспроса и подсчитывает число переспросов. Второе повторение принимается аналогично первому, записывается в накопитель б на место первого, поступает в блок 1 обнаружения ошибок и через элемент 3 запрета поступает на счетчик 4. Перед приемом каждого i-го элемента принимаемого повторения из зоны цифровых кодов накопителя б считывается цифровой код, соответствугапий числу единиц в i-X одноименных элементах ранее принятьтх повторений. Этот код поступает на установочный (второй) вход счетчика 4 и осутпествляет начальную установку двух разрядов счетчика (например, 10, что указывает на прием одной 1 в предыдущих .повторениях). Если i-и элемент принимаемого повторения 1, то счетчик 4 переходит в состояние 01 и этот цифровой код считывается со счетчика 4 и записывается в зону цифровых кодов накопителя б, как скорректированный (обновленный). Если в очередном повторении ошибка не обнаружена, то информационная часть выдается получателю и накопитель б устанавливается в исходное О состояние.... При плохом канале связи после того, как сформировано, для переспроса и накоплены цифровые коды, сортветствуклцие числу единиц в одноименных элементах двух повторений, сигнал с выхода формирова теля 2 .поступает на . управляющие входы переключателя 5, накопителя б и блока 7 мажоритарной обработки, который при помо1ди перекл чателей 13, 14 подключается к выходу счетчика 4, а его выход через переключатель 5 - ко входу-блока 1 обнаружения ошибок. При приеме третьего повторения в счетчике 4 происходит коррекция (обновление) цифровых кодов, которые со ответствуют числу единиц в одноименных элементах трех повторений сообщения, записываются в накопитель 6 и поступают в блок 7 для формирования мажоритарного результата по критерию два из трех. В этом случае открыт ключ 18 и старшие разряды циф ровых кодов через переключатель 14, ключ 18 и элемент ИЛИ 19 поступают на выход блока 7, как результат мажоритарной обработки, который через переключатель 5 подается в блок 1, где проверяется на отсутствие ошибок Если ошибка не обнаружена, то по сиг налу из блока 1 цифровые коды поступают в блок 7 мажоритарной обработки повторно из накопителя б (переключатели 13 и 14 после каждого цикла обработки возвращаются в исходное состояние сигналами синхронизации и в данный момент соединяют выход накопителя б со схемой мажоритарной обработки блока 7). Результат мажоритарной обработки (информационная часть) проходит транзитом через накопитель 6 и поступает на выход анализатора. При обнаружении ошибки сиг нал со второю выхода блока 1 обнару жения ошибок поступает на вход формирователя 2, где используется для получения сигнала переспроса. В последнем случае вслед за выдачей цифровых кодов из накопителя б выдается третья комбинация. Однако выдача ком бинации и ее обработка проводятся на тактовой частоте, превышающей скорость модуляции принимаемой информации, чтобы обработка третьей комбина ции была закончена до прихода первого элемента очередной комбинации. Третья комбинация транзитом (без изменения) проходит через блок 7 мажоритарной обработки, переключатель 5 и вводится в блок 1 обнаружения ошибок. В накопителе б данная комбинаци перезаписывается. При необнаружении ошибки сигнал с первого выхода блока 1 обнаружения ошибок поступает на пе вый управляющий вход накопителя 6 и разрешает выдачу информационных элементов третьей комбинации. В случае обнаружсрния ошибки сигнал со второго выхода блока 1 подается на вход формирователя 2, где совместно с сигналом ошибки результата мажоритарной обработки формирует сигнал, организующий очередной переспрос. Четвертое повторение принимается и анализируется аналогично рассмоту ренному. Однако цифровые коды корректируются (обновляются) только в том I случае, если счетчик 4 не оказывается в режиме насыщения (состояние и ) при его начальной установке. Для этого блок 7 мажоритарной обработки на момент считывания цифрового кода из накопителя 6 для начальной установки счетчика 4 подключа ется к выходу накопителя 6. Если цифровой код 11, тосигналы проходят через переключатели 13 и 14, поступают на входы элемента И 15 и переводят в единичное состояние триггер 16. Сигнал с выхода 11 блока 7 мажоритарной обработки проходит на зaпpeщa oщий вход элемента За аппрета, запрещая прохождение единичных сигналов принимаемого повторения для данного состояния:, что исключает коррекцию цифрового кода, соответствующего насыщению счетчика 4. В конце такта триггер 16 устанавливается в О. При обнаружении сяиибки в четвертом повторении организуют переспрос и начинают прием пятого повторения. Все необходимые управляющие сигналы формирует формирователь 2. в момент считывания цифровых кодов из накопителя 6 для начальной установки счетчика 4 блок 7 мажоритарной обработки переключателями 13 и 14 подключается к выходу накопителя 6. Этим обеспечивается фиксация состояния насыщения счетчика 4 и запрещение коррекции соответствующего цифрового кода сигналом с выхода 11 блока 7 мажоритарной обработки. Далее на момент считывания цифровых кодов с вькода счетчика 4 блок 7 мажоритарной обработки подключается переключателями 13 и 14 на выход счетчика 4 и открывается ключ 17. Результат мажоритарной обработки по критерию три из пяти формируется элементом И 15 и через открытый ключ 17 элемент ИЛИ 19 поступает на выход блока 7 мажоритарной обработки, проходит переключатель 5 и анализируется блоком 1 обнаружения ошибок. Дсшьнейшая обработка результата мажоритарной обработки по критерию три из пяти и пятого повторения, осуществляются аналогично тому, как. это делается для результата маоритарной обработки по критерию два из трёх и третьего повторения. Предлагаемый анализатор обладает более высокой технико-экономической эффективностью, чем известный, в котором возможна мажоритарная обработка только N-кратко дублированных сообщений. При этом сложность его (в элементах памяти) оценивается величиной S N . п Предлагаемый анализатор практически при той же сложности позволяет исправлять ошибки по критерию болыиинст l . -- - 781872

(2гт)-1) повторева для любых кодов с нйём, где m 2, 3,.. . , М, а М в 1. Сложность анализатора оценивается выражением

Sj (N-R+ 1) . n

где R - относительная

скорость передачи информации. Например, если известный анализатор обрабатывает только трехкратно , дублированные сообщения () , то М 1 3 и следовательно, предлагаемый анализатор обрабатывает по критерию большинства трех- или пятикратно дублированные сообщения. Это уменьшает вероятность неисправи -йг ЙШйбок, ,Р повышает помехоустойчи вЬс-лъ анализатора, Если канал связи характеризуется состоянием/ для которого вероятность искажения одного элемента равна Р iO, то вероятность несправляемых бшибок, приведенная к одному элементу, для известного анализатора будет

-6

а 3

3-10

Э-1

для предлагаемого анализатора 10.

,3 .а

5

31

Это более, чем в 10 раз лучше,

чем для известного анализатора.

Если в известном анализаторе предусмотреть возможность исправления покритерию большинства пятикратно дублированные сообщения (N 5), то его сложность оцениваете) выражением

N

8

1Это на % сложнее,

чем для предлагаемого анализатора.

Если

ТО у 56%.

Таким образом, предлагаемый анализатор позволяет получить выигрыш относительно известного или в помехо УСТОЙЧИВОСТИ пш заданной сложности, или в сложности реализации при заданной помехоустойчивости. Положительный эффект резко возрастает с увеличением предусматриваемой кратности мажоритарно обрабатываемых повторений. Формула изобретения

Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью по авт. св. 465648, от Л и ч ато щ ийс я тем; что, с целью повышения помехоустойчивости анализатора, в него введены элемент запрета и счетчик, выход счетчика соединен с соответствукяцими входами накопителя и блока мажоритарной обработки, управляющий вход блока мажоритарной обработки соединен с выходом формирователя сигналов переспроса и переключения, а управляющий выход - с запрещающим входом элемента запрета, информационный вход которого соединен со входом анализатора, а выход - с первым входом счетчика, второй информационный выход накопителя соединен со вторым входом счетчика. /

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР №465648, кл. G 08 С 19/28, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1981 |

|

SU1005151A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1980 |

|

SU951732A2 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Устройство для мажоритарного декодирования | 1982 |

|

SU1073788A1 |

| Устройство для приема и мажоритарного декодирования информации | 1981 |

|

SU980114A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1979 |

|

SU866767A2 |

12

ft

Авторы

Даты

1980-11-23—Публикация

1978-12-26—Подача