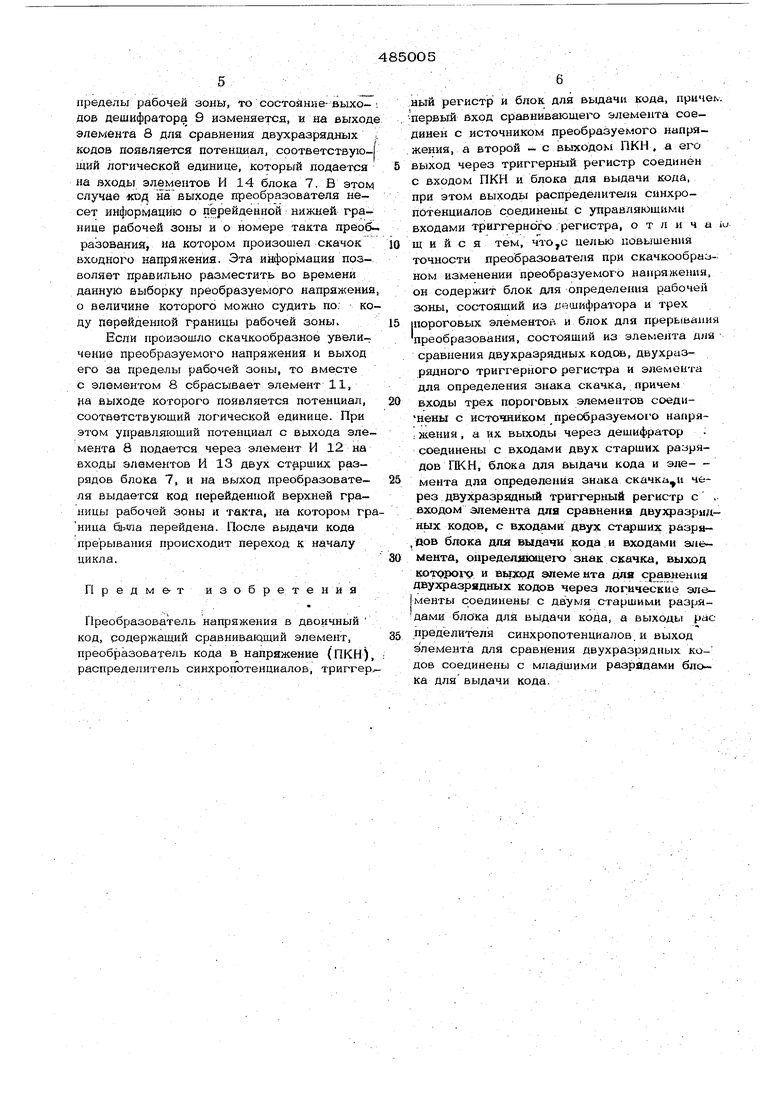

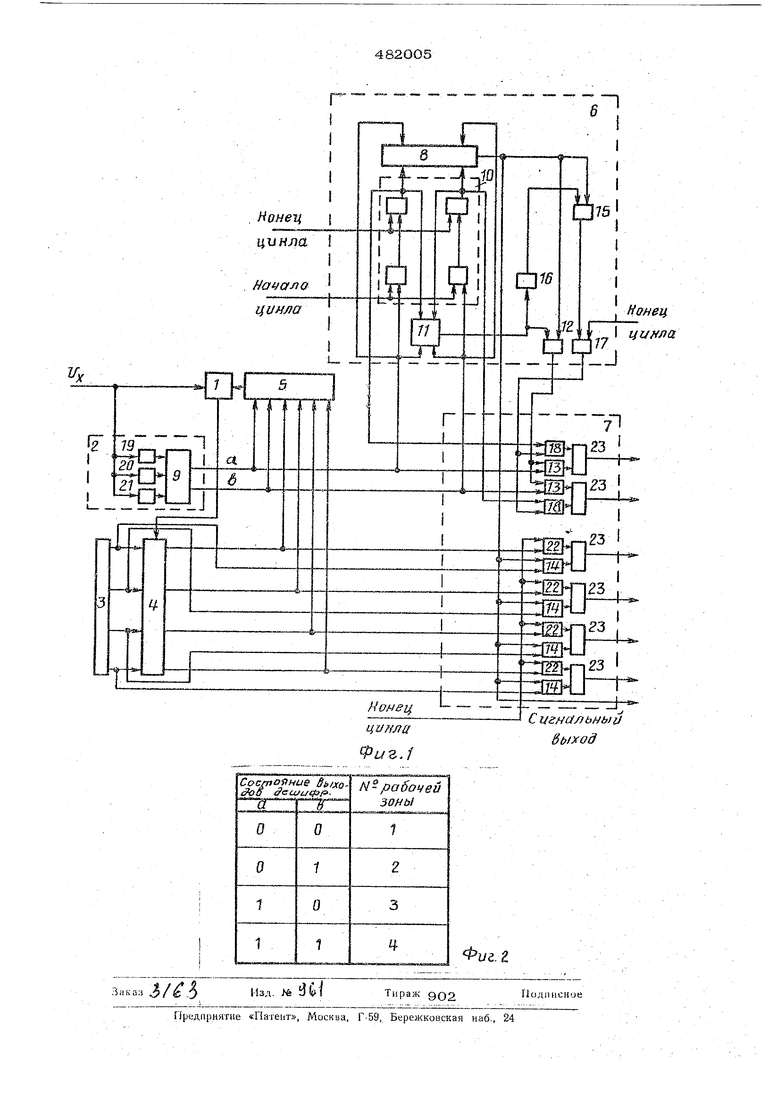

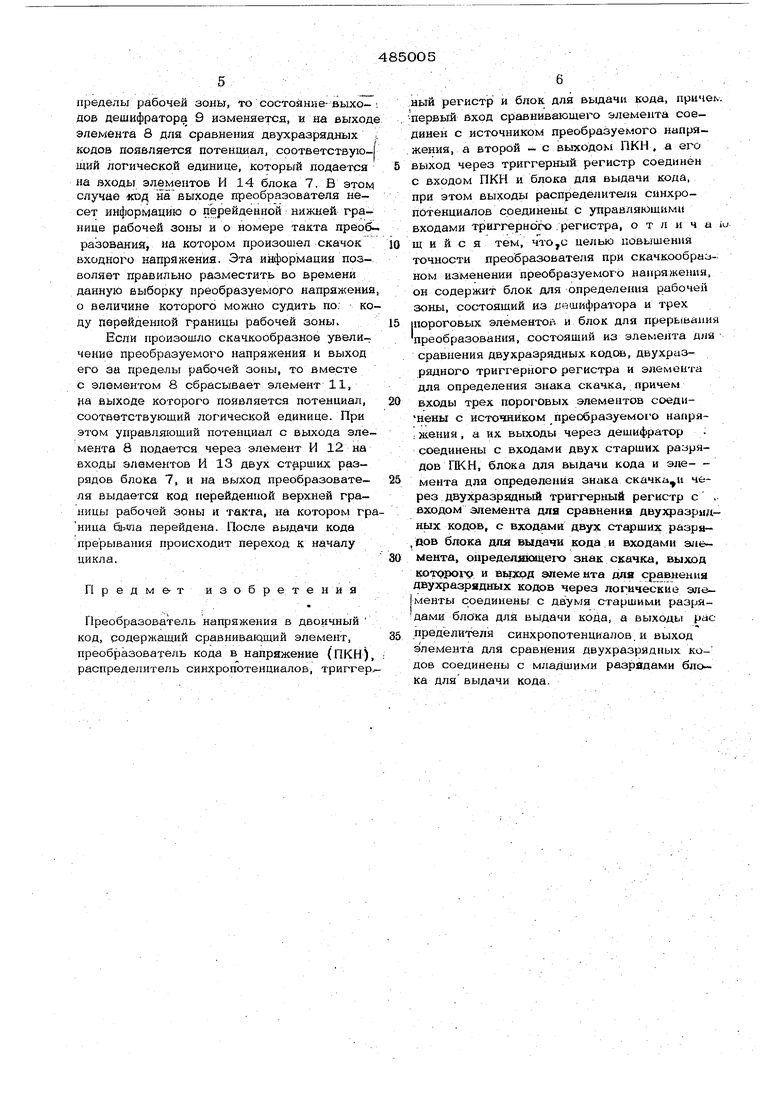

(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ДВОИЧНЫЙ КОД На фиг. 1 приведена структурная элек трическая схема пр бразоватег1Я; на фиг. 2 - таблица состояний выходов дешифратор Преобразователь напряжения в двоичный код содержит сравнивающий элемент . 1, блок 2, определяющий рабочую зону, распределитель синхропотенниалов 3, триг :герный регистр4, ПКН 5, блок 6 для пре рывания преобразования, блок 7 для выдачи кода , Блок 6 выполнен в виде элемента 8 для сравнения двухразрядных кодов, он связан. с дешифратором 9, причем к элементу 8 присоединен двухразрядный триггерный ре-у гистр 10 и элемент 11 для определения . знака скачка. Входы элемента 11 связаны с выходам дешифратора 9 и выходами .дв ухразрядного регистра. 10. Входы регистра Ю соединены с выходами дешифратора 9, а выход элемента 11 и выход элемента 8 подсое....ДИнены к логическому элементу И 12, выход которого подключен к входам логичес.ких элементов И 13 двух старших разрядо блока 7. Выход элемента 8 соединен также с си гнальным выходом преобразователя и первы ми входами логических элементов И 14, вторые входы которых связаны с выходами {распределителя синхропотенциалов 3. Кроме того, вы.ход элемента 8 подсое..динен через логический элемент И 15, с вторым входом которого через игшертор 16 соединен выход элемента 11 и элемент ИЛИ 17 к логическим элементам И 18 двух старших разрядов блока 7.. Вторые входы элементов И 18 связаны с выходам триггернрто регистра 10. Пороговые элементы 19, 2О, 21 входящие в состав блока 2, соединены с дешифратором 9, выходы которого подключены к ПКН 5. Выходы ПКН 5 подсоединены к сравни- Бающему элементу 1, выход которого свя|3ан с триггерным регистром 4, Выходы распределителя 3 соединены с управляющими входами регистра 4, а выходы последнего связаны с входами ПКН 5 и через логические элемейты И 22 соединены с входами логических элементов ИЛИ 23 младших разрядов Гёлока1 7, .I Выходы элементов И 13, И 18, а так.же И 14, И 22, относящихся к одному и тому же разряду блока 7, объединяются попарно элементами : ИЛИ 23. Преобразователь работает следующим образом. В начале цикла преобразуемое напряжение подается на первый вход сравниваю- liuero элемента 1 и входы пороговых элемен гоЬ 19, 20, 21, На управляющий, вход триггерного регистра 1О, входящего в состав блока 6, поступает кратковременный / сигнал Начало цикла.; В зависимости от того, сколько поро говых элел(ентов сработало к молшнту начал а ЦИ1ша, возбуждена та или иная (или обе вместе) выходная шина дешифратора 9. В результате в триггерный регистр 10 будет записан код нижней границы рабочей зоны, в пределах которой оказался уровень преобразуемого напряжения. Имеется четыре рабочих зоны преобразователя в соответст-, ствии с состояниями выходов Дешифратора 9 (см. фиг. 21 Управляющий потенциал воз™ бужденной ШИНЫ; дешифратора 9 производит включение эталонного напряжения в ПКН 5 соответствующего весу данного старшего разряда, которое подается на второй вход сравнивающего элемента 1. частично, компенсируя .преобразуемое напряжение. Нескомпеч- | сированная часть входного напряжения преобразуется затем в двоичный код по методу / поразрядного кодирования. . ,i iaKi-овые синхропотенциалы с распределителя 3 последовательно устанавливают в единичное состояние триггеры регистра 4, начиная с триггера старшего разряда, выходы которых управляют включением эталонных напряжений в ПКН 5. Синхропотенциал, устанавливаюший в 1 очередной триггер, возвращает или не возвращает предыдущий триггер регистра 4 в нулевое состояние в зависимости оч- сигнала элемента 1. При установке -го триггера в 1 производится включение эталонного напряжения в 1ЖН 5, соответствующего весу i -го разряда, Это эталонное напряжение суммируется в ПКН 5 с напряжениями, включенными в пре- |дыдущих тактах преобразования. Если в результате сравнения входного напряжения U и суммы эталонных напряжений U-. оказалось что .,-r. то л Э нал на выходе элемента 1 соответствует логической единице, и ( i + 1)-и такто- ;1 DfDiM Синхропотенциал изменит сосюяиие i триггера на О, отключив таким образом I ™е эталонное апряжение, и установит (1 +-1)-и триггер регистра 4 в 1. В кЪнце цикла преобразования на логические элементы И 22 подается сигнал Конец цикла. Этот же сигнал поступает через элемент ИЛИ 17 на элементы И 18. Сформированный на дешифраторе 9 и триггерном регистре 4 код выдается на вы.ход преобразователя. Если во время цикла преобразования произошло скачкообразное уменьшение преобразуемого напряжения и выход его за

пределы рабочей зоны, то;состояш1е-выхо-. дов дешифратора 9 изменяется, и на выходе элемента 8 для сравнения двухразрядных .: кодов появляется потенциал, соответствующий логической единице, который подается

на входы элементов И 14 блока 7. В этом. случае «од невыходе преобразователя несет информацию о перейденной г нижней границе рабочей зоны и о номере такта преобразования, на котором произошел скачок входного напряжения. Эта информация позволяет правильно разместить во времени данную выборку преобразуемого напряжения, о величине которого можно судить по; коду перейденной границы рабочей зоны.

Если произошло скачкообразное увеличение преобразуемого напряжения и выход его за пределы рабочей зоны, то вместе с элементом 8 сбрасывает элемент 11, fta выходе которого появляется потенциал, соотаетствуюший логической единице. При этом управляющий потенциал с выхода элемента 8 подается через элемент И 12 на входы элементов И 13 двух старших разрядов блока 7, и на выход преобразователя выдается код перейденной верхней границы рабочей зоны и такта, на котором граница Qt-via перейдена. После выдачи кода прерывания происходит переход к началу цикла..

Предме-т изобретения

Преобразователь напряжения в двоичный код, содержащий сравнивак ш.ий элемент,

преобразователь кода в напряжение (ПКН), распределитель синхропотенциалов, триггер

6

вый регистр и блок для вьщачи кода, приче первый вход сравнивающего элемента соединен с источником преобразуемого напря,жения, а второй - с выходом ПКН, а его выход через триггерный регистр соединен с входом ПКН и блока для выдачи кода, при этом выходь распределителя синхропотенциалов соединены с управляющим входами триггерного .регистра, о т л и ч а щ и и с я тем, ,с целью повышения точности преобразователя при скачкообразном изменении преобразуемого напряжения, он содержит блок для определения рабочей зоны, состоящий из дешифра1Х)ра и трех пороговых элементов и блок для прерывани преобразования, состоящий из элемента для сравнения двухразрядных кодов, двухразрядного триггерного регистра и элемента для определения знака скачка, причем входы трех пороговых элементов соединены с источником преобразуемого нааряi жения , а их выходы через дешифратор . соединены с входами двух старших разрядов ПКН, блока для выдачи кода и эле

мента для определения знака скачками через двухразр5здный триггерный регистр с входом элемента для сравнения двузфазрлд ных кодов, с входами двух старших разря,йов блока дпя выдачи кода и входами элемента, определякмцего знак скачка, выход которого и выход эпеме нта для сравнения двухразрядных кодов через логические зле|менты соединены с двумя старшими разрядами блока для выдачи кода, а выходы рас предёлителя синхропотенциалов.и выход элемента для сравнения двухразрядных кодов соединены с млаДшими разрядами блока для выдачи Кода. Ноиец Фиг,1 Сигнальный Bbixod

| название | год | авторы | номер документа |

|---|---|---|---|

| УО:;СОЮЗНАЯ | 1973 |

|

SU363202A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU809553A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД | 1972 |

|

SU340078A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ДВОИЧНЫЙ КОД | 1967 |

|

SU190073A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1972 |

|

SU432675A1 |

| Преобразователь напряжения в код | 1979 |

|

SU841111A1 |

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1971 |

|

SU440784A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Преобразователь напряжения в код | 1976 |

|

SU577670A2 |

Авторы

Даты

1975-08-25—Публикация

1972-04-17—Подача