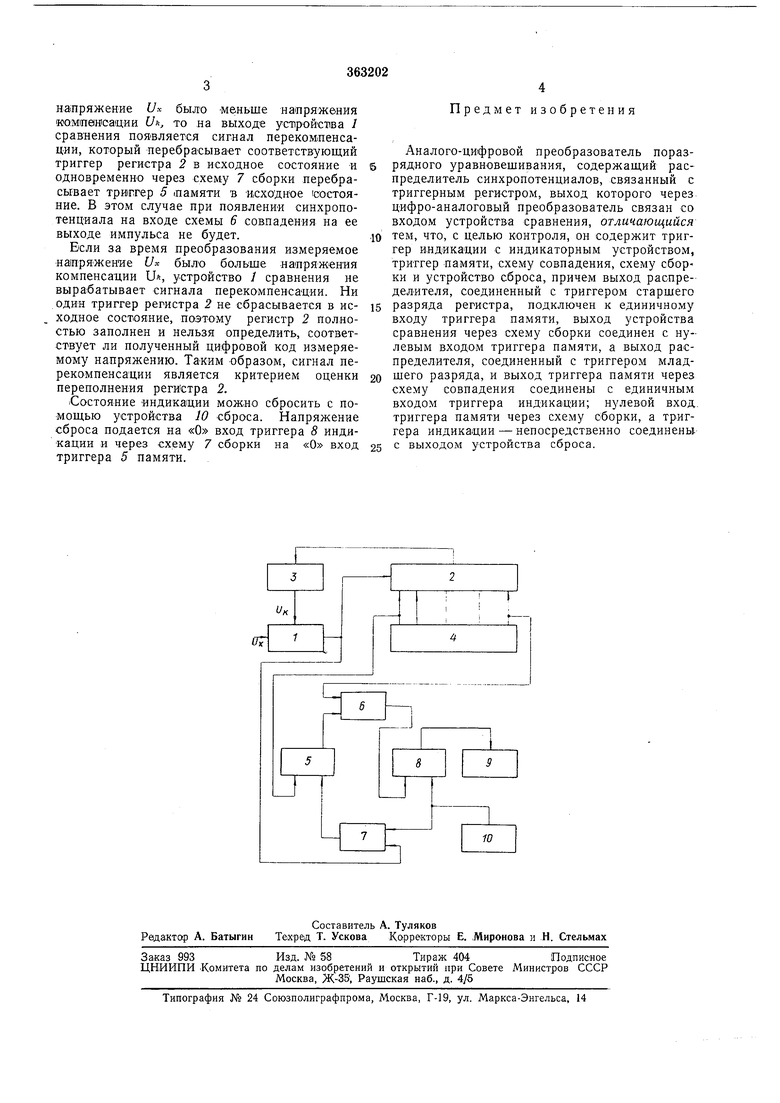

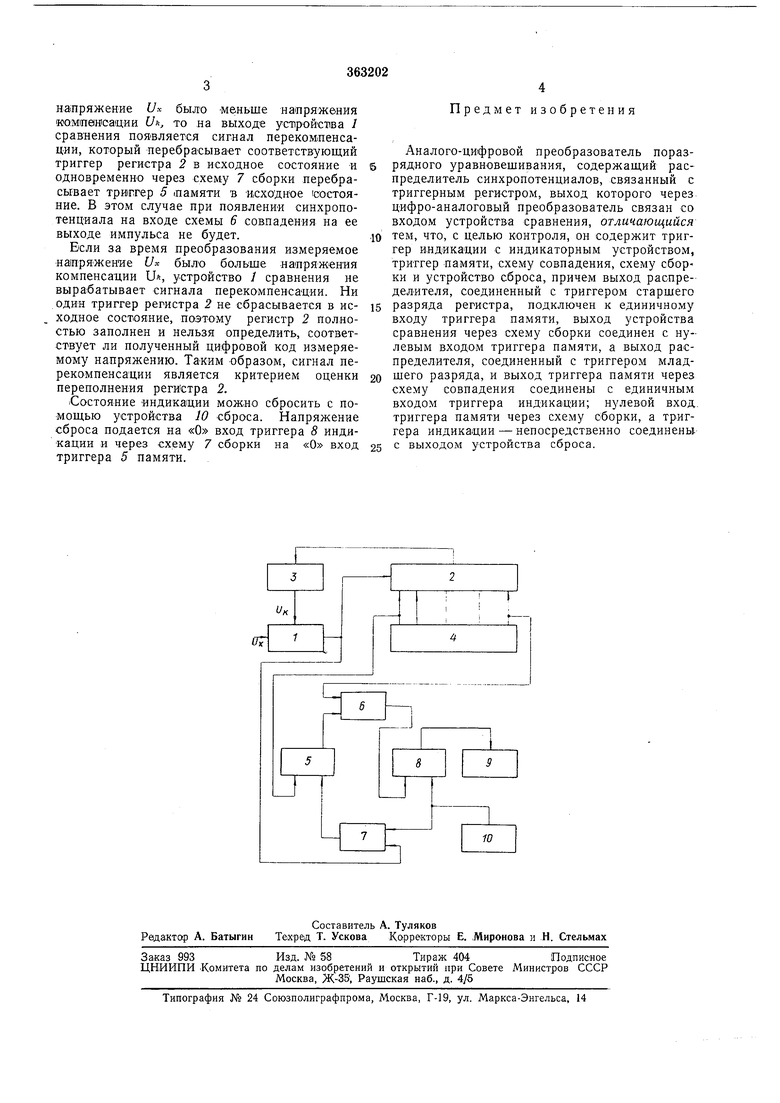

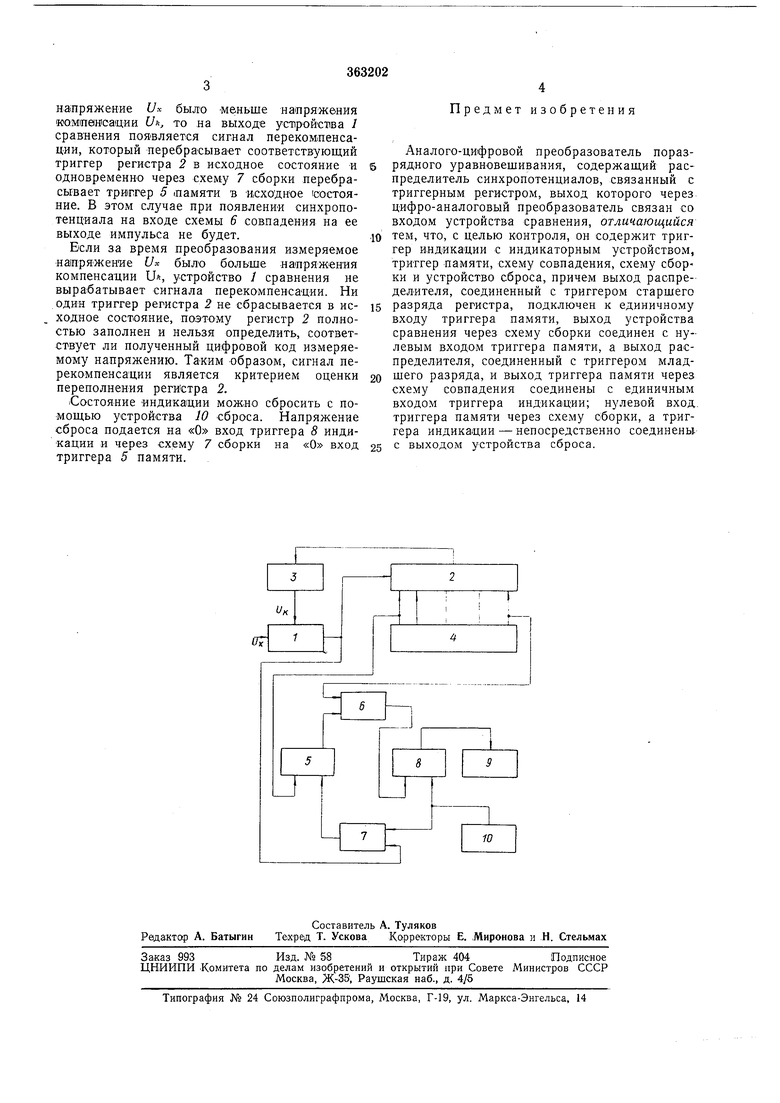

Изобретение относится к вычислительной технике и.может быть использовано для преобразования напряжения в цифровой код. Известные аналого-цифровые преобразователи поразрядного уравновешивания, содер.жащие распределитель синхропотенциалов, связанный с триггерным регистром, выход которого через цифро-аналоговый преобразователь связан со входом устройства сравнения, .не обеспечивают контроль. В предлагаемом аналого-цифровом преобразователе обеспечение контроля достигается тем , что он содержит триггер индикации с ин.дикаторным устройством, триггер памяти, схему совпадения, схему .сборки и устройство сброса, причем выход распределителя, соединенный с триггером старшего разряда регистра, подключен к единичному входу триггера памяти, выход устройства сравнения через схему сборки соединен с нулевым входом триггера памяти, а выход распределителя, соединенный с триггером младшего разряда, и выход триггера памяти через схему сборки соединены с единичным входом триггера ин.дикации; нулевой вход триггера памяти через схему сборки, а триггера индикации - непох;редственно соединены с выходом устройства -Сброса. На чертеже представлена блок-схема предлагаемого аналого-цифрового преобразователя. Аналого-цифровой преобразователь содержит устройство / сравнения; триггерный регистр 2; цифро-аналоговый преобразователь 5; распределитель 4 синхропотенциалов; триггер 5 памяти; схему 6 совпадения; схему 7 сборки; триггер 8 индикации; индикаторное устройство 9; устройство 10 сброса. Первый синхропотенциал с распределителя 4 переводит триггер старшего разряда регистра 2 из состояния «О в состояние «1 и одновременно - триггер 5 памяти из состояния «О в состояние «1. Выход триггера 5 памяти соединен со входом схемы 6 совпадения. Л -синхропотенциал переводит триггер младшего разряда регистра 2 из состояния «О в состояние «1 и одновременно поступает на другой вход схемы 6 совпадения. При совпадении импульсов с выхода распределителя и с выхода триггера 5 памяти на выходе схемы 6 совпадения появляется кратковременный импульс, который перебрасывает триггер 8 индикацин из состояния «О в состояние «1 и фиксирует .кратидавременяое совпадение импульсов на входе схемы 6 совпадения н; практически любой промежуток времени. Эт1 состояние триггера 8 индикации сигнализи руется индикаторным устройством 9. ЕслИ за время преобразования измеряемо

напряжение И было меньше напряжения 1ио:М1пен1са1Ции Uk, то на выходе успройства / сравнения появляется сигнал перекомленсации, который перебрасывает соответствующий триггер регистра 2 в исходное состояние и одновременно через схему 7 сборки перебрасывает триггер 5 (Памяти в исходное юостояние. В этом случае при появлении синхропотенциала на входе схемы 6 совпадения на ее выходе импульса не будет.

Если за время преобразования измеряемое напряжение было больше напряжения компенсации U, устройство / сравнения не вырабатывает сигнала перекомпенсации. Ни один триггер регистра 2 не сбрасывается в исходное состояние, поэтому регистр 2 полностью заполнен и нельзя определить, соответствует ли полученный цифровой код измеряемому напряжению. Таким образом, сигнал перекомпенсации является критерием оценки переполнения регистра 2.

-Состояние «ндикащии можно сбросить с помощью устройства 10 сброса. Напряжение сброса подается на «О вход триггера 8 индикации и через схему 7 сборки на «О вход триггера 5 памяти.

4 Предмет изобретения

Аналого-цифровой преобразователь поразрядного уравновешивания, содержащий распределитель сиихропотенциалов, связанный с триггерным регистром, выход которого через цифро-аналоговый преобразователь связан со входом устройства сравнения, отличающийся тем, что, с целью контроля, он содержит триггер индикации с индикаторным устройством, триггер памяти, схему совпадения, схему сборки и устройство сброса, причем выход распределителя, соединенный с триггером старшего разряда регистра, подключен к единичному входу триггера памяти, выход устройства сравнения через схему сборки соединен с нулевым входом триггера памяти, а выход распределителя, соединенный с триггером младшего разряда, и выход триггера памяти через схему совпадения соединены с единичным входом триггера индикации; нулевой вход, триггера памяти через схему сборки, а триггера индикации - непосредственно соединены с выходом устройства сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU809553A1 |

| Преобразователь напряжения в двоичный код | 1972 |

|

SU482005A1 |

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1969 |

|

SU256858A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД | 1972 |

|

SU340078A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО | 1971 |

|

SU293297A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| УСТРОЙСТВО для УСРЕДНЕНИЯ ВЫЗВАННЫХ ОТКЛИКОВ!,:k.-. | 1973 |

|

SU361461A1 |

| ДВУХКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1967 |

|

SU191233A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГОНАПРЯЖЕНИЯ | 1966 |

|

SU188587A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1969 |

|

SU243281A1 |

Авторы

Даты

1973-01-01—Публикация