Изобретение относится IK электроино-из/ме.рительной технике и предназначено для пересчета импульсов с иидикадией состояний устройства и может быть ислользовано, например, в электронно-счетных частотомерах.

Известны пе.ресчетные устройства оовыШ€1Н1Н-0(Го быстродействия. Все они имеют oi6щий тризнак - ловыш-ение частоты пересчета достигается лосредствОМ многократного деления частоты двОИчньши ячейка-ми, не охваченны.ми обратными связями, с последующим восстановлением коэффициента деления на 10.

Такие устройст1ва н-е 0|5е|Спечи1вают индикацию в режИме непрерывного счета. Это вызвано тем, что лишь при наличии импульса переноса, поступающего по окончании времени счета на дещиф|ратор, устройство функционирует как десятичное иересчетное. Режим непрерывного счета характеризуется отсутствием импульсов переноса, так как этот режим реализуется |без воздействия устрой-ств автомагики (схем переноса, т. е. при отсутствии каких-либо времен 1счета, и соответствует, например, подаче на .вход устройства бесконечной во времени прои3|воль ной последовательности импульсов.

Для (Нормального функционирования устройства |Необходи1мо использование дополнительных устройств - схем переноса.

Реализация десятичного пер€счет1ного у стройства невозможна при , т. е. деление входной частоты может осуществляться не более, чем тремя последо1ватель:но соединенными двоичными ячейками.

Цель изобретения-создание устройства повышенного быстродействия, позволяющего реализовать десятичный пересчет при любо.м количестше последо1вательна соединенных

двоичных ячеек на входе, а также обеспечить индикацию состояний устройства в режиме непрерывного 1счета.

Это достигается тем, что выходы делителя с 1коэ ф фициенто1м деления 2 подключены к

входам соответствующих делителей с коэффициентом деления 5 и к схемам «Запрет, соединенньгм запрещающими входа1ми с соответствующими ячейками делителей на 5, а выходами- со входами схемы «ИЛИ, сипнальный выход которой, а также лотенциальный выход дешифратора, к которому подключены выходы делителей, являются выходаМИ устройства. Это дает воэможность существенно снизить

частоту до ее поступления на делители с обратными связями - делителя с коэффициентом деления 5 и обеспечить, таким 0|бразом, реализацию десятичного пересчета при произвольно:М количестве последовательно соедиже обеспечить режил «епрерывн.о-го счета выделением .в ,дешифрато,ре данного разряда (потеициа лыных уровней, соот1ветст,вуюЩ:Их поступлеиию 1на вход устройства числа импульсов более десяти и устанавливалощих соответствие .между ЧИ1СЛ01М импульсов, записанным в устройстве, числом, |предста1вле1нным в д-ешифрато,ре IB десятичной системе счислвния, и .ИАшульса ми, присутствующими «а выходе устройства.

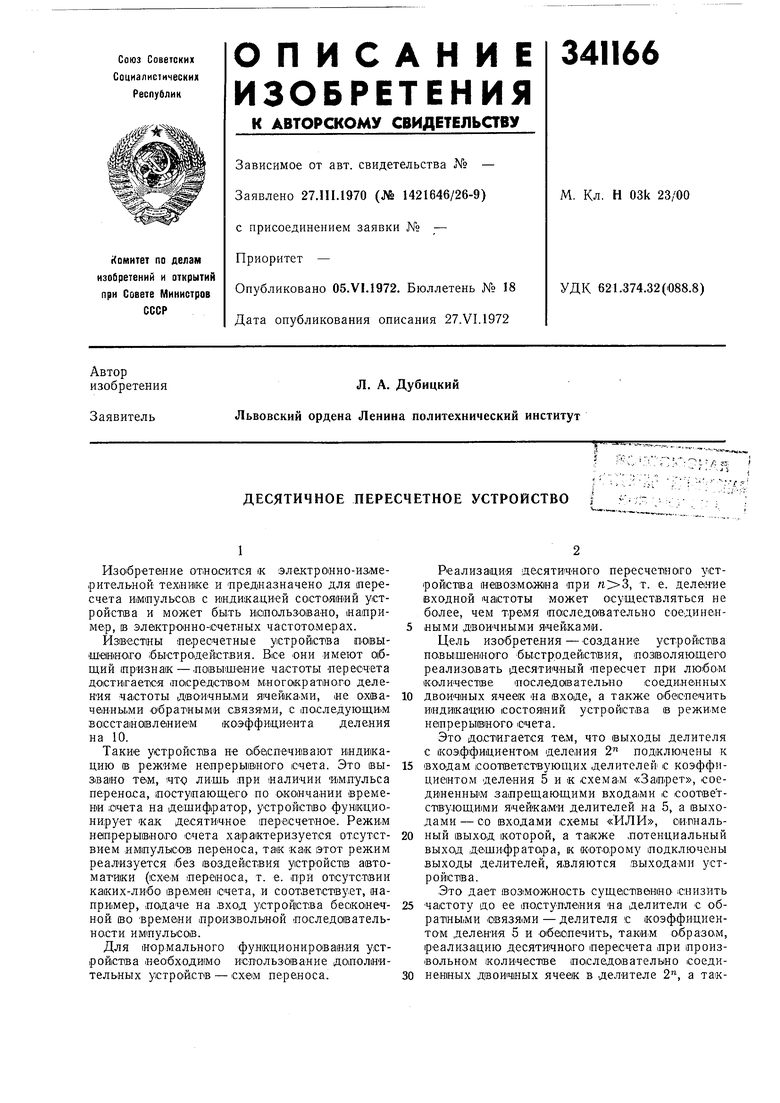

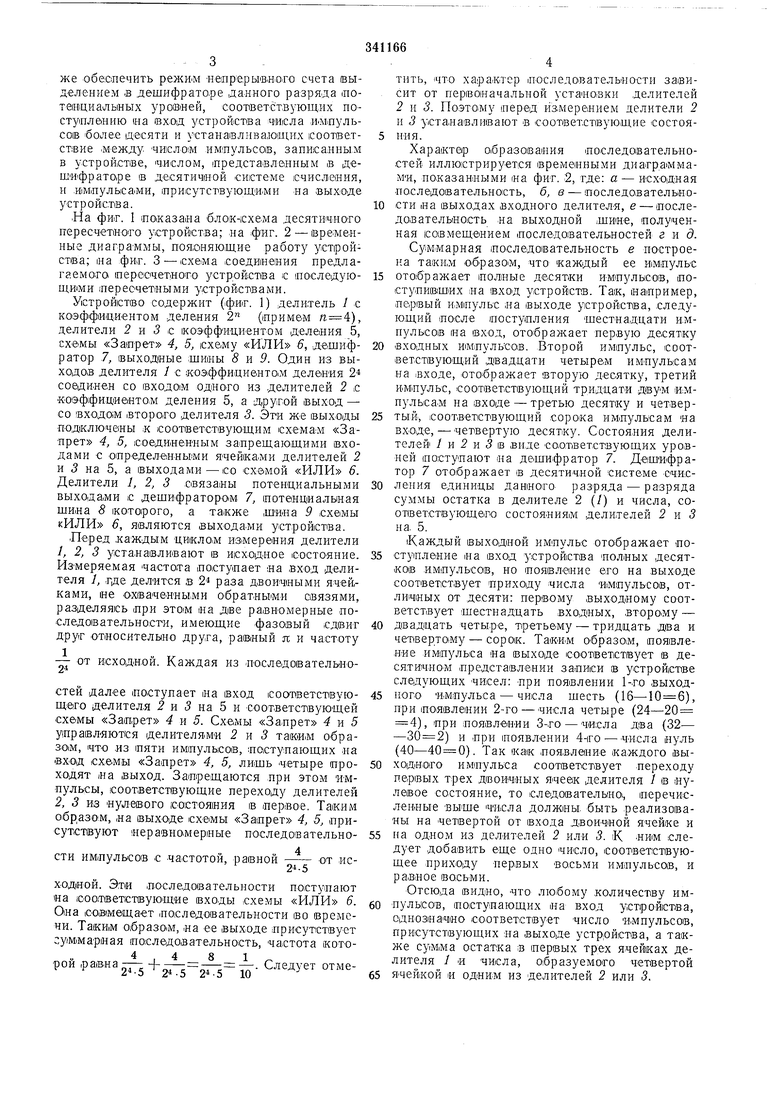

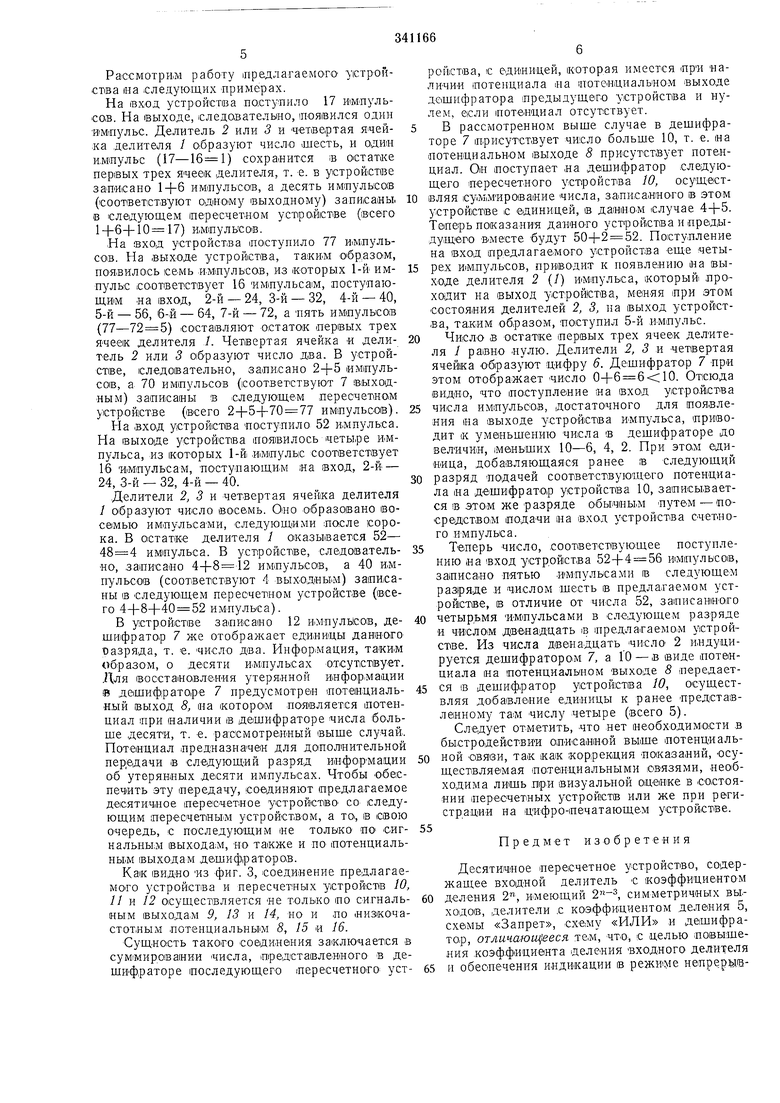

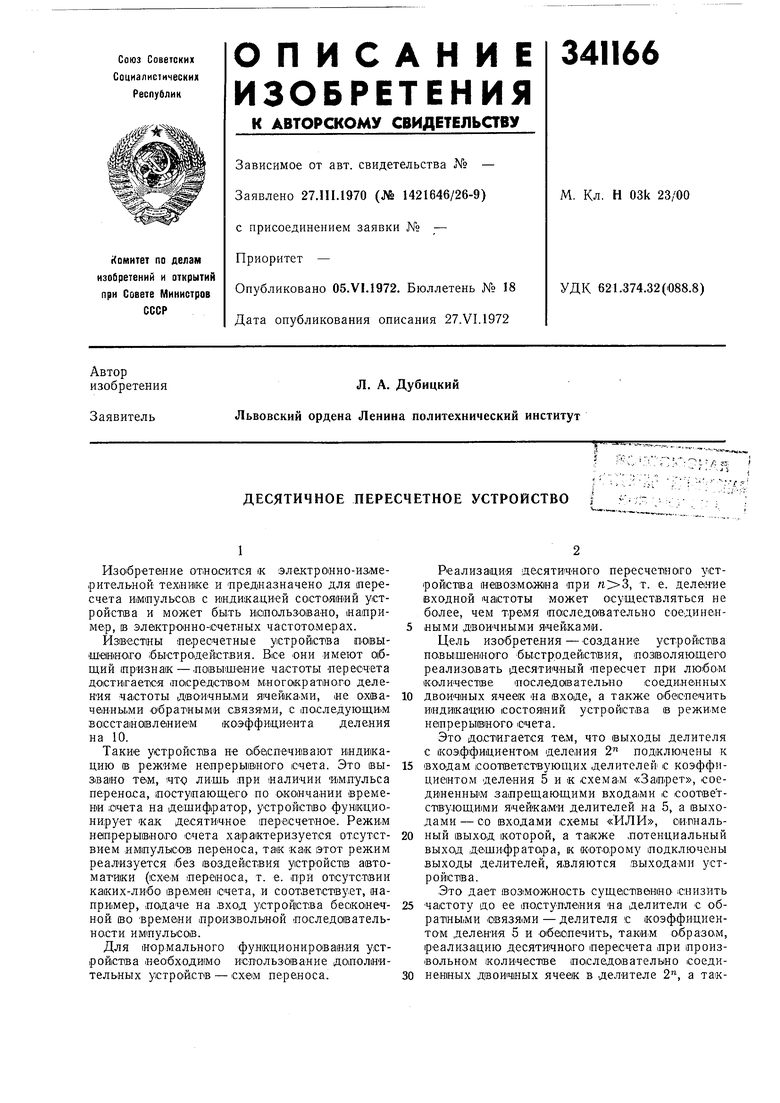

На фиг. 1 токазаиа блокнсхе ма десятичного ггересчетиого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства; 1на . 3--схема соедииеиия предлагаемого юересчетного устройства с последующими юереочетными устройствами.

Устройство содержит (фиг. 1) делитель 1 с коэффициентом деления 2 (примем ), делители 2 и 5 с коэффициентом деления 5, схемы «Запрет 4, 5, схему «ИЛИ 5, дешифратор 7, выходные шины S и 5. Один из выходов делителя / с коэффидиенто м деления 2 соединен со входом одного из делителей 2 с коэффициентов деления 5, а другой выход - со входо;м второго делителя 3. Эти же выходы подключены к соответствующим схема:м «Запрет 4, 5, соединенным запрещающими входами с определенными ячейка ми делителей 2 и 5 на 5, а выходами-со схемой «ИЛИ 6. Делители 1, 2, 3 связаны потенциальными выходами с дещифратором 7, потенциальная щина 8 которого, а также ,ШИ«а 9 схемы кИЛИ 6, являются выхода-ми устройства.

Перед .каждым циклом измерения делители 1, 2, 3 уста.навливают в исход.ное с-остояние. Измеряемая частота поступает на вход делителя 1, где делится ,в 2 раза двоичными ячейками, ее .ахваче.нньши обратными связями, разделяясь при это1М на две равномерные последовательности, имеющие фазовый сдвиг друг относительно друга, равный я и частоту

ОТ исходной. Каждая из .последовательно2

стей далее поступает на вход соответствующего делител.я 2 и 5 на 5 и Соответствующей схемы «Зап,рет 4 и 5. Схемы «За.прет 4 и 5 управляются д;елителями 2 и 5 такИ|М о.бра3.0iM, что .из пяти импульсов, поступающих на ВХОД схемы «Запрет 4, 5, лишь четыре проходят на выход. Запрещаются .при этом импульсы, соотв-етствующие переходу делителей 2, 3 из нулевого (состояния в первое. Таким Образом, на выходе схемы «Запрет 4, 5, присутствуют нера1Вно.мерные последовательности имлульсов с .частотой, равной

.ОТ

ходной. Эти по.сле.довательиости поступают на соответствующие вхо.ды схемы «ИЛИ 6. Она совмещает последовательности во времени. Таким oi6pa30iM, на ее выходе присутствует суммарная последовательность, частота которой -+. Следует отметить, ЧТО характер атоследовательиости зависит от первоначальной уста новки делителей 2 и 3. Поэто.му перед из.мерением делители 2 и Л устанавливают в соответствую.щие состояни я.

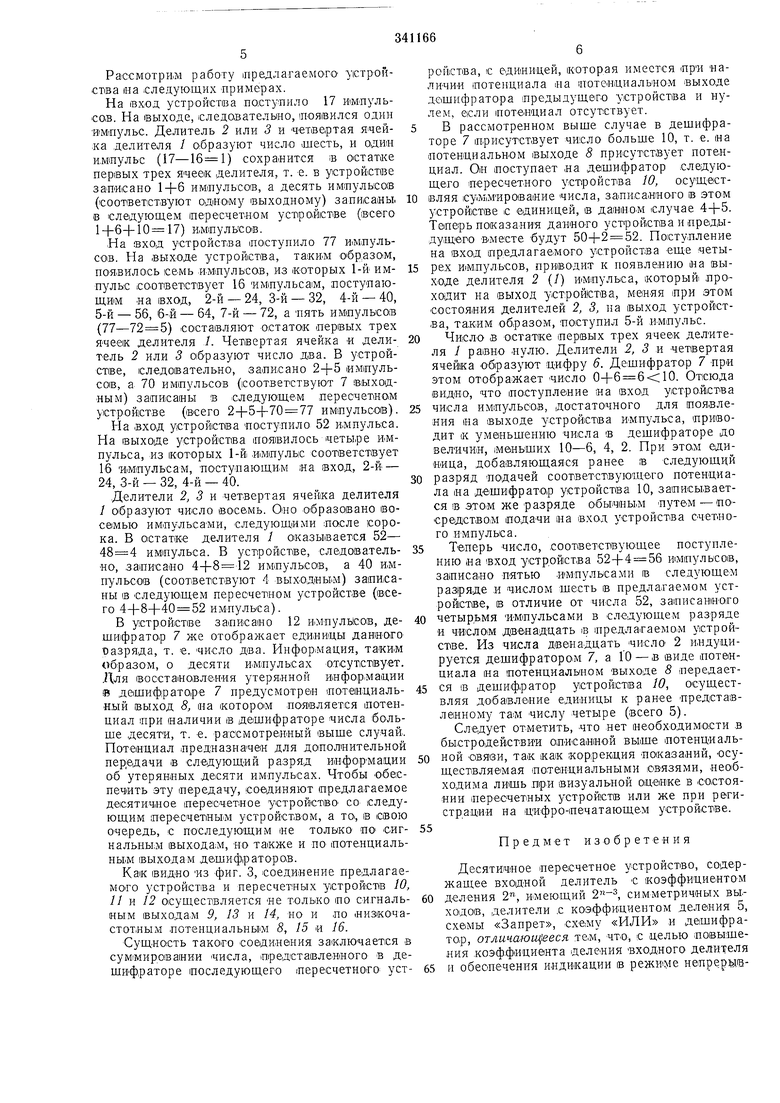

Характер 0|бразования последовательностей иллюстрируется временными диаграммами, по.казанными на фиг. 2, где: а - исходная .последовательность, б, в - последовательности на выходах входного делите.ЛЯ, е - последовательность на выходной шине, полученная совмещением последовательностей г и д. Суммарная последовательность е построена таким .образом, что каждый ее илшульс

отображает полные десятки импульсов, поступивШИх на вхОД устройств. Так, например, лервый импульс на выходе устройства, .следующий после поступления шестнадцати и.мпульсов на вход, отображает первую десятку

входных импульсов. Второй импульс, соответствуЮЩ.ий .двадцати четырем импульсам на входе, .отображает вторую десятку, третий ИМ1иульс, соответствующий тридцати двум И:Мпульса.м на входе - третью десятку и четвертый, соответствующий сорока импульсам на входе,-четвертую десятку. Состояния делителей / и 2 и 5 в виде соответствующих уровней поступают на дешифратор 7. ДешИфратор 7 отображает в десяти.чной систе.ме Счисления единицы данного разряда-разряда суммы остатка в делителе 2 (/) и числа, соответствующего состоя.ниям делителей 2 и 5 на. 5. |Каждый выходной импульс отображает посту1иле1ние на вход устройства полных десятков импульсов, но появл.е1ние его на выходе соответствует приходу числа импульсов, отличных от десяти: первому выходному соответствует ше.стнадцать входных, второму -

двадцать четыре, третьему - тридцать два и четвертому - сорок. Таким образом, появление импульса на выходе соответствует в десятичном представлении записи в устройстве следующих чисел: .при появлении 1-.го выходиого импульса - числа щесть (16-10 6), при появлении 2-го - числа четыре (24-20 4), при появл.ен.ии 3-.го - числа два (32- ) и .при появлении 4-го-ч.исла нуль (40-40 0). Так как появление каждого выходного импульса соответствует переходу первых трех двоичных ячеек делителя ) в нулевое состояние, то следовательно, перечислевные ВЫще числа должны, быть .реализованы на четвертой от входа двоичной ячейке и

на одном из делителей 2 или 5. iK .ним следует .добавить еще одно число, соотв.етствующее приходу первых восьми им1пульсов, и равное восьми.

Отсюда видно, что лЮбому количеству импульсов, поступающих на вход устройства, одиозначно соответствует число и.мпульсов, присутствующих на выходе устройства, а также суМ|Ма остатка в первых трех ячейках делителя / и числа, образуемого четвертой Рассмотрим работу тредлагаемОГО устройства 1на следующих примерах. На вход устройства поступило 17 и шульсов. На выходе, следовательно, появился один импульс. Делитель 2 или 3 и ч-етвертая ячейка делителя / 0 бразуют число шесть, и один импульс (17-16 1) сохранится в остатке первых трех ячеек делителя, т. е. в устройстве записано 1+6 импульсов, а десять импульсов (соответствуют одному выходному) записаны, е следующем пересчет-ном устройстве (всего 1+6+10 17) импульсов. На вход устройства поступило 77 импульсов. На выходе устройства, таким oi6p,a30iM, появилось се.мь импульсов, из которых 1-й импульс соответствует 16 импульса1М, поступающим на вход, 2-й - 24, 3-й - 32, 4-й - 40, 5-й - 56, 6-й - 64, 7-й - 72, а пять имоульсов (77-72 5) составляют остаток первых трех ячеек делителя 1. Четвертая ячейка и делитель 2 или 3 образуют число два. В устройстве, следовательно, записано 2+5 импульсов, а 70 импульсов (соответствуют 7 выходным) записаны в 1следующем пересчетном устройстве (всего 2+5+-70 77 импульсов). На вход устройства поступило 52 импульса. На выходе устройства появилось четыре импульса, из которых 1-й импульс соответствует 16 импульсам, поступающим на вход, 2-й- 24, 3-й - 32, 4-й - 40. Делители 2, 3 н четвертая ячейка делителя 1 образуют число восемь. Оно образовано восемью импульса-ми, следующими после сорока. В остатке делителя 1 оказывается 52- импульса. В устройстве, следователь«о, записано импульсов, а 40 импульсов (соответствуют 4 выходным) записаны в следующем пересчетиом устройстве (всего 4+8+40 52 импульса). В устройстве записано 12 импулысов, дешифратор 7 же отображает единицы данного Разряда, т. е. число два. Ннфор-мация, таким образом, о десяти импульсах отсутствует. .Для восстанавлеНИя утерянной информации IB дешифраторе 7 предусмотрен потанциальН.ЫЙ выход 8, на «OTOpoiM появляется лотенциал при наличии в дешифраторе числа больще десяти, т. е. рассмотренный выще случай.. Потенциал предназначен для дополнительной информации передачи в следующий разряд об утерянных десяти импульсах. Чтобы обеспечить эту передачу, соединяют предлагаемое десятичное пересчетное устройство со следующим пересчетным устройством, а то., в свою очередь, с последующим не только по сигнальным 1Выхода М, но также и по потенциальным выходам дешифраторов. Как видно ИЗ фиг. 3, соединение предлагаемого устройства и пересчетных устройств 10, 11 и 12 осуществляется не только по сигнальным выхода.м 9, 13 и 14, но и по низкочастотным потенциальным 8, 15 и 16. Сущность такого соединения заключается в сум(мировании числа, представленного в де роиства, с единицей, которая имеется при иаличии потенциала па потепциальном выходе дешифратора предыдущего устройства и нулем, если потенциал отсутствует. В рассмотренном выше случае в дешифраторе 7 присутствует число больше 10, т. е. на потенциальном выходе 8 присутствует потенциал. OiH поступает на дешифратор следующего пересчетного устройства 10, осуществляя сульмироваиие числа, записанного в этом устройстве с единицей, в даино-м случае . Теперь показания даннОГо устройства и предыдущего B iecTB будут 50+2 52. Поступление на вход предлагаемого устройства еще четырех импульсов, приводит к появлению на выходе делителя 2 (1) импульса, который прохо|дит на выход устройютва, меняя при этом состояния делителей 2, 3, на выход устройства, таким образом, поступил 5-й .и.мпульс. Число в О статке первых трех ячеек делителя 1 равно нулю. Делители 2, 3 и четвертая ячейка образуют цифру 6. Дешифратор 7 при этом отобра:жает число . Отсюда видно, что поступление иа вход устройства числа импульсов, достаточного для появления на выходе устройства импульса, приводит к уменьшению числа в дешифраторе до величин, меньших 10-6, 4, 2. При единица, добавляющая1ся ранее IB следующий разряд подачей соответствующего потенциала на дешифратор устройства 10, записывается в этом же разряде обычным путем -(посредствол подачи на вход устройства счетного импульса. Теперь число, соответствующее поступлению на вход устройства импульсов, записано пятью импульсами в следующем разряде и числом шесть в предлагаемом устройстве, в отличие от числа 52, записанного четырьмя импульсами в следующем разряде и числом двенадцать в предлагаемо устройстве. Из числа двенадцать число 2 индуцируется дешифратором 7, а ГО - в виде потенциала на потенциальном выходе 8 передается IB дешифратор устройства 10, осуществляя добавление единицы к ранее представленному там числу четыре (всего 5). Следует отметить, что нет необход импост и в быстродействии опи санной выще потенциальной свяеи, так как коррекция показаний, осуществляемая потенциальными связями, необходима лишь при визуальной оценке в состоянии пересчетных устройств или же при регистрации на цифро-печатающем устройстве. Предмет изобретения Десятичное пересчетное устройство, содержащее входной делитель с коэффициентом деления 2, имеющий 2, симметричных выходов, делители с коэффициентом деления 5, схемы «Запрет, схему «НЛИ и дешифратор, отличающееся тем, что, с целью повышения коэффициента деления входного делителя

ного счета, выходы входнюто делителя подключены 1К входам соответствующих делителей 1C 1КОэ.ф|фициентом деления 5 и к схемам «Залрет, соединениым затрещающими входа1ми с выходами делителей с коэффициентом

делания 5, а выходы схем «Залрет, лодключены к входам схемы «ИЛИ, выходы всех делителей лодключелы к входам дешифратора., выход которого совместно свыходом схемы «ИЛИ являются выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341165A1 |

| ВИБЛИОТЕКД J | 1971 |

|

SU299030A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU241127A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU233308A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Делитель последовательности импульсов (его варианты) | 1982 |

|

SU1051730A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНО-ШЕСТИДЕСЯТИРИЧНЫЙ КОД | 1967 |

|

SU190054A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1977 |

|

SU684744A1 |

Г

ь

5 д

Т Т

I I

fill

I f

тт

i/. с

Даты

1972-01-01—Публикация