Предложенное устройство относится к электронно-измерительной технике. Оно предназначено для деления частоты, пересчета имлульсов с индикацией состояний и может быть использовано в электронно-счетных частотомерах.

Известны скоростные пересчетные устройства, работающие .по принципу двойного преобразования входного сигнала.

Известное устройство содержит делитель с коэффициентом деления 2 , вход которого соединен с выходом селектора счета частотомера, а выход подключен :ко входу делителя с Коэффициентом деления 10. Выход последнего подключен ко входу умножителя импульсов в 2 раз. Выход умножителя соединен со входом последующих декад частотомера. Кроме того, устройство содержит считывающую систему, управляемую датчиком калиброванных отрезков времени Р декад с быстродействием на несколько порядков ниже входной частоты и выходной ключ.

Однако применение метода двойного преобразования в описанном устройстве обусловило громоздкость конструкции, сложность считывающей системы и необходимость введения двух умножителей импульсов, что не могло не сказаться на надежности работы устройства и трудоемкости его регулировки.

три выхода делителя с коэффициентом деления 2з соединены со входами схемы «ИЛИ, другой выход этого делителя подключен ко входам делителя с коэффициентом деления 5

и схемы «Запрет, запрещающий вход которой соединен с соответствующей ячейкой делителя с коэффициентом деления 5, а выход подключен ко входу схемы «ИЛИ. Выход последней связан со входом делителя с коэффициентом деления 2, выход которого, а также выходы делителей с коэффициентом деления 2з и коэффициентом деления 5 подключены к соответствующим входам дешифратора. Сущность предлагаемого изобретения заключается в том, что для увеличения быстродействия измерения частота претерпевает деление в 2з раз при прохождении через двоичные ячейки, не охваченные обратной связью, расщепляясь при этом на четыре периодические последовательности импульсов, имеющие фазовый сдвиг одна относительно другой, равный - , и частоту от исходной. Далее

22

одна из последовательностей преобразовывается до частоты, равной от исходJ Л1

ной, что достигается селектированием каждого пятого имлульса и является возможным, так как преобразовывается частота, в 2з раз ниже исходной, и суммируется с остальными

тремя, воспроизводя непериодическую после„ 1 . , 1 --,- довательность с частотой, равной -,+

1 1116„тт

-t- - + g 23 4о ° исходной. Деление

последней в 22 раз двоичными ячейками, не охваченными обратными связями, преобразует суммарную непериодическую последовательность в периодическую с частотой, равной

161„

. - от исходной, обеспечивая

таким образом коэффициент деления данного пересчетного устройства на 10.

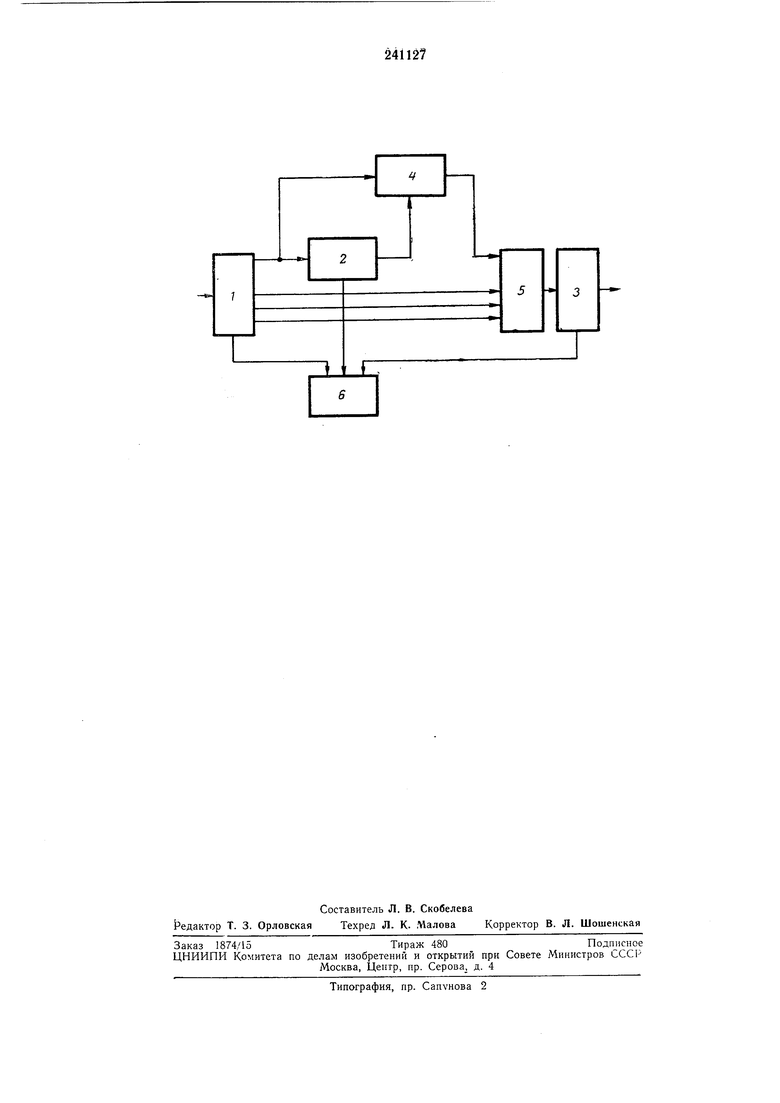

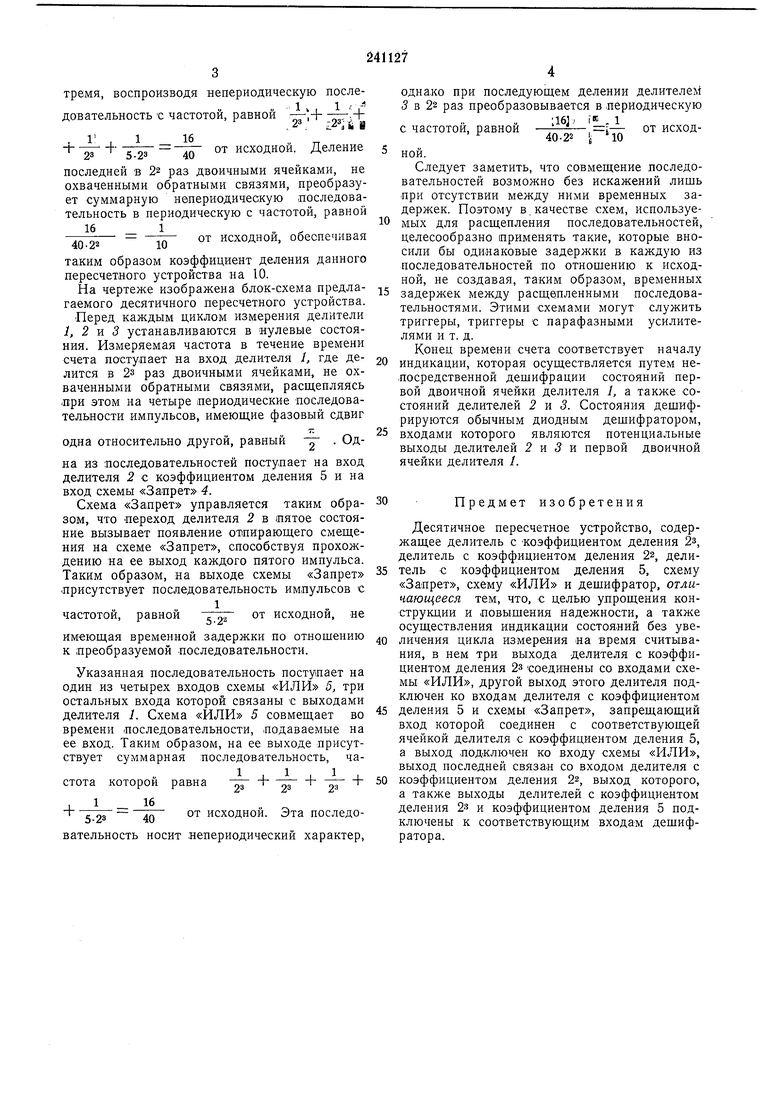

На чертеже изображена блок-схема предлагаемого десятичного пересчетного устройства.

Перед каждым циклом измерения делители 1, 2 и 3 устанавливаются в нулевые состояния. Измеряемая частота в течение времени счета поступает на вход делителя 1, где делится в 2з раз двоичными ячейками, не охваченными обратными связями, расщепляясь .при этом на четыре периодические последовательности импульсов, имеющие фазовый сдвиг

г.

одна относительно другой, равный - . Одна из последовательностей поступает на вход делителя 2 с коэффициентом деления 5 и на вход схемы «Запрет 4.

Схема «Запрет управляется таким образом, что переход делителя 2 в лятое состояние вызывает появление отпирающего смещения на схеме «Запрет, способствуя прохождению на ее выход каждого пятого импульса. Таким образом, на выходе схемы «Запрет присутствует последовательность импульсов с

1 частотой, равной 7 исходной, не

имеющая временной задержки по отношению к преобразуемой последовательности.

Указанная последовательность поступает на один из четырех входов схемы «ИЛИ 5, три остальных входа которой связаны -с выходами делителя 1. Схема «ИЛИ 5 совмещает во времени последовательности, подаваемые на ее вход. Таким образом, на ее выходе присутствует суммарная последовательность, ча1,1,1, стота которой равна - + --г -г

, 1 16„

Г „3 - 40 ИСХОДНОЙ. Эта последовательность носит непериодический характер.

одна.ко при последующем делении делителем 3 в 22 раз преобразовывается в периодическую

от исходс частотой, равной

10

40-22

li ч л

НОИ.

Следует заметить, что совмещение последовательностей возможно без искажений лишь при отсутствии между ними временных задержек. Поэтому в.качестве схем, используемых для расщепления последовательностей, целесообразно применять такие, которые вносили бы одинаковые задержки в каждую из последовательностей по отношению к исходной, не создавая, таким образом, временных

задержек между расщепленными последовательностями. Этими схемами могут служить триггеры, триггеры с парафазными усилителями и т. д. Конец времени счета соответствует началу

индикации, которая осуществляется путем непосредственной дешифрации состояний первой двоичной ячейки делителя 1, а также состояний делителей 2 и 3. Состояния дешифрируются обычным диодным дешифратором,

входами которого являются потенциальные выходы делителей 2 и 5 и первой двоичной ячейки делителя /.

Предмет изобретения

Десятичное пересчетное устройство, содержащее делитель с коэффициентом деления 2з, делитель с коэффициентом деления 22, делитель -с коэффициентом деления 5, схему «Запрет, схему «ИЛИ и дешифратор, отличающееся тем, что, с целью упрощения конструкции и повышения надежности, а также осуществления индикации состояний без увеличения цикла измерения на время считывания, в нем три выхода делителя с коэффициентом деления 2з соединены со входами схемы «ИЛИ, другой выход этого делителя подключен ко входам делителя с коэффициентом

деления 5 и схемы «Запрет, запрещающий вход которой соединен с соответствующей ячейкой делителя с коэффициентом деления 5, а выход подключен ко входу схемы «ИЛИ, выход последней связан со входом делителя с

коэффициентом деления 2, выход которого, а также выходы делителей с коэффициентом деления 2з и коэффициентом деления 5 подключены к соответствующим входам дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВИБЛИОТЕКД J | 1971 |

|

SU299030A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341165A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341166A1 |

| ВСЕСОЮЗНАЯ | 1973 |

|

SU370702A1 |

| Устройство для измерения числа сбоев делителей частоты | 1973 |

|

SU473960A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU233308A1 |

| Функциональный генератор частоты | 1978 |

|

SU758490A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU330542A1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU364944A1 |

Даты

1969-01-01—Публикация