Изобретение относится к электронно-измерительной технике и предназначено для деления частоты, пересчета импульсов с непосредственной индикацией состояния устройства и, в частности, молсет быть использовано в электронно-счетных частотомерах.

Известны различные десятичные пересчетные устройства. Наибольшее распространение получили нересчетные устройства, выполненные на основе четырех двоичных ячеек, соединенных между собой последовательно, с внутренними обратными связями, обеспечивающими пересчет на десять. Скорость счета таких устройств ограничивается в основном наличием обратных связей и вследствие этого оказывается ниже быстродействия автономной двоичной ячейки.

Для создания нересчетного устройства, скорость счета которого ограничивается только быстродействием двоичной ячейки, был предложен принцип двойного преобразования входного сигнала, нозволяющий осуществлять пересчет без значительного увеличения цикла измерения и при наличии счетных декад, быстродействие которых может быть на несколько порядков ниже входной частоты.

подключен ко входу делителя с коэффициентом деления ЮР, выход которого соединен со входом умножителя импульсов в 2 раз. Выход умножителя соединен со входами последующих декад частотомера. Кроме того, устройство содержит считывающую систему, управляемую датчиком калиброванных отрезков времени, Р декад с быстродействием на несколько порядков ниже входной частоты и

выходной ключ. При использовании этого устройства входная частота в течение выбранного времени измерения, проходя через селектор счета, преобразуется с помощью двоично-десятичного делителя в частоту

где 2 и ЮР - коэффициенты деления последовательно соединенных двоичного и десятичного делителей. Преобразованная частота поступает на вход умножителя импульсов в 2 раз и претерпевает вторичное преобразо/мзм

С выхода умноживание до величины

10°

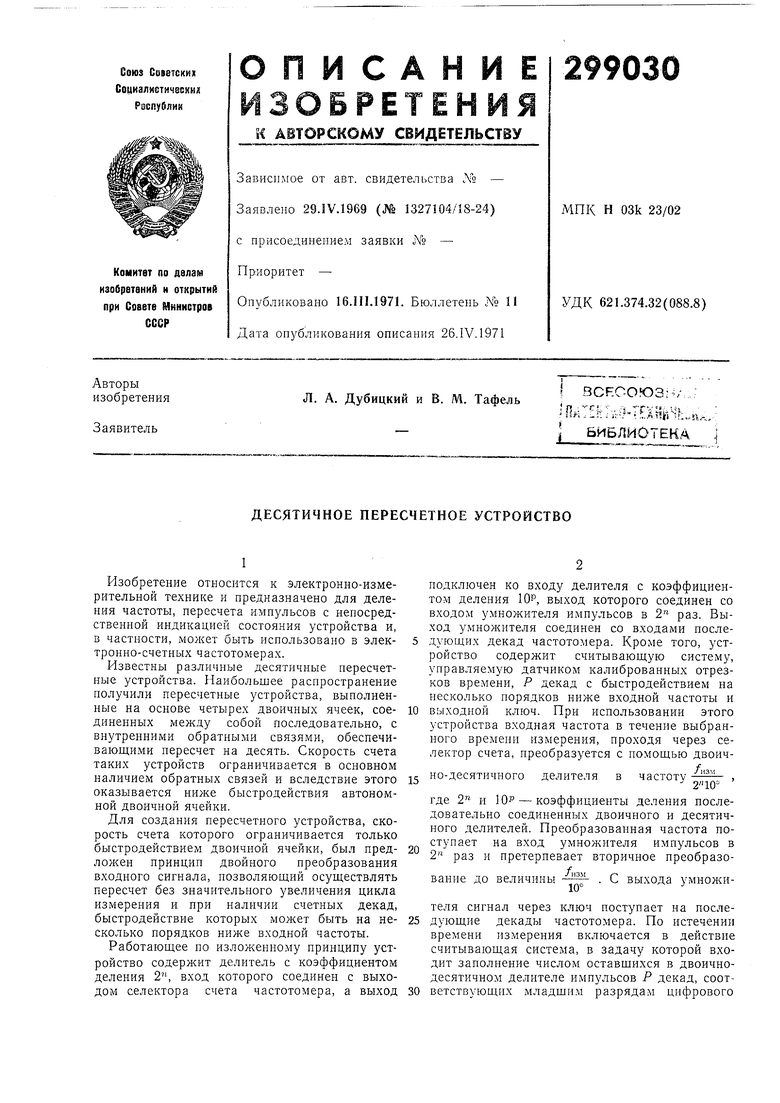

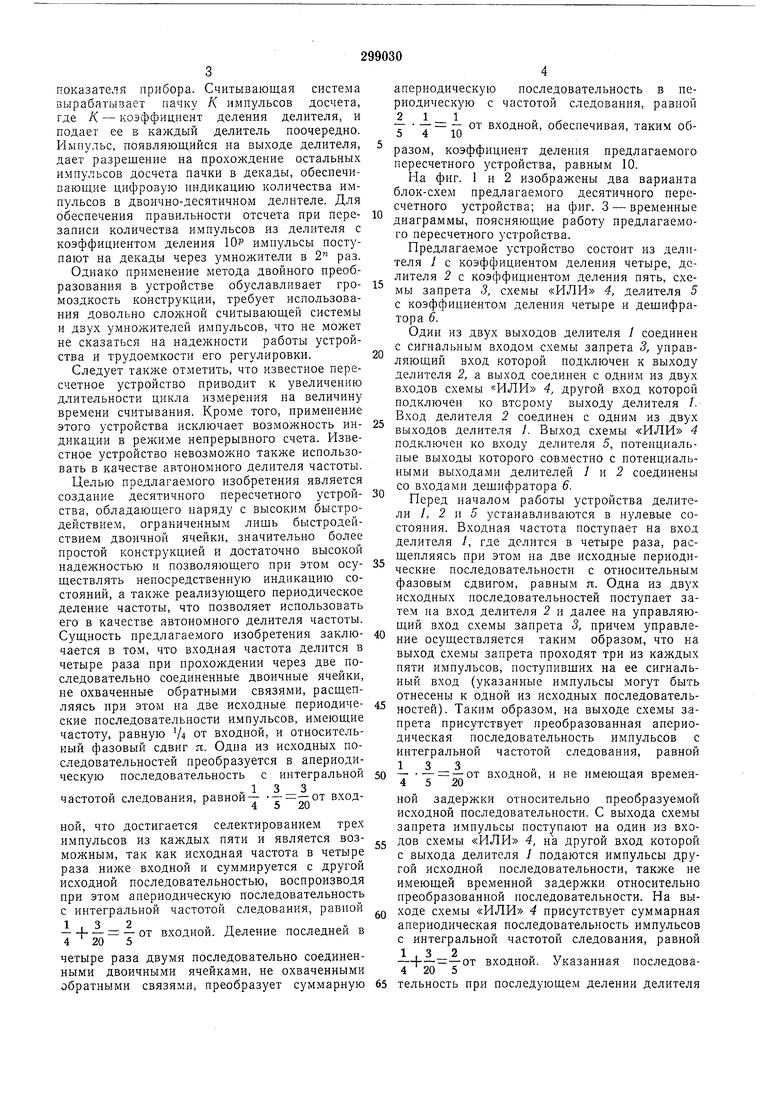

теля сигнал через ключ поступает па последующие декады частотомера. По истечении времени измерения включается в действие считывающая система, в задачу которой входит заполнение числом оставшихся в двоичнодесятичном делителе импульсов Р декад, соответствующих младши.м разрядам цифрового показателя прибора. Считывающая система вырабатывает пачку /С импульсов досчета, где К. - коэффициент деления делителя, и подает ее в каждый делитель поочередно. Импульс, появляющийся на выходе делителя, 5 дает разрешение на прохождение остальных импульсов досчета иачки в декады, обеспечивающие цифровую индикацию количества импульсов в двоично-десятичном делителе. Для обеспечения правильности отсчета при пере- ю записи количества импульсов из делителя с коэффициентом деления ЮР импульсы поступают на декады через умножители в 2 раз. Однако применение метода двойного преобразования в устройстве обуславливает гро- 15 моздкость конструкции, требует использования довольно сложной считывающей системы и двух умножителей импульсов, что не может не сказаться на надежности работы устройства и трудоемкости его регулировки. Следует также отметить, что известное пересчетное устройство приводит к увеличению длительности цикла измерения на величину времени считывания. Кроме того, иримеиение времени считывания, гчроме того, применение этого устройства исключает возможность ий- 25 дикации в режиме непрерывного счета. Известное устройство невозможно также использовать в качестве автономного делителя частоты. Целью предлагаемого изобретения является M uupt icnnM л«ллс1.л создание десятичного пересчетного устрой- и пересчетного устрой- 30 ства, обладающего наряду с высоким быстродействием, ограниченным лишь быстродеиствием двоичной , значительно болес простои конструкцией и достаточно высокой надежностью и позволяющего ири этом осу- 35 ществлять непосредственную индикацию состоянии, а также реализующего периодическое деление частоты, что позволяет использовать его в качестве автономного делителя частоты. Сущность предлагаемого изобретения заклю- 40 чается в том, что входная частота делится в четыре раза при прохождении через две последовательно соединенные двоичные ячейки, не охваченные обратными связями, расщепляясь ири этом на две исходные периодиче- 45 ские последовательности импульсов, имеющие частоту, равную Д от входной, и относительиый фазовый сдвиг я. Одна из исходных последовательностей преобразуется в апериодиинтегральной 50 ческую последовательность с о о частотой следования, равной- вход4 С) и ной, что достигается селектированием трех импульсов из каждых пяти и является возможным, так как исходная частота в четыре раза ниже входной и суммируется с другой исходной последовательностью, воспроизводя ири этом анер иодическую последовательность с интегральной частотой следования, равной 132 -I - от входной. Деление последней в 4 20 5 апериодическую последовательность в периодическую с частотой следования, равной 211„ . входной, обеспечивая, таким об5 4 iU разом, коэффициеит деления предлагаемого пересчетного устройства, равным 10. На фиг. 1 и 2 изображены два варианта блок-схем предлагаемого десятичного пересчетного устройства; на фиг. 3 - времениые диаграммы, поясняющие работу предлагаемого пересчетного устройства. Предлагаемое устройство состоит из делителя / с коэффициентом деления четыре, делителя 2 с коэффициентом деления пять, схемы Т схемьГ ИЛИ 1 д5 коэффициентом деления четыре и дешиф раОдин из двух выходов делителя / соединен с сигнальным входом схемы запрета 3, управляющий вход которой подключен к выходу делителя 2, а выход соединен с одним из двух входов схемы «ИЛИ 4, другой вход которой подключен ко второму выходу делителя /. делителя 2 соединен с одним из двух , делителя 1. Выход схемы «ИЛИ 4 подключен ко входу делителя 5, потенциальпые выходы которого совместно с потенциальными выходами делителей 1 2 соединены входами дешифратора 6. епет иячялпм пяботы vr началом работы устройства делите, /, 2 и 5 устанавливаются в нулевые состояния. Входная частота поступает на вход делителя /, где делится в четьфе раза, расщепляясь при этом на две исходные иериоди последовательности с относительным фазовым сдвигом, равным я. Одна из двух „сходных последовательностей поступает з,а делителя 2 и далее на управляю , уцравление осуществляется таким образом, что на , запрета проходят три из каждых „ импульсов, поступивших на ее сигналь -. (указанные импульсы могут быть отнесены к одной из исходных последовательностей). Таким образом, на выходе схемы за ирисутствует преобразованная апериоi г - г г iдическая последовательность импульсов с интегральной частотой следования, равной 133 -г - - ;;;;от входной, и не имеющая времен45 20 ной задержки относительно преобразуемой исходной последовательности. С выхода схемы запрета импульсы поступают на один из входов схемы «ИЛИ 4, на другой вход которой с выхода делителя / подаются импульсы другой исходной последовательности, также не имеющей временной задержки относительно преобразованной последовательности. На выходе схемы «ИЛИ 4 присутствует суммарная апериодическая последовательность импульсов с интегральной частотой следования, равной

о в четыре раза преооразуется в периодическую последовательность с частотой, равной

- - от входной. Индикация осущестО 4iU

вляется при помощи непосредственной дешифрации состояний делителей Л 2 и 5.

Следует отметить, что в зависимости от свойств двоичных ячеек, на которых собраны делители У, 2 и 5 (задержка, крутизна фронтов выходных сигналов), одна из двух блоксхем построения предлагаемого пересчетного устройства может оказаться более предпочтительной.

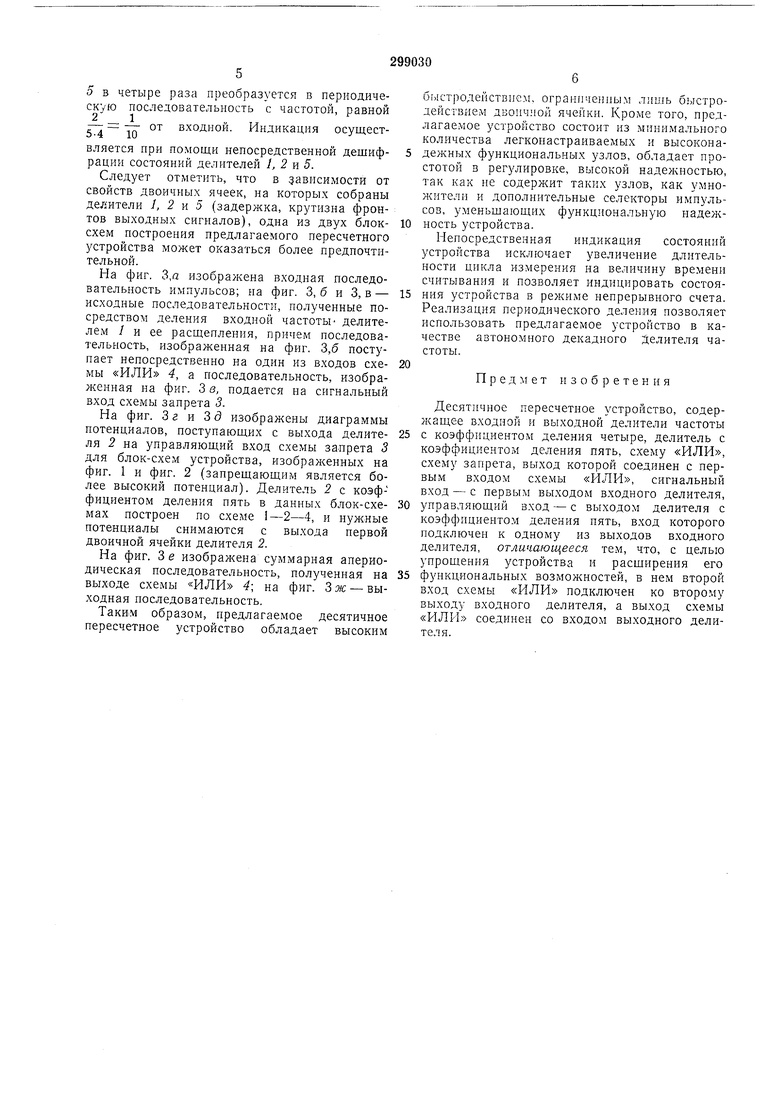

На фиг. 3,а изображена входная последовательность импульсов; на фиг. 3, б и 3, в - исходные последовательности, полученные посредством деления входной частоты делителем / и ее расщепления, причем последовательность, изображенная на фиг. 3,6 поступает непосредственно на один из входов схемы «ИЛИ 4, а последовательность, изображенная на фиг. 3 в, подается на сигнальный вход схемы запрета 3.

На фиг. Зг и 3d изображены диаграммы потенциалов, поступающих с выхода делителя 2 на управляющий вход схемы запрета 3 для блок-схем устройства, изобралсенных на фиг. 1 и фиг. 2 (запрещающим является более высокий потенциал). Делитель 2 с коэффициентом деления пять в данных блок-схемах построен по схеме 1-2-4, и нужные потенциалы снимаются с выхода цервой двоичной ячейки делителя 2.

На фиг. 3 е изображена суммарная апериодическая последовательность, полученная на выходе схемы «ИЛИ 4; на фиг. Зж - выходная последовательность.

Таким образом, предлагаемое десятичное пересчетное устройство обладает высоким

оыстродеиствиел, ограниченным лишь оыстродействием двоичной ячейки. Кроме того, предлагаемое устройство состоит из минимального количества легконастраиваемых и высоконадежных функциональных узлов, обладает простотой в регулировке, высокой надежностью, так как не содержит таких узлов, как умножители и дополнительные селекторы импульсов, уменьщающих функциональную надежность устройства.

Непосредственная индикация состояний устройства исключает увеличение длительности цикла измерения на величину времени считывания и позволяет индицировать состояния устройства в режиме непрерывного счета. Реализация периодического деления позволяет использовать предлагаемое устройство в качестве автономного декадного Делителя частоты.

Предмет изобретения

Десятичное пересчетное устройство, содержащее входной и выходной делители частоты

с коэффициентом деления четыре, делитель с коэффициентом деления пять, схему «ИЛИ, схему запрета, выход которой соединен с первым входом схемы «ИЛИ, сигнальный вход - с первым выходом входного делителя,

управляющий вход - с выходом делителя с коэффициентом деления пять, вход которого подключен к одному из выходов входного делителя, отличающееся тем, что, с целью упрощения устройства и расщирения его

функциональных возможностей, в нем второй вход схемы «ИЛИ подключен ко второму выходу входного делителя, а выход схемы «ИЛИ соединен со входом выходного делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU241127A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕСЧЕТА И РЕГИСТРАЦИИ КОЛИЧЕСТВА ИМПУЛЬСОВ | 1971 |

|

SU310400A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU233308A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341165A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1970 |

|

SU282423A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341166A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Цифровое устройство измерения времени | 1977 |

|

SU672606A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

Даты

1971-01-01—Публикация