Изобретеиие относнтся к области автоматики и вычислительной те.хникл.

Известен десятичный сумматор, выполне«НЫЙ на магнитных элементах с распределением тока, содержащий всномогательщый и накапл:и:вающ,ий регистры, обмотки залиси которых соединены но схе. преобразователя ДВОИЧНОГО код.а в десятичный.

Предложенный сумматор отличается те-м, что. в нем Обмотка распределения элемеита первото разряда вспомогательного регистра соединена с началом обмоток зани.сн регистра результата, обмотка распределения элемента rt-iro разряда .вспомогательного регистра связана с началом Обмоток залиси регистра .результата со сдвигом на л-1 разряд в сторону старших разрЯдов .причем в .целях формирования перено.са обмотки распределения вспомогательного регистра соединены с обмотками записи регистра результата действия через обмотки записи нере;1осов. Ко1ьиы обмоток заииси рег.чсгра результата подключены к началу обмоток р.аспре.деления иакапл)вающегО рсго;стра, и обмопки распределения регистра результата связаны с обмотками записи накапливающего регистра.

Это позвол.яет повысить быстродейств1 е сумматора.

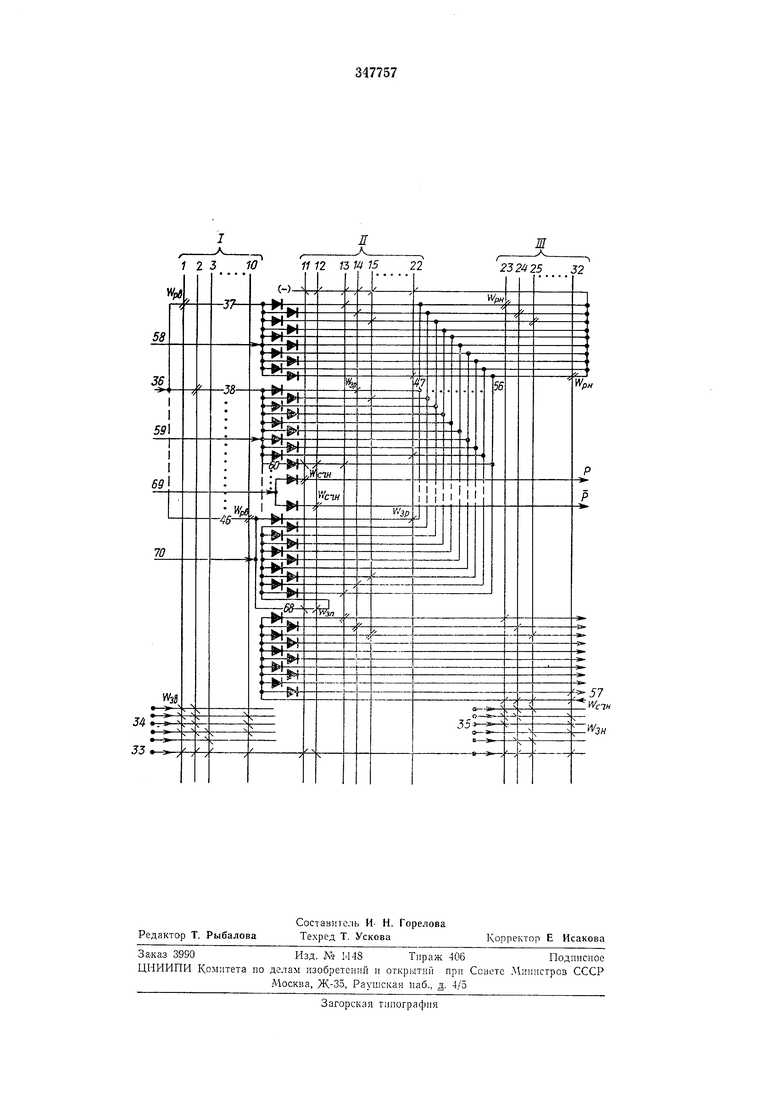

однородных матр.ипах, представляющих сооои всно.могательный регистр 1, регистр И результата действия и накаилпвающпй рег)1стр ГИ, собранный на м агнитных сердечни ках /, 2, 3,..., 10; ,..., 22; 23; 24, 25,..., 32.

Первоначально по входу 33 происходит иодготовка., а ио входам 34 и ,35 запись числа (на чертеже показана зались кода «2 и 5) -в вспомогательный и накапливающий регистры но обмоткаем и соответственно.

После запнси в регистры на вход 36 прихо.дит импульс сложения, который распростр|ан.яется но пеням распределен ия 37, 38,... 46 в з ависимост.и от содержимого вспомогательного регистра, производит запись результата но обмоткам F.,p в регистр результата действия и проходит в одну из пепей 47,..., 56 обмоток рахпределепагя W,,,, накапливающего periiCTpa в завиошости от его содержа 1ия. Причем сердечники / -10, 3-32 ир11меняемых регистров несут соответствен .ю информацию о ч)1слах О-9, я сердечнопки //, 12 хран.ят информацию о переносе ил.п его отсутствии.

Считывание информации с десятотного cyMiMaTopa Происход)гг по обмоткам W .имиульсом по входу 57, который переп)1сывает результат действия в накопительный .регистр. Следующим тактом по входу 55 гнформ.адпя

регенерируется в регистре результата действия гари отсутствии переноса в мл-адшем разряде лутем перезаписи инфорсмащии с навош- тельиого региктра ,в регистр результата действия, пли же raiKTOM по пходу 59 происходит уволичСИпо и:и|форма 11,ии iia одну единиЦу is регистре результата депствнш лри И1ал№пш переноса в младшем разряде.

Лри сложении дв1ух чисел, при которых возникает перенос, импульс операции по входу 36 распределяется в одну из цепей 60,... 68, проходя по обмоткам записИ переносов сердечников //, 12, записывает информацию о наличии .переноса, которая считывается следую(щим тактом по входу 69, причем импульс очитывани.я, прешедший по обмотке считы вания переносов .сердечника 11, характеризует наличие перено;са, а по Обмотке считывания переносов сердечиика /2-его отсутствие.

iB (Предложенном сумматоре осуществляется операция преобразования прямого кода в обратный. Эта оиерация реализуется подачей пары импульсов по входам 57 и 70, в результате чего происходит сначала передача содержимого регистра результата действия в н.а копительньш регистр и далее обратная передача инвеитированного значения в регистр результата действия.

Рассмотрим пример реализации суммы чисел 1 и 9, первое из которых после подготовки регистров ио входу 33 записывается ,по входам 34 во вспомогательный регистр I, второе но входам 35 - в накопительный регистр III.

iB результате записи «1 во вспомогательном регистре 1 сердеч.ииж 2 находится в сосТОЯИ1ИИ1 положительной индумции и его обмотка распределения представляет малое сопротивление для считывающего импульса. В анало Г11чном состоянии находится сердечник 32 накопительного регистра, тогда ток считывания с входа 36 распределяется пО цеи-ям 38, 60, 56 и далее на отрицательную шину источника питания. Проходя по этому путн, ток считывания перемагничивает в состояние лоложительяой индукции сердечник 12 наличия переноса и сердечник 13 значения «О регистра II.

В следующем такте по входу 57 происходит считЫ|В.ание информации п перезапись ее в накоиительный регистр III. Сразу по входу 69 вопо.мюгательным такто.м считывается ключ переноса на сердечн1нках 11, 12, импульс которого приходит на вход 55 старшего разряда

при отсутствии переноса и на вход 59 при наличии переноса. В первом случае происходит неискаженная передача содерж1имого н-акопительного регистра в регистр II результата дей ствия, во втором случае - увеличение информащии по входу 59 на одну единицу по сравнению с .предыдущей. В таком состоянии схема готова к новому циклу работы.

Предмет изобретения

Десятичный сумматор, выполненный на м.агнитных элементах с распределением тока, содержащий вспомогательный и накапливающий регистры, абмотки затиси которых соедннены по схеме преобразователя двоичного кода .в десягсичиый, и связанный с ними регистр результата, отличающийся тем, чд-о, с целью п.0вы1шения быстродействия, в нем обмотка распределения элемента первого разряда вспомогательного регистра соединена с началом об.моток записи регистра результата, обмотка распределения элемента л-го разряда вапомогателыного регистра соединена с началом обмоток ааписи регистра результата со

сдвигом на п-1 разряд в сторону старших разрядов, причем в цепях формирования переноса обмотки распределения вспомогательного регистра соединены с обмотками записи регистра результата через обмотки записи переносов, концы обмото1К записи регистра результата соединены с началом обмоток распределения накапливающего регистра, и обмотки распределения регистра результата соедниены с облютками затиси накапливающего

регистра.

11 12 /3 W 15

10

1 2 3

22

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU231223A1 |

| ВСЕСОЮЗНАЯ р;г;;«';''!:4;^ 'rr'vlim^f•{'^Q:КЧ sSiil 3 is.:- ; ;,jU;ij !^i,tirt:«;Ь:^;^Л;'ЮТ?НА 1 | 1972 |

|

SU337826A1 |

| Устройство для моделирования времени ожидания заявок в очереди | 1974 |

|

SU503246A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| ПАРАЛЛЕЛЬНЫЙ НАКОПИТЕЛЬНЫЙ ДЕСЯТИЧНЫЙСУММАТОР | 1965 |

|

SU173034A1 |

| ПАТЕНТНО-ТЕХНННЕСКАЯ]БИБЛИОТЕКА | 1971 |

|

SU304704A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| МАТРИЧНОЕ ФЕРРИТ-ДИОДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU395899A1 |

| АНАЛИЗИРУЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU246156A1 |

Даты

1972-01-01—Публикация