1зобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных цифровых системах, имеющих магнитное оперативное запоминающее устройство (МОЗУ).

Известно устройство параллельного суммирования двоичных чисел с последовательиой реализацией переносов на магнитном оперативном запоминающем устройстве с линеЙ1 ой выборкой, в котором в качестве логического устройства используются специально выделенные линейки МОЗУ (см. авт. св. XQ 226955).

Однако в таком устройстве для суммирования двух т-разрядиых двоичных чисел требуется от пяти до 2 - 3 т циклов обращеипя к МОЗУ.

Цель изобретения заключается в сокращении числа циклов обращения к МОЗУ, требующихся для сложения двоичных чисел. Это достигается тем, что в устройстве выход каждого усилителя чтения через блок задержки Н диод соедииен с дополнительным входом считывания ключа регистра регеиерацнн следующего старшего разряда и сдополкительиой шиной импульсного иитания, а выход каждого ключа регистра регенерации подключен к дополнительным выходам считывания ключа следующего старшего разряда.

жении двух т-разрядных чнсел, но следующей логической формуле:

()л,(1)

где Pi I - перенос из /-го в ( + 1) -и разряд;

Pi -перенос из (г-1)-го в г-й разряд;

а,- и &;-сла1аемые г-го разряда; Действительно, перенос нз г-го в ((-Ь1)-й разряд может возникнуть в двух случаях: нри налнчпн еднннц в обоих слагаемых v-ro разряда; ирн иаличип еднннцы в одном из слагаемых -го разряда н переносе в /-и разряд нз (/-1)-го разряда.

Формулу (1) можно нрнвестн к виду:

//.i (/V,-)()-(2)

Для вычисления слова нереносов но формуле

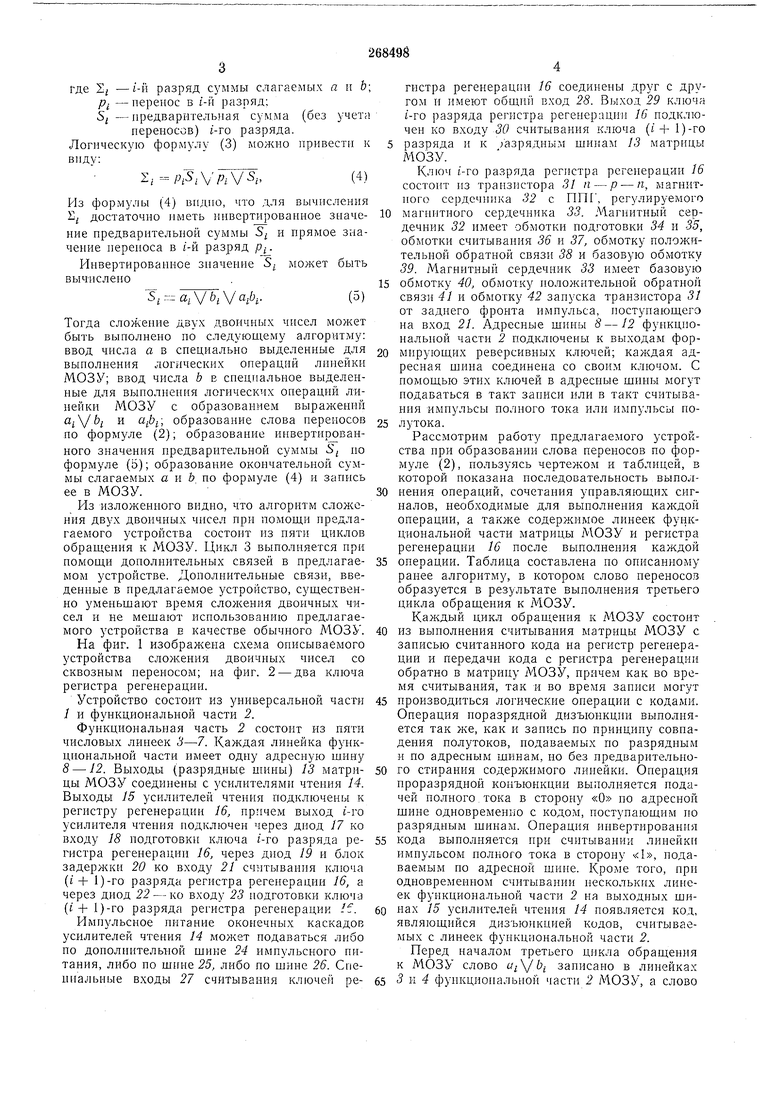

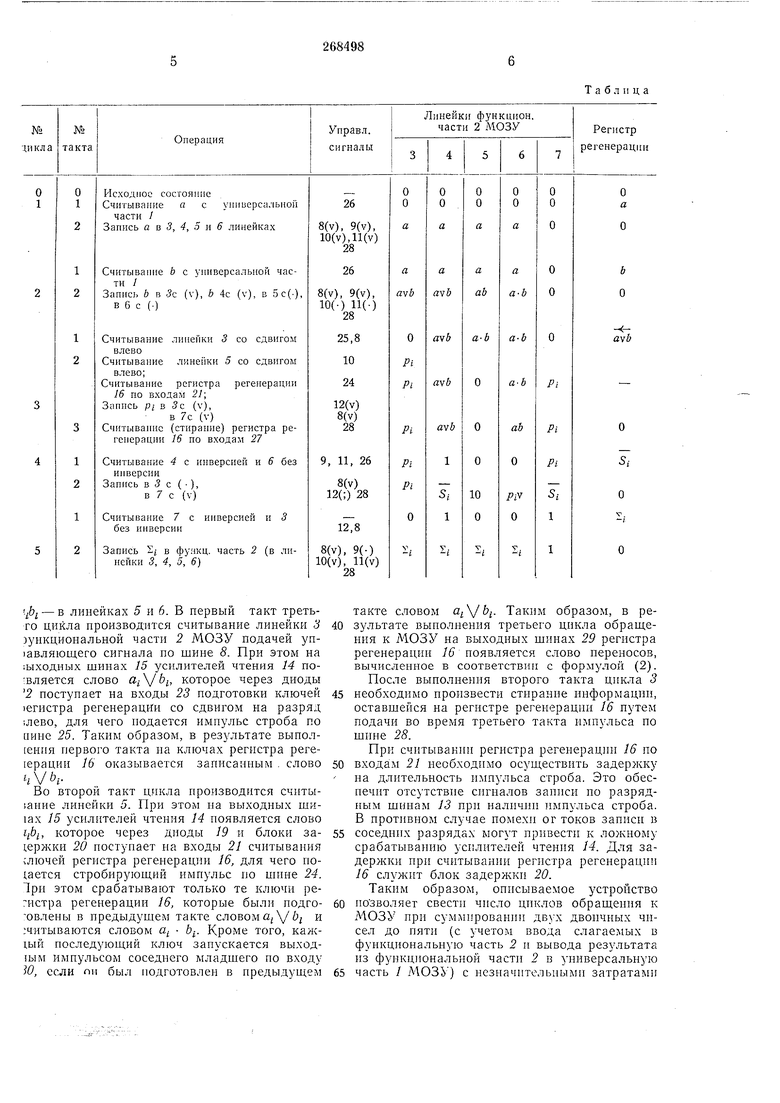

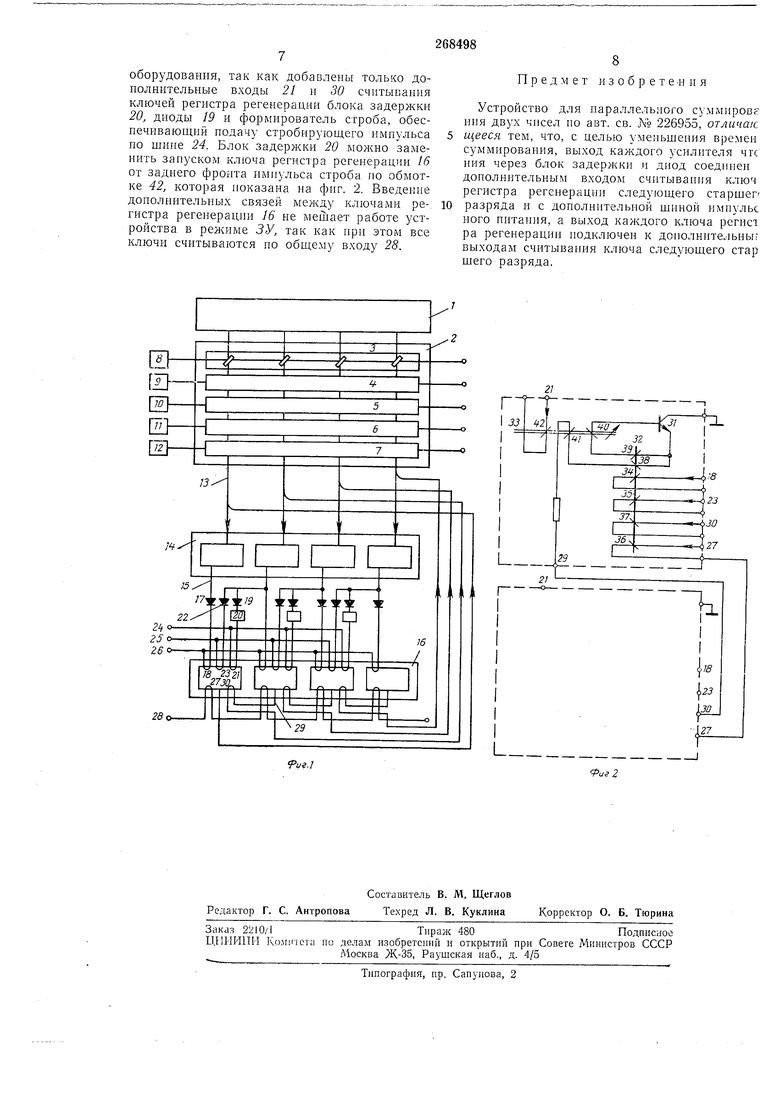

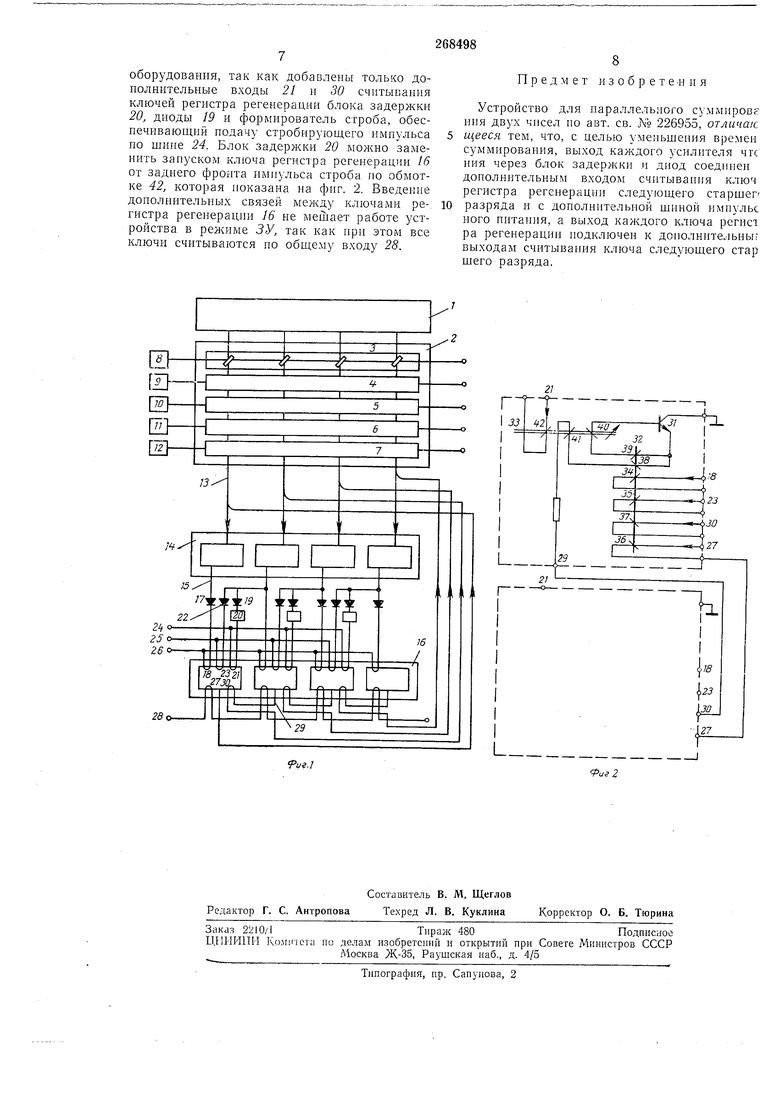

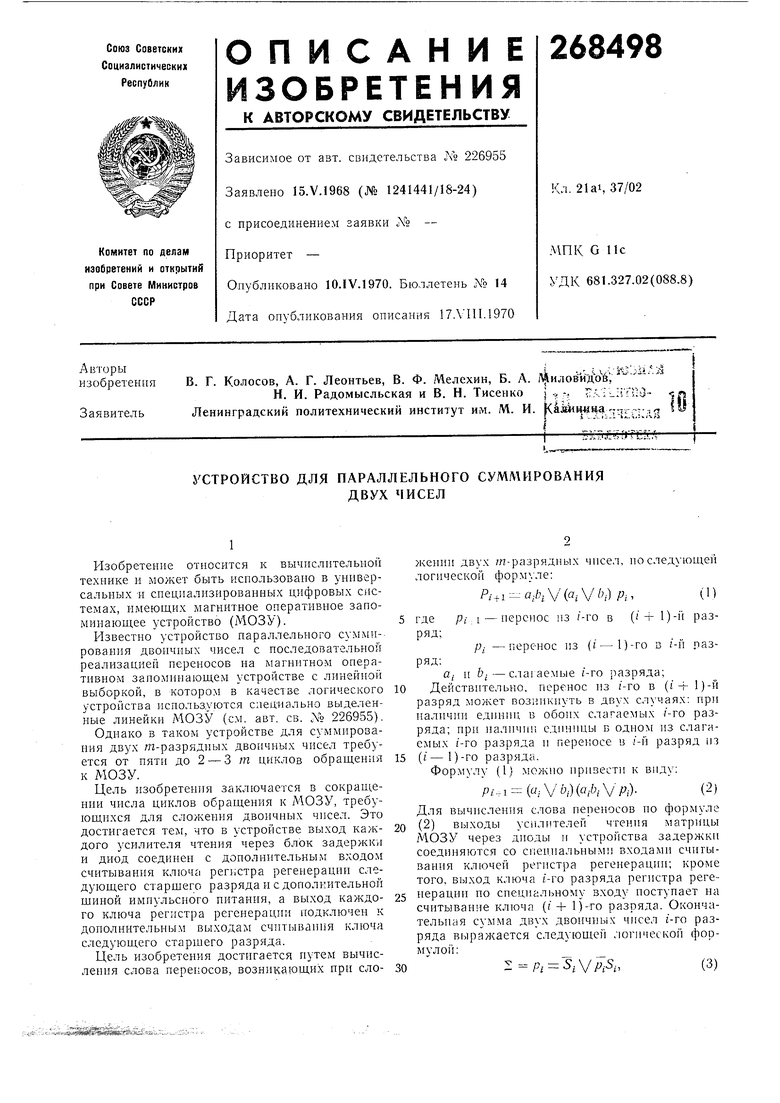

(2) выходы усилителей чтення матрицы МОЗУ через диоды и устройства задержки соединяются со специальными входамн считываиия ключей регистра регеиерации; кроме того, выход ключа i-ro разряда регистра регеиерацнн но снецнальному входу ностунает на считывание ключа (f + 1)-го разряда. Окоичательиая сумма двух двоичных чисел г-го разряда вырал ается следующей логической (f)opмулой:где Е; -г-й разряд суммы слагаемых а и 6 PI -перенос в t-й разряд; 5 -предварительная сумма (без учета переносов) i-ro разряда. Логическую формулу (3) привестн к виду: ,p,/S,, Из формулы (4) видно, что для вычнслення ; достаточно иметь ннвертнрованное зиаченне предварительной суммы S и прямое значение нереноса в t-й разряд pj Инвертироваииое зиачеиие S может оыть вычислено 5,r.fl.V6;V«AТогда сложеиие двух двоичных чисел может быть выиолнено но следующему алгоритму: ввод числа а в специально выделенные для вынолнения логических операций лииейки МОЗУ; ввод числа b в сиецпальиое выделенные для выполнения логических онераций линейки МОЗУ с образованием выражений и аД; образование слова переносов по формуле (2); образование инвертированного значения предварительной суммы i по формуле (5); образование окончательной суммы слагаемых а и b по формуле (4) и заиись ее в МОЗУ. Из изложенного видно, что алгоритм сложения двух двоичных чисел при помойки иредлагаемого устройства состоит из няти циклов обращения к МОЗУ. Цикл 3 выполияется ири номощи доиолнительных связей в предлагаемом устройстве. Дополнительные связи, введенные в нредлагаемое устройство, существенно уменьщают время сложения двоичных чисел и не мещают использованию предлагаемого устройства в качестве обычного МОЗУ. На фиг. 1 изображена схема описываемого устройства сложения двоичных чисел со сквозным переносом; на фиг. 2 - два ключа регистра регенерации. Устройство состоит из универсальной части / и функциональной части 2. Функциональная часть 2 состоит из пяти числовых линеек 3-7. Каждая линейка функциональной части имеет одну адресную шнну 8 -12. Выходы (разрядные шины) 13 матрицы МОЗУ соедииены с усилителями чтения 14. Выходы 15 усилителей чтения подключены к регистру регенерации 16, причем выход i-ro усилителя чтения подключен через диод 17 ко входу 18 иодготовки ключа г-го разряда регистра регенерации 16, через диод 19 и блок задержки 20 ко входу 21 считывания ключа (i + 1)-го разряда регистра регенерации 16, а через диод 22 - ко входу 23 иодготовки ключа (г + 1)-го разряда регистра регеиерации /5. Импульсное иитание оконечных каскадов усилителей чтения 14 может нодаваться либо но доиолнителыюй щине 24 импульсного питания, либо ио щине 25, либо по щине 26. Спегистра регенерации 16 соединены друг с Другом и имеют общий вход 28. Выход 29 ключа f-ro разряда регистра регенерации 16 подключен ко входу f считывания ключа (i + 1)-го разряда и к Уазрядным щикам 13 матрицы МОЗУ. Ключ i-ro разряда регистра регеиерации 16 состоит из транзистора 31 п - р - п, магнитного сердечника 32 с ППГ, регулируемого магннтного сердечника 33. Магнитный сердечник 32 имеет обмотки подготовки 34 и 35, обмотки считываиия 36 и 37, обмотку ноложительиой обратной связи 38 и базовую обмотку 39. Магнитный сердечник 33 имеет базовую обмотку 40, обмотку иоложительной обратиой связи 41 и обмотку 42 заиуска транзистора 31 от заднего фронта импульса, поступающего на вход 21. Адресные шипы 8 -12 функциональной части 2 подключены к выходам формирующих реверсивных ключей; каждая адресная щина соединена со своим ключом. С помощью этих ключей в адресные щины могут подаваться в такт записи или в такт считывания имиульсы иолиого тока или импульсы иолутока. Рассмотрим работд предлагаемого устройства при образовании слова переносов но формуле (2), пользуясь чертежом и таблицей, в которой показана последовательность выполнения операций, сочетания управляющих сигналов, необходимые для выполиения каждой операции, а также содержимое линеек функциональной части матрицы МОЗУ и регистра регенерации 16 после выполнеиия каждой операции. Таблица составлена ио оиисанному ранее алгоритму, в котором слово иереносов образуется в результате выполнеиия третьего цикла обращения к МОЗУ. Каждый цикл обращения к МОЗУ состоит из выиолнения считывания матрицы МОЗУ с записью считанного кода на регистр регенерации и передачи кода с регистра регенерации обратно в матрицу МОЗУ, причем как во время считывания, так и во время записи могут производиться логические операции с кодами. Операция иоразрядиой дизъюнкции выполияется так же, как и заиись по прииципу совпадения полутоков, подаваемых ио разрядным и по адресным щинам, но без предварительного стирания содержимого лииейки. Операция проразрядной конъюнкции выполняется подачей полиого,тока в сторону «О по адресной шине одновременно с кодом, постунающнм но разрядным щинам. Онерация иивертирования кода выполняется при считывании линейки импульсом полного тока в сторону 1, нодаваемым по адресной шипе. Кроме того, ири одновременном считывании иескольких линеек функциональной части 2 па выходных щинах 15 усилителей чтеиия 14 появляется код, являющийся дизъюнкцией кодов, считываемых с линеек функциональной части 2.

Т а б л II ц а

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Устройство для параллельного суммирования двух чисел | 1974 |

|

SU523452A1 |

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| Логическое запоминающее устройство | 1975 |

|

SU529486A1 |

| ЛОГИЧЕСКОЕ ЗАПОЛНИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432598A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

& - в линейках 5 и 6. В первый такт третьго цикла производится считывание линейки 3 40 зункциональной части 2 МОЗУ подачей уп1авляющего сигнала по шипе 8. При этом на ;ыходных шинах 15 усилителей чтения 14 по:вляется слово которое через диоды 2 поступает на входы 23 подготовки ключей 45 югистра регенерации со сдвигом на разряд 1лево, для чего подается импульс строба по айне 25. Таким образом, в результате вынол1ения первого такта на ключах регистра реге ерации 16 оказывается записанным . слово 50 ,. Во второй такт цикла производится считы1ание „тинейки 5. При этом на выходных шиlax 15 усилителей чтения 14 иоявляется слово , которое через диоды 19 и блоки за55;ержки 20 поступает на входы 21 считывания ;лючей регистра регенерации 16, для чего по1,ается стробирующий импульс по шине 24. 1ри этом срабатывают только те ключи регистра регенерации 16, которые были подго60-овлены в предыдущем такте словом и :читываются словом а Ь. Кроме того, каж1,ый последующий ключ запускается выход ым импульсом соседнего младшего ио входу 0, если ли был подготовлен в нредыдуш,ем такте словом . Таким образом, в результате выполнения третьего цикла обраш.ения к МОЗУ на выходных шинах 29 регистра регенерации 16 иоявляется слово переносов, вычисленное в соответствии с формулой (2). После выполнения второго такта цикла 3 необходимо нроизвести стирание информации, оставшейся на регнстре регеперацни 16 путем подачи во время третьего такта импульса но шнне 28. При считывании регистра регенерацнн 16 по входам 21 необходимо осуи ествить задержку на длительность нмнульса строба. Это обеснечит отсутствие сигналов заииси но разрядным шинам 13 при налпчип имнульса строба. В противном случае помехн ог токов записи в соседннх разрядах могут привести к ложному срабатыванию усилителей чтения 14. Для задержки ири считывании регистра регенерацни 16 служит блок задержки 20. Таким образом, описываемое устройство позволяет свести число циклов обраш,еиия к МОЗУ ири суммировании двух двоичных чпсел до нятн (с четом ввода слагаемых в функциональную часть 2 и вывода результата из функциональной части 2 в универсальную

оборудования, так как добавлены только донолнительные входы 21 и 30 считывания ключей регистра регенерации блока задержки 20, диоды 19 и формирователь строба, обеспечивающий иодачу стробирующего импульса по шине 24. Блок задержки 20 заменнть запуском ключа регисара регеперацни 16 от задиего фроита импульса строба но обмотке 42, которая показана иа фнг. 2. Введение донолиительпых связей между ключами ре-, гистра регенерации 16 не мешает работе устройства в режиме ЗУ, так как ирн этом все ключи считываются по обш,ему входу 28.

Предмет и з о б р е т е л и я

Устройство для параллельного сум миров ПИЯ двух чисел но авт. св. jYo 226955, отличшс

щееся тем, что, с целью уменьшения времеп суммирования, выход каждого усилителя чгс ния через блок задержки и диод соединен донолнительным входом счнтывання ключ регистра регсиераини следующего старшег

разряда и с дополнительной шнной нмнульс иого нитаиия, а выход каждого ключа регист ра регенерации подключеи к дополнительны выходам считывания ключа следующего стар шего разряда.

21

Риг.

Даты

1970-01-01—Публикация