Известны параллельные арифметические устройства, содержащие устройство управления, цепи формирования переноса, матрицу выявления знака действия, накопительный регистр и буферный регистр. В таких устройствах используют многообмоточные .ретистры сумматора. Считывание информации с накопительного регистра производится однократно.

Предложенное устройство отличается от известных тем, что в нем устройство управления выполнено ло схеме распределителя токов на шесть выходов и соединено с матрицей выявления знака действия, входы которой присоединены к источникам сигналов, несущих информацию о знаке слагаемых и характере выполняемой операции. Источники рабочих тактов парами подключены ко входу устройства управления. Первая пара соединена по регенераторной кольцевой схеме и через буферный регистр подключена к накалливающему регистру, выполненному ло ком 5инацио1нной схеме десятичиого счетчика с дешифратором кода «2 из 5 в десятичный и имеющему расположенные на неосновных ферритах обмотки сложения, инвертирования и обмотку для сохранения информации при сч«тываоии. Эти обмотки соединены с общими многовитковьши обмотками на основных фе;рритах. Каждая десятая шина накопительного .регистра подклю чена к цепям формиро.зания

переноса, соединенным последовательно з каждом ряде и подключенным К цепям сложения в накопительном регистре.

Эти особенности позволили расширить функциональные возможности устройства и упростить его конструкцию.

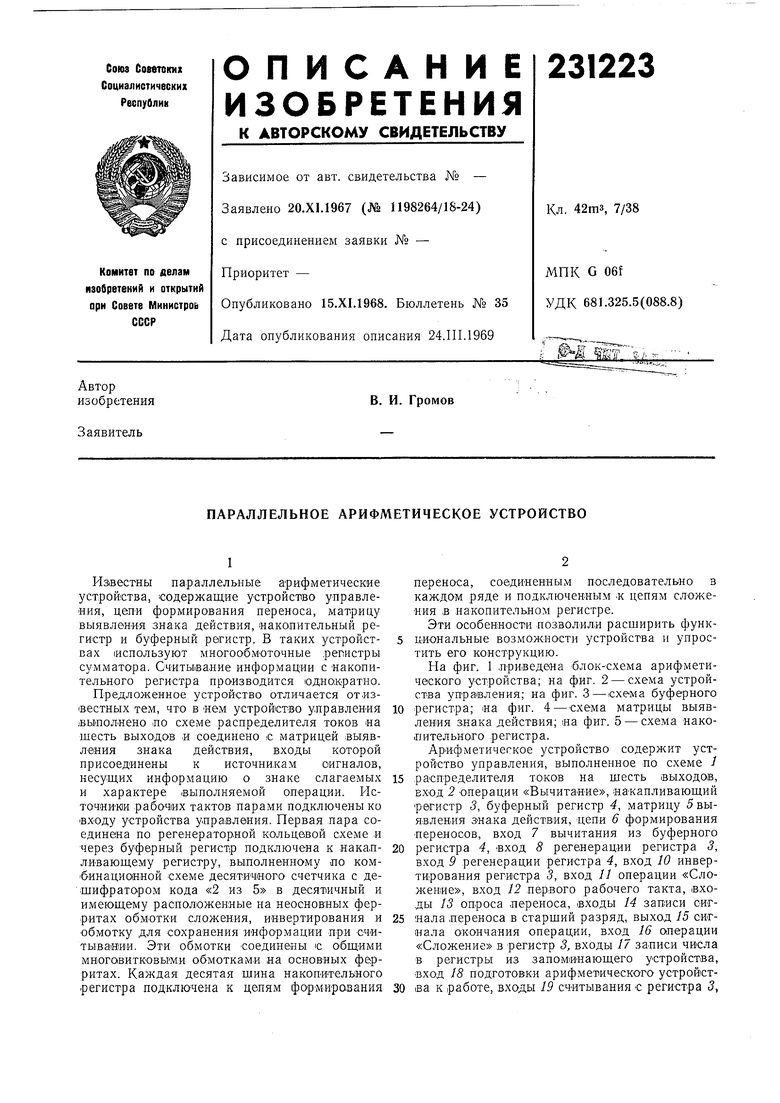

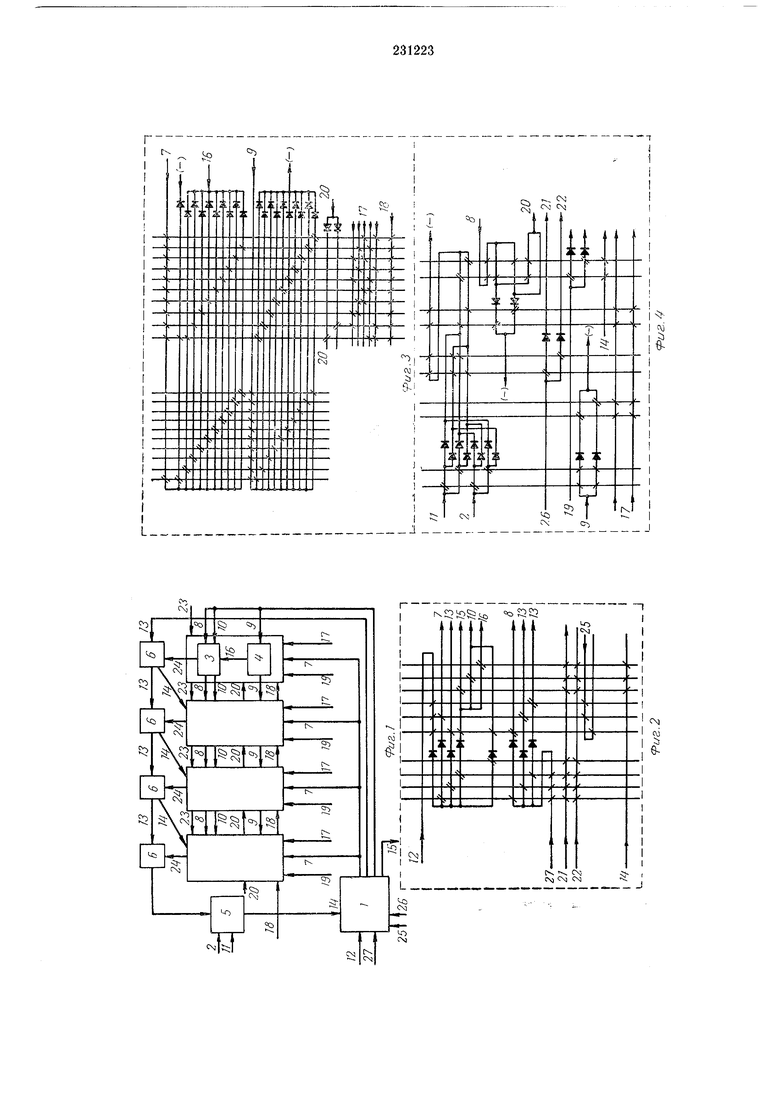

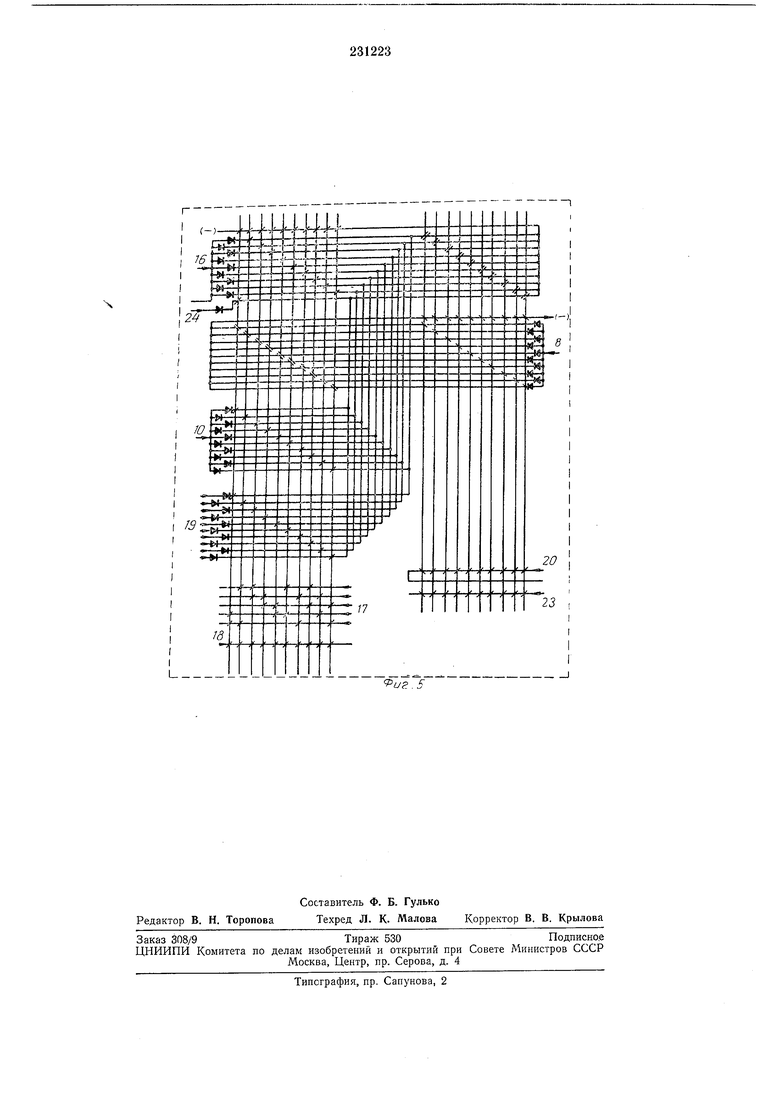

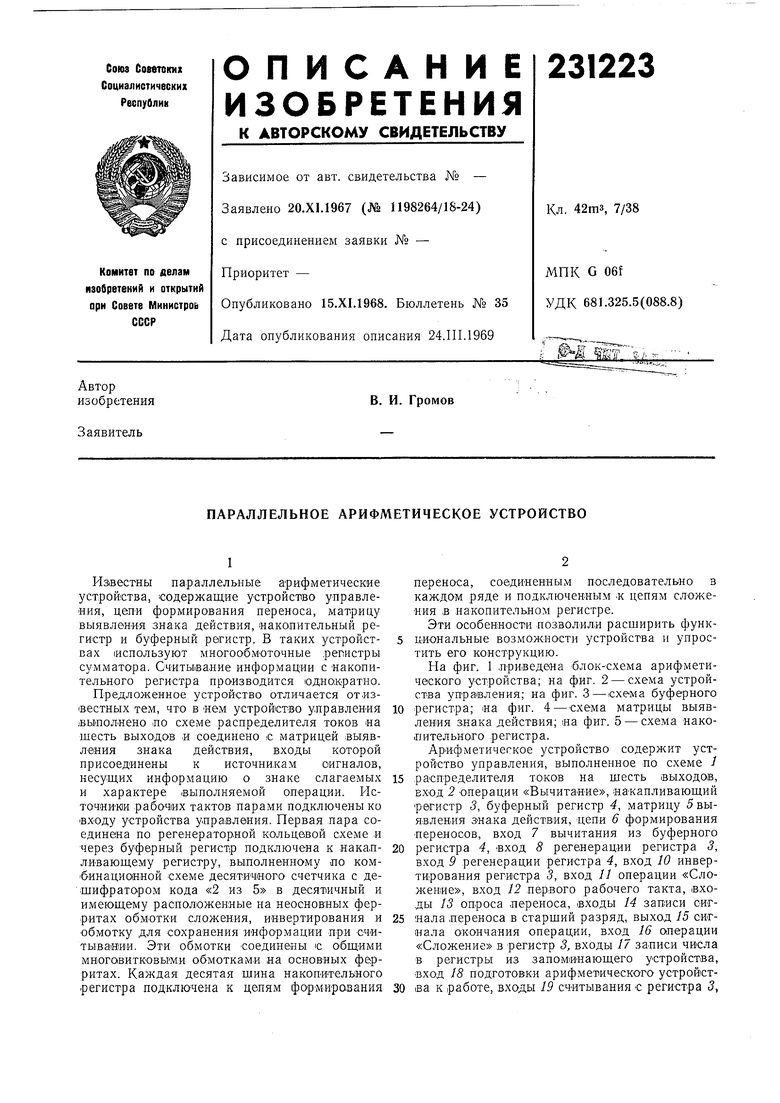

На фиг. 1 лри-ведбна блок-схема арифметического устройства; на фиг. 2 - схема устройства управления; на фиг. 3-схема буферного

регистра; на фиг. 4 схема матрицы выявления знака действия; яа фиг. 5 - схема накопительного регистра.

Арифметическое устройство содержит устройство управления, выполненное по схеме 1

распределителя токов на шесть выходов, вход 2 онерации «Вычитание, накапливающий регистр 3, буферный регистр 4, матрицу 5 выявления знака действия, цепи 6 формирования лереносов, вход 7 вычитания из буферного

регистра 4, вход 8 регенерации регистра 3, вход 9 регенерации регистра 4, вход 10 инвертирования регистра 3, вход // операции «Сложение, вход 12 лервого рабочего такта, входы 13 опроса переноса, входы 14 записи сигнала лереноса в старший разряд, выход 15 сигнала окончания операции, вход 16 операции «Сложение в регистр 3, входы 17 залиси числа в регистры из запоминающего устройства, вход 18 подготовки арифметического устройствходы 20 люгического умножения, вход 21 знака действия (-), вход 22 знака действия (+), вход 23 записи «О в регистре 3, запись 24 переноса, вход 25 такта «а, вход 26 такта «б, вход 27 второго рабочего такта. Работа арифметического устройства. В два регистра 3 и 4 записываются числа, над которыми 1надо произвести арифметическое действие. Из регистра 4 вычитается оо единице и прибавляется в регистр 3 до тех пор, пока содержимое регистра 4 не будет равно 0. В результате получим в регистре 3 результат слолсеиия двух чисел. После того, как содержимое в регистре 4 во всех разрядах будет равно О, происходит перестройка схемы / по входу 25 на выдачу тактов «а опроса нереносов, После опроса .переносов схема 1 реагирует на знак действия и на наличие переносов в старшем разряде ири знаке действия (-) и выбирает одно из трех решений: -инвертирует код, формирует сигнал конца операции или прибавляет единицу в младший разряд регистра 3. Для большей наглядности разберем пример операции сложения. Предварительно в арифметическое устройство приходит из управляющего устройства импульс подготовки по .входу 18. В следующем такте приходит по -входу 17 инвертированный код «2 из 5 и записывает на феррите информацию. По команде «Запись в регистр 5 происходит запись по входу 5 регенерадии числа в накапливающем регистре. на основные ферриты (правые на фиг. 5) и по команде «Запись в регистре по входу 9 регенерации числа регистра 4 на основные ферриты (левые на фит. 3 и 4). Таким образом, записывается информация на регистры 5 и 4, а знаки чисел регистров поступают на матрицу 5 выявления знака действия ко входу 17, где генерируют на основные ферриты соответственно по входам S и Р. После TODO, как числа записаны в регистры, приходит сигнал о характере арифметической операции «сложение в матрицу 5 но входу 11 (фиг. 3 и 4). Сразу же вспомогательным тактом по входу 26 приходит -считывание знака действия и запись его Б схему /. После того, как закончились вопомогательные такты, на схему / приходят первый и второй рабочие такты соответственно по входам 2 и 27 (фиг. 1). Схема 1 выдает такты -в зависимости от алго-ритма рещаемой задачи. По входам 7 импульсы уходят на вычитание единицы из регистра 4 и прибавляют единицу в регистре 5, если содержимое регистра 4 не равно нулю. По входам 8 -выдаются такты регенерации регистров 3 и 4, тем самым готовя их к новой работе. Есл;и содержимое регистра 4 не равно нулю, то схема / по входу 26 будет перестраиваться на регенерадию чисел в регистрах 3 и 4. После того, как содержимое регистра 4 во всех разрядах станет равно нулю, по входу 26 не будут .приходить импульсы « схема не будет перестраиваться на регенерацию, а будет выполнять опрос переноса. Опрос переноса происходит в три такта по входам 13. После опроса переноса схема 1 выдает сигнал окончания, та,к как в ней был подготовлен соответствующий феррит импульсов знак действия (-)-) по входу 22. Если выполнялась операция «Вычитание и знак действия был (-), то схема отрабатывает или операцию инвертирования содержимого регистра 3, или же добавление единицы в младший разряд регистра 3, в зависимости от наличия переноса в старшем разряде при операции (-). В последнем такте происходит регенерация числа регистра 3 на основные ферриты. В этом |СостояНИИ схема снова готова записывать информацию и выполнять операции над числами. Предмет .изобретения Параллельное арифметическое устройство, содержащее устройство управления, цепи формирования переноса, матрицу выявления знака действия, накопительный регистр и буферный регистр, отличающееся тем, что, с целью расширения функциональных возможяостей устройства и упрощения конструкции, в нем устройство управления выполнено по схеме распределителя токов на шесть выходов и соединено с -матрицей выявления знака действия, входы которой присоединены к источникам сигналов, несущих информацию о знаке слагаемых и характере выполняемой операции; источники рабочих такгов парами подключены ко входу устройства управления, причем первая пара соединена по регенеративной кольцевой схеме и через буферный регистр подключена к накапливающему регистру, выполненному по комбинационной схеме десятичного счетчика с дешифратором кода «2 из 5 в десятичный с об-мотками , инвертирования и обмоткой для сохранения информации при считывании на неосновных ферритах, соединенными с общими многовит1ковыми об.мотками на основных ферритах, последние из которых на неосновных ферритах соединены без сдвига; каждая десятая щ-ина накопительного регистра подключена к цепям формирования переноса, соединенным последовательно в ка}кдом ряде и подключенным к цепям сложения в накопительном регистре.

. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО СПЕЦИАЛИЗИРОВАННОЙ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1969 |

|

SU234753A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

Даты

1968-01-01—Публикация