Изобретение относится к областн вычислительной те.хники и может быть нснользовано в арифметических устройствах параллельного или последовательно-параллельного тнпа, онерирующих с двоично-кодированными десятичнымИ числами.

Известны двоично-десятичные накапливающие сумматоры (вычитатели), содержащие триггерный суммирующий регистр, триггерный регистр для хранения двоичных переносов н логические элементы на входах триггеров регистра переносов. Недостатком таких сумматоров является необходимость дополнительного времени для раснространення переносов при введении коррекции.

Целью изобретения является повышение быстродействия сумматора (вычитателя) за счет исключения времени на распространение двоичных переносов (заемов) при коррекции.

Указанная цель в предложенном сумматоре достигается за счет того, что в него включены дополнительно три схемы «И на входе регистра переносов, один из входов иервой схемы «И соединен с прямым выходом второго разряда суммирующего регистра, один из входов схемы «И соединен с прямым выходом третьего разряда суммирующего регистра. Выходы обеих схем «И соединены с входами схемы «ИЛИ четвертого разряда регистра переносов. Один из вхо.дов третьей схемы «И

соединен с инверсным выходом второго разряда суммирующего регистра. Выход третьей схемы «И соедннен с входом схемы «ИЛИ третьего разряда регистра переносов. Другие входы элементов «И и элемеита «ИЛИ второго разряда регистра переносов соединен) с управляющей шиной.

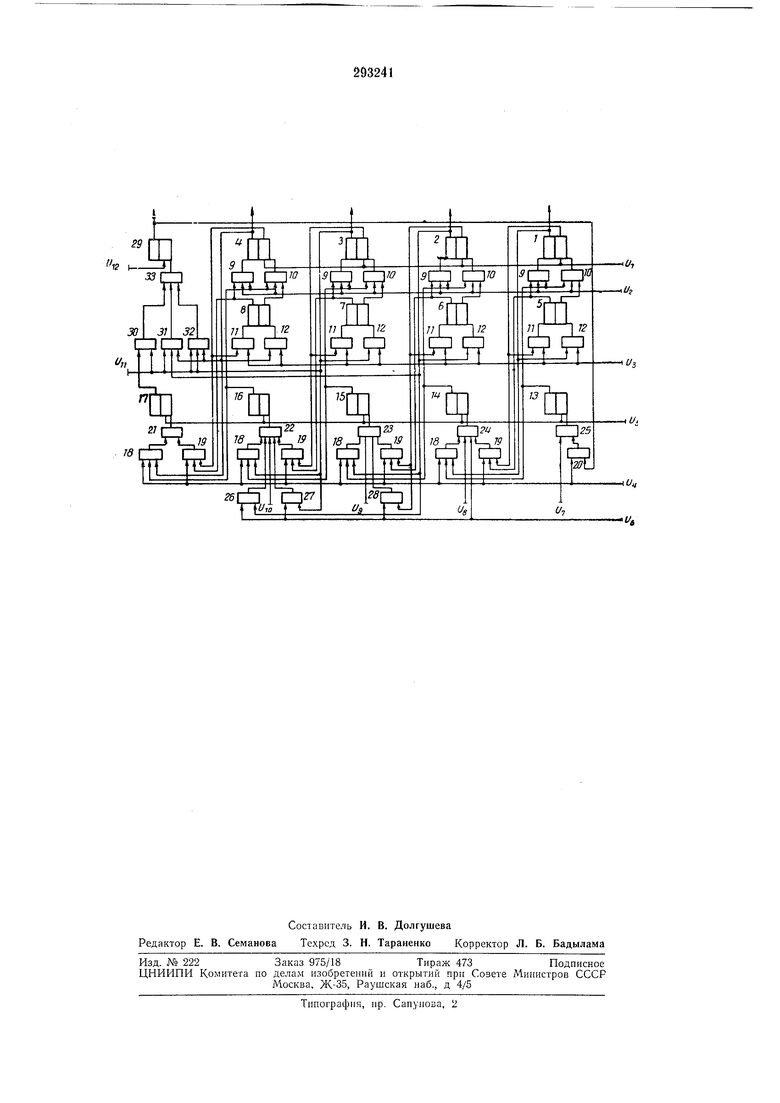

На чертеже прпведепа логнческая схема последовательно-параллельного накапливающего сумматора, работающего в двопчио-десятнчном коде с весами двоичных разрядов 8-421 и ностроенного на нотенциальных элементах.

Сумматор содерл 11Т суммирующий регистр, состоящий )13 основных триггеров /-4, вспомогательных трнггеров 5-8 н лог ческпх элементов «И 9-12 на входах этих триггеров, и регистр переносов, состоящий из триггеров 13- 17, логических элементов «И 18-20-«ИЛИ 21-25 на входах этих триггеров для образования и передачи двоичных переносов и .донолнительных логических элементов «И 26-28-«ИЛИ 22-24 для образования корректирующих кодов.

Кроме того, в сумматоре имеется триггер 29 с логическими элементамн «И 30-,W н «ИЛИ 33 на входе для образован-ия и временного хранения десятичного переноса.

зует потенциальный счетный триггер, счетный вход которого соединен с единичным выходом соответствующего триггера регистра переносов. Унравление работой суммирующего регистра осуществляется потенциальными сигналами t/i - t/3. Сигнал Ll служнт для установки основных триггеров в нулевое состояние. По сигналу f/3 содержимое осиовиых триггеров передается во всномогательиые, а но сигналу dz в тех разрядах, где на счетный вход постунает единнчный нотенциал от триггеров регистра иереносов, осиовные триггеры меняют свое состояние на обратное, осуществляя тем самым поразрядное сложение но модулю два своего содержимого с содержимым четырех младщнх разрядов регистра иереносов.

На единичных входах триггеров 17-14 регистра переносов включены логические элементы «И 18, «И -/5 -«ИЛР1 21-24, которые служат для образования двоичных иереиосов при кодов двоично-десятичных числе. В данном сумматоре двоичиые иереиосы образуются по следующему логическому уравнению:

Л; + 1 CiAiVCiBi,

где Л,-+ - неренос в(1-г1)-й разряд нз г-го, С,- и Сг - значение суммы но модулю 2 в

i-OM разряде и ее инверсия, Bi - зиаченне г-го разряда одного из

слагаемах.

На еднннчном входе триггера 13 включены логические элементы «PI 9 - «ИЛИ 25, через которые в этот триггер передается хранящийся в трнггере 29 десятичный неренос из нредыдущего десятичного разряда. Образованием н нередачей нереносов унравляет сигиал U. Сигнал /5 служит для устаиовки триггеров регистра переиосов в нулевое состояиие. Кроме того, на входах триггеров 16-14 регистра иереносов включены донолнительиые логические элементы «И 26-2S -«ИЛИ 22--24, которые служат для образовання в нем корректирующих кодов. Входы этих элементов соединены с выходами основных триггеров суммирующего регистра и с управляющим сигналом UQ, но которому ироисходит образование корректнрующнх кодов. Ири сложении в коде 8421 разряды корректирующего кода нолучают по следующил логическим уравнеииям:

Л,б Л,5 С2; Л1з 0, в соответствии с которыми и выполнены соединения на чертеже.

В сумматоре четыре младщих разряда регистра Переносов, помимо онисаииых функций, служат еще в качестве буферного регистра, в котором времеино хранятся коды десятичиых цифр, участвующих в сложении чисел, последовательио считываемые из запоминающего устройства. Для этого триггеры 16-13 имеют входы U-; - и 10, которые соединяются с уситителями считывания.

триггер 29 и логические элементы «И 30-32 и «ИЛИ 33 на его единичном входе. Эти элементы включены в соответствии с уравиением

Г29 Л,7УС4СзУС,С2.

Образованием десятичного переноса управляет сигнал Uii, а сигиал U служит для установки триггера 29 в нулевое состояние. Единичные выходы основных триггеров суммирующего регистра являются выходами сумматора, с которых снимается код десятичиой суммы и иодается на усилители записи запоминающего устройства (ЗУ). Выход с триггера 29 исиользуется в устройстве унравления

для выработки сигиала UR.

Оиисанный накаиливающий с мматор полную обработку двух десятичиых цифр осуществляет за щесть тактов, каждый из которых, как это ирииято в потенцнальной системе элемеитов, делится на две фазы cpi и ф2. Предположим, что в предыдущем цикле сложеиия с помощью сигиала Ui триггеры /-4 были устаиовлеиы в «О, а триггер 29 храпит возможную единицу иереиоса из иредыдущего десятичного разряда (состояние остальных трнггеров - безразлично).

В иервой фазе иервого такта па входы t/ -

-UIQ с усилителей считывания иоступает код очередиой цифры иервого слагаемого, одновременно па вход U нодается снгиал нротивопололсной полярности, заканчивающийся несколько ранее сигиалов Uj - УЮ. В результате иредыдущее содержимое регистра Л гасится, и в его триггеры 16-13 записывается код иервого слагаемого. Кроме того, в этой фазе иодается сигнал 1/3, по которому триггеры регистра В в соответствии с содержимым регистра С устанавливаются в «О. Во второй фазе первого такта подается сигнал U, но которому код первого слагаемого передается в регистр С, складываясь иоразрядио ио модулю два с нулевым содержимым иоследнего. Одновременно с выходов регистра С ироисходит запись (регеиерация кода иервого слагаемого в ЗУ).

В первой фазе второго такта на входы UT -

-Uio с усилителей считывання постунает одновременно с сигналом 1/5 код очередной цифры второго слагаемого и устанавливается в

триггерах 16-13. Кроме того, иодается сигнал Us,, по которому код первого слагаемого, хранящийся в регистре С, переписывается еще и в регистр В.

Во второй фазе второго такта по сигналу

f/2 в регистре С происходит поразрядное сложение ио модулю два кодов первого и второго слагаемого.

В третьем такте подаются сигналы t/5 и Ь4, но которым в регистре Л происходит

образование двоичиых иереносов. Длительность сигнала U такая же, как и в иредыдущих тактах, т. е. несколько менее длительиости одной фазы, а сигнал U должен иметь длительность, достаточную для иоследовательноправлении от младшего разряда к старшему, ввиду возможного распространения двоичного переноса. В первой фазе четвертого такта подается силнал f/3, по которому содержимое регистра С переписывается в регистр В. Во второй фазе четвертого такта подаюгся сигналы 1/2, О ,9 и и ц. По сигналу 1/2 в регистре С происходит поразрядное сложение по модулю два храняш,ейся в нем поразрядной суммы слагаемых с полученными в регистре Л двоичными переносами, в результате чего в регистре С образуется полная двоичная сумма слагаемых. По сигналам f/i2 и f/u, в зависимости от наличия двоичного переноса в триггере 17 или от образования в регистре С псевдотетрады, в триггере 29 записывается единица переноса в слеДУЮШ.ИЙ десятичный разряд. Если иосле четвертого такта триггер 29 содержит нуль, то это означает, что в регистре С образовалась иравильная десятичная сумма, п лятый такт пропускается или остается холостым. При наличии в триггере 29 единицы в иер вой фазе ПЯТОГО такта подаются сигналы из, Us п t/6. По сигналу f/з содержимое регистра С переписывается в регистр В, а по сигналам Us и Ue в регистре А образуется корректирующий код. Во второй фазе пятого такта по сигналу 1/2 в регистре С происходит поразрядное сложение но модулю два хранящегося в нем кода некорректированной двоичиой суммы с полученным в регистре А корректирующим кодом, в результате чего в регистре С образуется правильная десятичная сумма. В первой фазе шестого такта производят запись десятичной суммы из регистра С в ЗУ, а во второй фазе ио сигналу L/i регистр С устанавливается на нуль, н управляюш,пе цепи ЗУ переключают на следующий десятичный разряд.

жение пли вычитание. Описанный цикл новторяется столько раз, сколько десятичных разрядов содержат складываемые числа. Если цепи, образования двоичных переносов выполнить по уравнению Лг+1 CiAiV CiBi, г цепи образования корректнруюш,его кода- по уравиенпям Л.б-Со; Л, Л,з 0, то -4i6 С:-,/ описанная схема преврап,ается в вычитатель, который будет выполнять вычитание двоичнодесятичных чисел в прямых кодах. При этом в первом такте надо подавать вычитаемое, а во втором - уменьшаемое. При необходимости можно построить сумматор-вычитатель, который в зависимости от уиравляюших сигналов будет выиолнять слоПредмет изобретения Двоично-десят 1чный накапливающий сумматор, содержаш,ий суммпруюш,пй регистр. регистр переносов и логические элементы «И п «ИЛП, отличающийся тем, что, с целью повышения быстродейстЕ 1я, он дополнительно содержит на входе регистра переносов три схемы «И, один из входов первой схемы «И соединен с прямым выходом второго разряда суммирующего регистра, од1П1 из входов второй схемы «И соедпнен с прямым выходом третьего разряда суммирующего регистра, выходы обеих схем«П соединены с входами схемы «ИЛП четвертого разряда регистра переносов, одни из входов третьей схемы «П соединен с инверсным выходом второго разряда суммирующего регистра, вы.ход третьей схемы «И соединен с входом схемы «ПЛИ третьего разряда регистра переносов, другие входы элементов «П и элемента «ИЛИ второго разряда регистра переносов соедииены с управляюн ей щииой.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМБИНАЦИОННЫЙ СУММАТОР | 1969 |

|

SU236858A1 |

| УСТРОЙСТВО для | 1973 |

|

SU398947A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Отсчетное устройство | 1975 |

|

SU614435A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

Даты

1971-01-01—Публикация