Устройство относится к области измерительной техники и автоматики и может быть использовано при построении технических средств автоматики и измерительных систем, например, для суммирования нескольких последовательностей импульсов с частотной модуляцией.

Известно устройство для суммирования иМПульсных сигналов, преобразующее число одновременно поступающих Импульсов в последовательную серию импульсов, задержанных относительно друг друга.

Однако в таком устройстве при формировании суммарной последовательности часть импульсов может поступить после окончания измерительного интервала, что приводит к ощибкам в результатах сложения.

Предложенное устройство отличается тем, что в нем суммирование осуществляется на счетчике с фиксацией совпадения входных импульсов во времени на дещифраторе кратности совпадений, выходы которого связаны с управляющими входами схем запрета, а к их информационным входам подключены шины суммируемых импульсов. Выходы схем запрета подключены ко входам триггеров соответствующих разрядов счетчика, а выходы схем запрета каналов с нечетной кратностью совпадения через схему «ИЛИ дополнительно подключены ко входу одновибратора с нулевым временем восстановления, выход которого через формирователь и схему запрета подключен ко входу триггера первого разряда счетчика.

Это позволяет повысить точность выполнения операции.

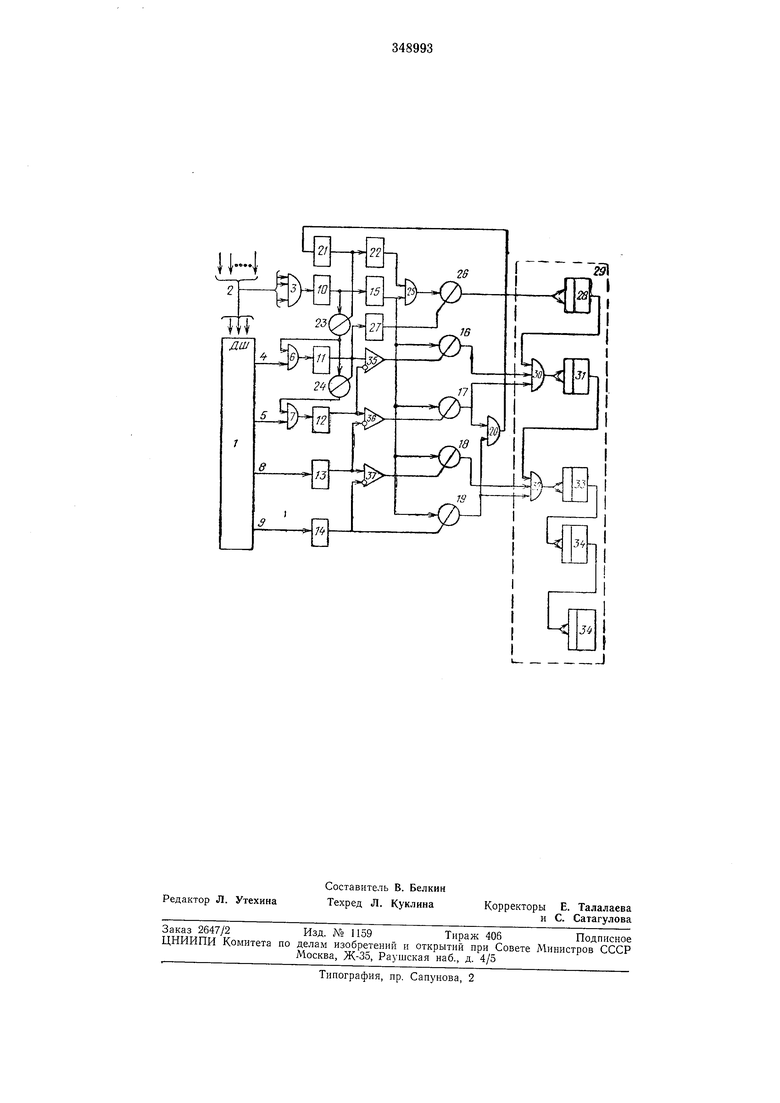

Схема предлол енного устройства для случая совпадения во времени не более 5 (при

условии совпадения в следующий момент времени не более двух импульсов) изображена на чертеже.

Устройство содержит дещифратор кратности совпадений 1, на входы которого подключены шины входных импульсов 2, подключенные ко входам схемы «ИЛИ 3. Выходы 4, 5 дешифратора 1 подключены ко входам схем «ИЛИ 5 и 7 соответственно. Выходы схем «ИЛИ 3, 6, 7 8, 9 дешифратора 1 подключены ко входам формирователей 10-14 соответственно. Выход формирователя 10 через линию задержки 15 связан с информационными входами схем запрета 16-19. Выходы схем запрета 17 и 19 соединены со входами

схемы «ИЛИ 20, выход которой подключен ко входу составного одновибратора 21 с нулевым временем восстановления. Выход одновибратора 21 подключен ко входу формирователя 22 и к управляющему входу схемы

ционным входом схемы запрета 24 и.входом схемы «ИЛИ 6.

Информационный вход схемы запрета 2§ соединен с выходом формирователя 10. Выход формирователя 22 через схему «ИЛИ 25, второй вход которой соединен с выходом линии задержки 15, подключен к информационному входу схемы запрета 26. Управляющий вход схемы запрета 24, выход которой подключен ко входу схемы «ИЛИ 7, связан через инвертор 27 с управляющим входом схемы запрета 26, соединенной по выходу со входом триггера 28 первого разряда счетчика 29. Выход триггера 28 соединен через схему «ИЛИ 30, на другие входы которой подключены выходы схем запрета 16 и 17, со входом триггера 31 второго разряда счетчика 29. Выход триггера 31, в свою очередь, через схему «ИЛИ 32, на другие входы которой подключены выходы схем запрета 18 и 19, соединен со входом триггера 33. Триггер 33 по выходу, как и все остальные триггеры 34 счетчика 29, связан со счетными входами триггеров соседних разрядов. Управляющие входы схем запрета 16-18 соединены с выходами схем «И 35-37 соответственно. Прямые входы схем «И 55-37 соединены с выходами формирователей //-13, а инверсные входы-с выходами формирователей 12-14 соответственно. Управляющий вход схемы запрета 19 связан с выходом формирователя 14.

Устройство работает следующим образом.

Входные импульсы поступают на щины 2 и через схему «ИЛИ 3, формирователь 10, линию задержки 15, схему «ИЛИ 25 и схему запрета 26, на управляющий вход которой через инвертор 27 в случае несовпадения во времени имиульсов поступает разрешающий сигнал, передаются на вход триггера 23 первого разряда счетчика 29.

При совпадении любых двух импульсов сигнал с выхода 4 дешифратора / через схему «ИЛИ 6, формирователь 11 и инвертор 27 по управляющему входу схемы запрета 26 прекращает поступление импульсов на вход триггеру 28. Через схему «И 35, на инверсный вход которой сигнал не подан, сигнал с выхода 4 дешифратора / поступает на уг1равляющий вход схемы запрета 16 и разрешает прохождение задержанного во времени входного импульса (точнее двух совпавших импульсов) через схему «ИЛИ 30 на вход триггера 3tl второго разряда счетчика 25 и в нем записывзется число 2.

При совцадении трех импульсов сигнал появляется на щинах и б дешифратора /. Через схему «И 36, на инверсный вход которой импульс не подается, на управляющий вход схемь запрета поступает разрешающий сигнал, а в счетчик, как и в предыдущем случае через схему «ИЛИ 30 записывается число 2. Одновременно через схему «ИЛИ 20 сигнал поступает на одновибратор 21, построенный таким образом, что формируемые им импульсы равны по длительности разрешающей способности счетчика и возможно формирование очередного импульса сразу же после окончания предыдущего. Сигнал, сформированный по заднему фронту импульса с выхода одновибратора 21 на формирователе 22 через схему «ИЛИ 25 и открь1тую к этому времени схему запрета 26, поступает на вход триггера 28, записывая в счетчике единицу. Таким образом, в счетчик записывается число 3.

При совпадении четырех импульсов сигналы появляются на выходах 4, 5 }i 6 дешифратора 1 и по аналогии со случаем двух совпадений открыта только схема запрета 18. В счетчик записывается число 4 на триггер 33

через схему «ИЛИ 32.

При совпадении пяти импульсов сигналы формируются на шинах 4, 5, 8 и 9 дешифратора 1, в счетчик записывается число 4 и через одновибратор 21 аналогично случаю

трех совпадений с задержкой во времени записывается еще единица. Таким образом, в счетчик записывается число 5.

Если во время работы одновибратора 21 на вход устройства поступает импульс, то он

через открытую схему запрета 23 поступает на схему «ИЛИ 5 и аналогично сигналу с выхода 4 дешифратора / записывает в счетчик число 2. При поступлении двух совпадающих импульсов через схему «ИЛИ 7 аналогично сигналу с выхода 5 дешифратора / в счетчик записывается число 3.

Предмет изобретения

Устройство для суммирования импульсов, содержащее дешифратор кратности совпадения импульсов во времени и связанные с ним логические схемы, формирователи и двоичный счетчик, линию задержки, одновибратор с нулевым временем восстановления,. отли чающееся тем, что, с целью повышения точности выполнения операции, выходы дешифратора через формирователи и схемы «И

подключень к управляющим входам схем запрета, к информационным входам которых через схемы «ИЛИ подключены шины суммируемых импульсов, выходы схем запрета подключены ко входам триггеров соответствующих разрядов счетчика, а выходы схем запрета каналов с нечетной кратностью совпадения через схему «ИЛИ подключены ко входу одновибратора с нулевым временем восстановления, выход которого через формирователь и схему запрета подключен ко входу триггера первого разряда счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления намоточным станком | 1987 |

|

SU1451648A1 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Устройство для контроля проскальзывания и отклонения скорости гибкой тяги | 1989 |

|

SU1791839A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для определения номера транспортного средства | 1988 |

|

SU1555169A1 |

| Устройство для контроля модулей коммутации | 1984 |

|

SU1273931A1 |

| Устройство для счета метража и определения теоретической массы проката | 1981 |

|

SU955096A1 |

| Устройство для вывода отображаемой информации | 1986 |

|

SU1322252A1 |

| Устройство для задержки импульсов с программным управлением | 1979 |

|

SU866722A1 |

Даты

1972-01-01—Публикация