)етенне опюсится к автоматике и вычислительно технике, в частности к индикаторным устройствам, и может быть использовано в устройст- плх вывода информации из ЭВМ.

Цель изобретения - увеличение пропускной способности устройства за счет исключения передачи псевдопосто яниой отображаемой информации.

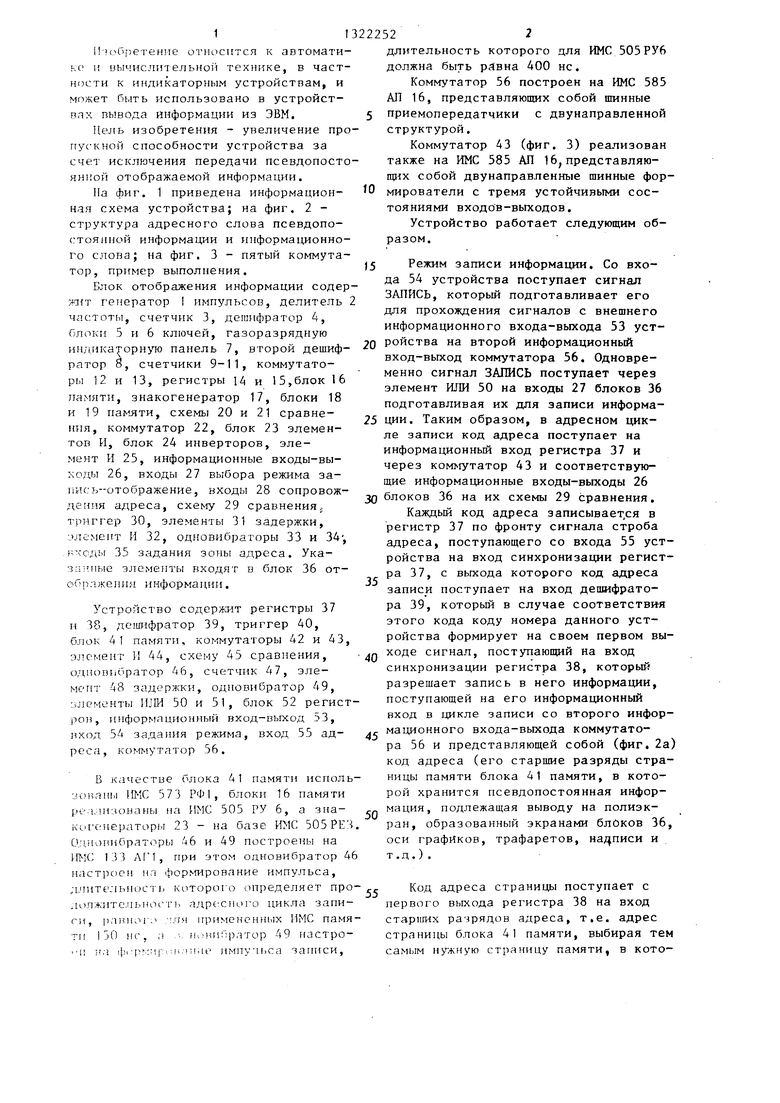

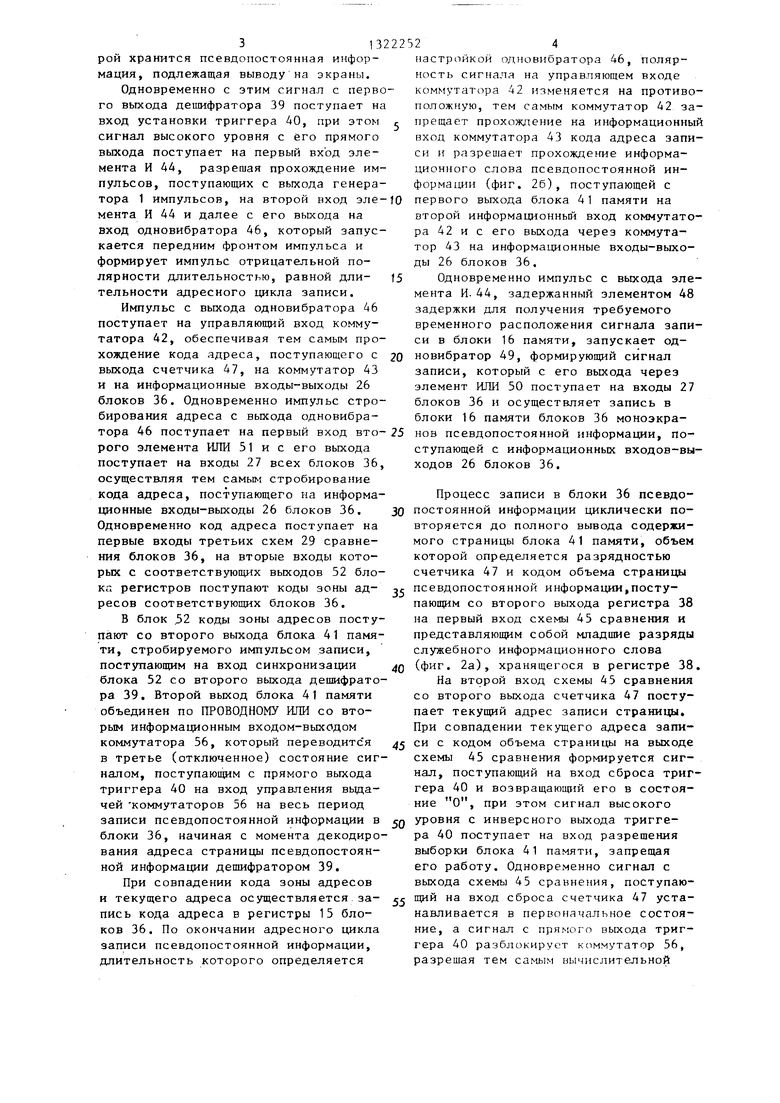

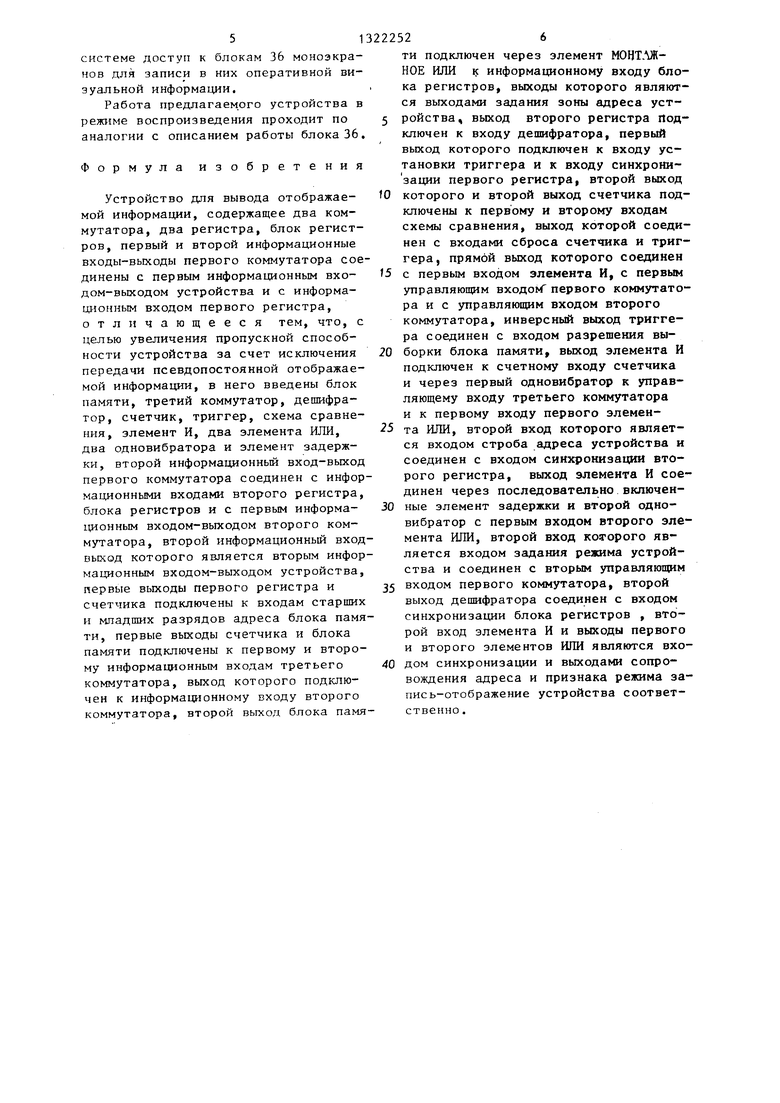

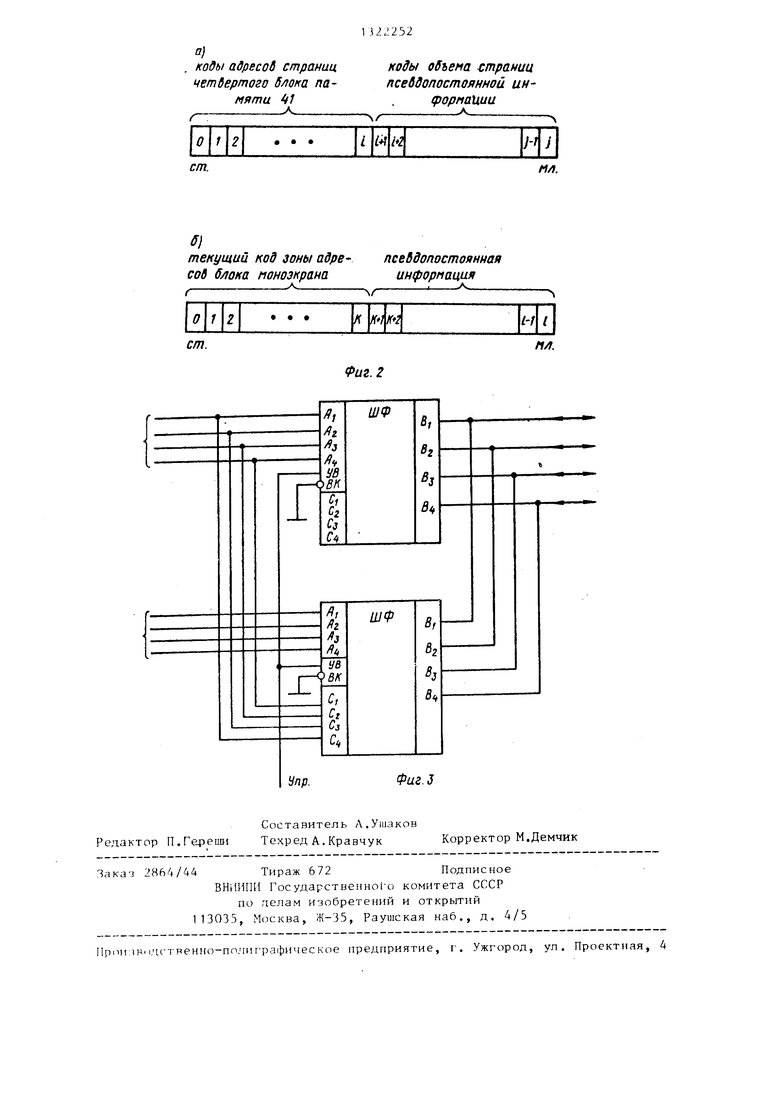

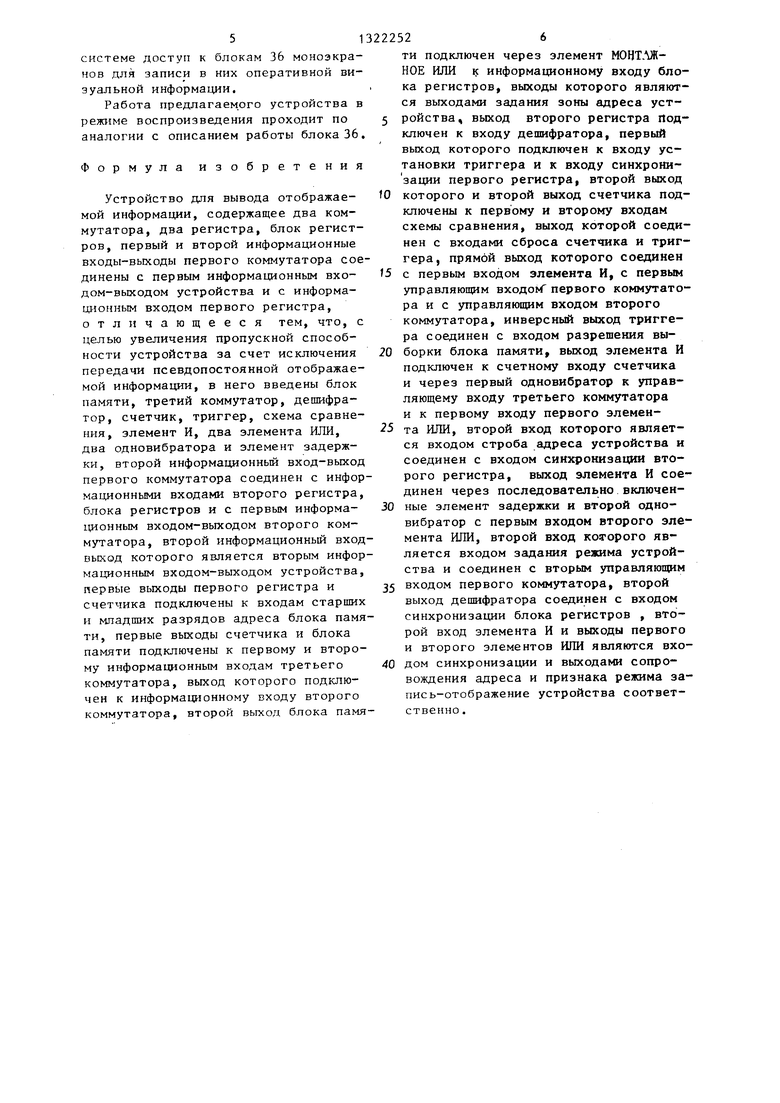

На фиг. 1 приведена информационная схема устройства; на фиг. 2 - структура адресного слова псевдопо- стоялной информации и информационного слова; на фиг. 3 - пятый коммутатор, пример выполнения.

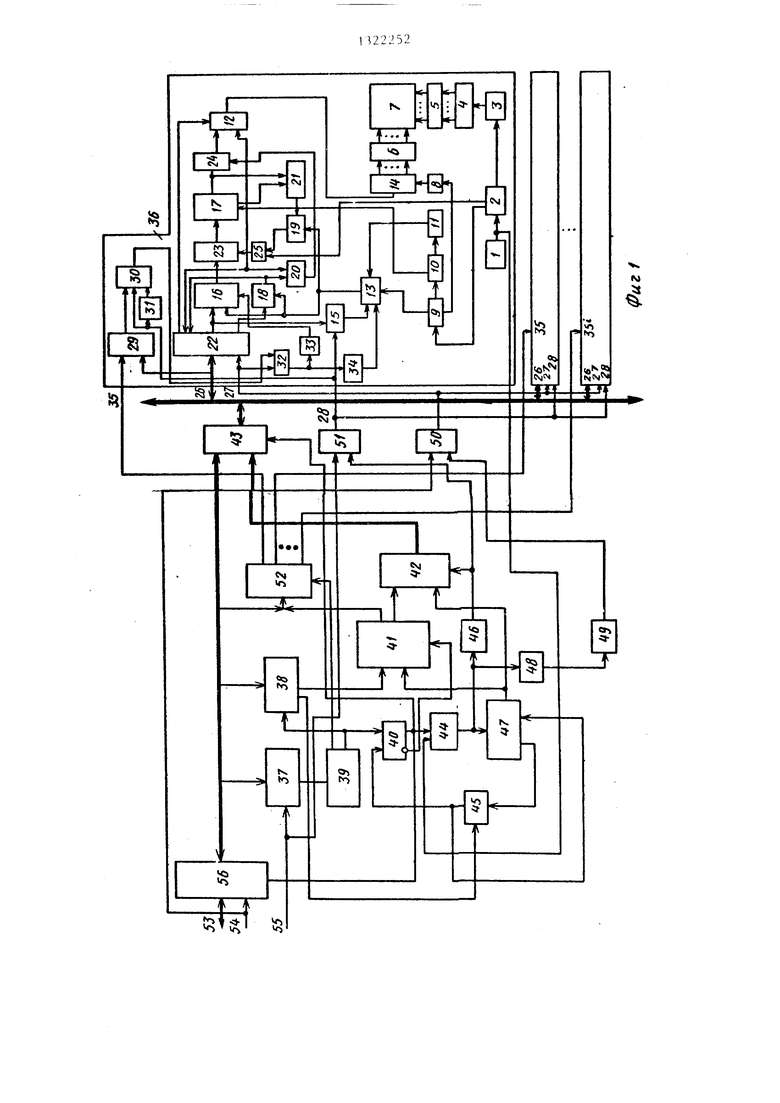

Блок отображения информации содержит генератор i импульсов, делитель частоты, счетчик 3, дешифратор 4, блоки 5 и 6 ключе, газоразрядную индика орную панель 7, второй дешифратор 8, счетчики 9-11, коммутаторы 12 и 13, регистры 14 и 15,блок 16 памяти, знакогенератор 17, блоки 18 и 19 памлти, схемы 20 и 21 сравнения, коммутатор 22, блок 23 элементов И, блок 24 инверторов, элемент И 25, информационные входы-выходы 26, входы 27 выбора режима запись-отображение, входы 28 сопровождения адреса, схему 29 сравнения триггер 30, элементы 31 задержки, элемент И 32, одновибраторы 33 и 34, t-cc;i,bi 35 задании зоны адреса. Ука- элементы входят в блок 36 от- еГ рлжения информа1Ц1И.

Устройство содерймт регистры 37 и 38, де1Ш1фратор 39, триггер 40, блок 41 памяти, коммутаторы 42 и 43, элемент И 44, схему 45 сравнения, одпоиибратор 46, счетчик 47, элемент 48 задержки, одновибратор 49, элементы ИЛИ 50 и 51, блок 52 регист рон, информационный вход-выход 53, нход 54 задания режима, вход 55 адреса, коммутатор 56.

В качестве блока 41 памяти испол з(15аны IMC 573 РФ 1 , блоки 16 памяти реали-чонаны на ИМС 505 РУ 6, а зна; с1ГС-иератор,1

23 - на базе ИМС 505 РЕЗ.

Однопибраторы 46 и 49 построены на 1ГМС 133 ЛГ1, при этом одновибратор 46 настроен на формирование импульса, длите.чьность которого определяет про- лолжительиогть .ч-о цикла записи, pniiiioi-.i чля примененных ИМС памяти 130 ПС, ,ч .. 1|.,ииПр,чтор 49 настро- vi: ita )r-:Mf:i Mi.-i iiiie HMnyniCa записи.

длительность которого для ИМС 505РУ6 должна быть рДвна 400 не.

Коммутатор 56 построен на ИМС 585 АЛ 16, представляющих собой шинные приемопередатчики с двунаправленной структурой.

Коммутатор 43 (фиг. 3) реализован также на ИМС 585 АЛ 16, представляю- njiix собой двунаправленные шинные формирователи с тремя устойчивыми состояниями входов-выходов.

Устройство работает следующим образом.

)5 Режим записи информации. Со входа 54 устройства поступает сигнал ЗАПИСЬ, который подготавливает его для прохождения сигналов с внешнего информационного входа-выхода 53 уст20 ройства на второй информационный вход-выход коммутатора 56, Одновременно сигнал ЗАПИСЬ поступает через элемент ИЛИ 50 на входы 27 блоков 36 подготавливая их для записи информа25 ции. Таким образом, в адресном цикле записи код адреса поступает на информационный вход регистра 37 и через коммутатор 43 и соответствующие информационные входы-выходы 26

30 блоков 36 на их схемы 29 сравнения, Каждый код адреса записывает,ся в регистр 37 по фронту сигнала строба адреса, поступающего со входа 55 устройства на вход синхронизации регистра 37, с выхода которого код адреса записи поступает на вход дешифратора 39, который в случае соответствия этого кода коду номера данного устройства формирует на своем первом выходе сигнал, поступающий на вход синхронизации регистра 38, который разрешает запись в него информации, поступающей на его информационный вход в цикле записи со второго информационного входа-выхода коммутатора 56 и представляющей собой (фиг, 2а код адреса (его старшие разряды страницы памяти блока 41 памяти, в которой хранится псевдопостоянная информация, подлежащая выводу на полиэкран, образованный экранами блоков 36, оси графиков, трафаретов, и т.д.).

35

40

45

50

55

Код адреса страницы поступает с первого выхода регистра 38 на вход старших разрядов адреса, т.е. адрес страницы блока 41 памяти, выбирая тем самым пу-А(ную страницу памяти, в которой хранится псевдопостоянная информация, подлежащая выводу на экраны.

Одновременно с этим сигнал с первого выхода дешифратора 39 поступает на вход установки триггера 40, при этом сигнал высокого уровня с его прямого выхода поступает на первый вход элемента И 44, разрешая прохождение импульсов, поступающих с выхода генератора 1 импульсов, на второй вход элемента И 44 и далее с его выхода на вход одновибратора 46, который запускается передним фронтом импульса и формирует импульс отрицательной полярности длительностью, равной дли- тельности адресного цикла записи.

Импульс с выхода одновибратора 46 поступает на управляющий вход коммутатора 42, обеспечивая тем самым прохождение кода адреса, поступающего с выхода счетчика 47, на коммутатор 43 и на информационные входы-выходы 26 блоков 36. Одновременно импульс стро- бирования адреса с выхода одновибратора 46 поступает на первый вход вто- рого элемента ИЛИ 51 и с его выхода поступает на входы 27 всех блоков 36, осуществляя тем самым стробирование кода адреса, поступающего на информационные входы-выходы 26 блоков 36. Одновременно код адреса поступает на первые входы третьих схем 29 сравнения блоков 36, на вторые входы которых с соответствующих выходов 52 блока регистров поступают коды зоны ад- ресов соответствующих блоков 36.

В блок 2 коды зоны адресов поступают со второго выхода бло.ка 41 памяти, стробируемого импульсом записи, поступающим на вход синхронизации блока 52 со второго выхода дешифратора 39, Второй выход блока 41 памяти объединен по ПРОВОДНОМУ ИЛИ со вторым информационным входом-выходом коммутатора 56, который переводится в третье (отключенное) состояние сигналом, поступающим с прямого выхода триггера 40 на вход управления выдачей коммутаторов 56 на весь период записи псевдопостоянной информации в блоки 36, начиная с момента декодирования адреса страницы псевдопостоянной информации дещифратором 39,

При совпадении кода зоны адресов и текущего адреса осуществляется за- пись кода адреса в регистры 15 блоков 36. По окончании адресного цикла записи псевдопостоянной информации, длительность которого определяется

настройкой одновибратора 46, полярность сигнала на управляющем входе коммутатора 42 изменяется на противоположную, тем самым коммутатор 42 запрещает прохождение на информационный вход коммутатора 43 кода адреса записи и разрешает прохождение информационного слова псевдопостоянной информации (фиг. 26), поступающей с первого выхода блока 41 памяти на второй информационный вход коммутатора 42 и с его выхода через коммутатор 43 на информационные входы-выходы 26 блоков 36.

Одновременно импульс с выхода элемента И. 44, задержанный элементом 48 задержки для получения требуемого временного расположения сигнала записи в блоки 16 памяти, запускает од- новибратор 49, формирующий сигнал записи, который с его выхода через элемент ИЛИ 50 поступает на входы 27 блоков 36 и осуществляет запись в блоки 16 памяти блоков 36 моноэкранов псевдопостоянной информации, поступающей с информационных входов-выходов 26 блоков 36.

Процесс записи в блоки 36 псевдопостоянной информации циклически повторяется до полного вывода содержимого страницы блока 41 памяти, объем которой определяется разрядностью счетчика 47 и кодом объема страницы псевдопостоянной информации,поступающим со второго выхода регистра 38 на первый вход схемы 45 сравнения и представляющим собой младшие разряды служебного информационного слова (фиг. 2а), хранящегося в регистре 38,

На второй вход схемы 45 сравнения со второго выхода счетчика 47 поступает текущий адрес записи страницы, При совпадении текущего адреса записи с кодом объема страницы на выходе схемы 45 сравнения формируется сигнал, поступающий на вход сброса триггера 40 и возвращающий его в состояние О, при этом сигнал высокого уровня с инверсного вькода триггера 40 поступает на вход разрешения выборки блока 41 памяти, запрещая его работу. Одновременно сигнал с выхода схемы 45 сравнения, поступаю- ш;ий на вход сброса счетчика 47 устанавливается в первоначальное состояние, а сигнал с прямого выхода триггера 40 разблокирует коммутатор 56, разрешая тем самым иычислительной

51

системе доступ к блокам 36 моноэкранов для записи в них оперативной визуальной информации.

Работа предлагаемого устройства в режиме воспроизведения проходит по аналогии с описанием работы блока 36,

Формула изобретения

Устройство для вывода отображаемой информации, содержащее два коммутатора, два регистра, блок регистров, первый и второй информационные входы-выходы первого коммутатора соединены с первым информационньм входом-выходом устройства и с информационным входом первого регистра, отличающееся тем, что, с целью увеличения пропускной способности устройства за счет исключения передачи псевдопостоянной отображаемой информации, в него введены блок памяти, третий коммутатор, дешифратор, счетчик, триггер, схема сравнения, элемент И, два элемента ИЛИ, два одновибратора и элемент задержки, второй информационный вход-выход первого коммутатора соединен с информационными входами второго регистра, блока регистров и с первым информационным входом-выходом второго коммутатора, второй информационный вход- выход которого является вторым информационным входом-выходом устройства, первые выходы первого регистра и счетчика подключены к входам старших и младших разрядов адреса блока памяти, первые выходы счетчика и блока памяти подключены к первому и второму информационным входам третьего коммутатора, выход которого подключен к информационному входу второго коммутатора, второй выход блока памя222526

ти подключен через элемент МОНТ.Ж- НОЕ ИЛИ к информационному входу блока регистров, выходы которого являются выходами задания зоны адреса уст5 ройства, выход второго регистра подключен к входу дешифратора, первый выход которого подключен к входу установки триггера и к входу синхрони- зации первого регистра, второй выход

to которого и второй выход счетчика подключены к первому и второму входам схемы сравнения, выход которой соединен с входами сброса счетчика и триггера, прямой выход которого соединен

5 с первым входом элемента И, с первым управляющим ВХОДОМ первого коммутатора и с управляющим входом второго коммутатора, инверсный выход триггера соединен с входом разрешения вы20 борки блока памяти, выход элемента И подключен к счетному входу счетчика и через первый одновибратор к управляющему входу третьего коммутатора и к первому входу первого элемен 5 та ИЛИ, второй вход которого является входом строба адреса устройства и соединен с входом синхронизации второго регистра, выход элемента И соединен через последовательно включен30 ные элемент задержки и второй одно- вибратор с первым входом второго элемента ИЛИ, второй вход которого является входом задания режима устройства и соединен с вторым управляющим

35 входом первого коммутатора, второй выход дешифратора соединен с входом синхронизации блока регистров , второй вход элемента И и выходы первого и второго элементов ИЛИ являются вхо40 дом синхронизации и выходами сопровождения адреса и признака режима запись-отображение устройства соответственно ,

f)

коды адресов страниц четбертого блока паст.

ff}

текущий код зоны адре- псебдопостоянная

ст.

Упр.

Составитель Л.Ушаков Редактор П.Гереши Техред А.КравчукКорректор М.Демчик

Заказ 2864/44Тираж 672Подписное

ВНИНГ1М Государственно1Ч) комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

11рои: нидственно-по.чиг ра|{)ическое предприятие, г-. Ужгород, ул. Проектная, 4

коды объема страниц псевдопостоянной инМ/1.

H/t.

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для отображения информации | 1984 |

|

SU1226519A2 |

| УСТРОЙСТВО ДЛЯ СБОРА, РЕГИСТРАЦИИ И СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1996 |

|

RU2115163C1 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

SU1825189A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для вывода информации из ЭВМ. Цель изобретения - увеличение пропускной способности устройства за счет исключения передачи псевдопостоянной отображаемой информации. Устройство выводит информацию на группу блоков отображения информации (БОИ), которые позволяют формировать фрагменты изображения для трех соответствующих зон общего поля изображения, и содержит блок памяти, хранящий постранично псевдопостоянную информацию для соответствующих БОИ, коммутаторы, обеспечивающие соответствующее направление передачи, блок регистров, хранящий коды начальных адресов зон для соответствующих БОИ, счетчик, осуществляющий вывод псевдопостоянной информации из блока памяти в БОИ, и элементы управления и временного согласования сигналов. Устройство обеспечивает гибкое задание адресов БОИ за счет оперативной перезаписи их в блоке регистров управляющей ЭВМ, что позволяет распп1рить возможности компоновки изображения, 3 ил. S (Л ел 1О

| Авторское свидетельство СССР № 758129, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления матричным табло | 1975 |

|

SU551636A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-01-08—Подача