Изобретение относится к вычислительной технике и может быть использовано для контроля оператившлх запоминающих устройств.

Известно устройство для контроля оперативной памяти, содержащее первый счетчик, регистр числа и блок управления, подключенные к выходньви шинам устройства, счетный триггер, формирователь, элемент И, основные и дополнительные коммутаторы, второй и третий счетчики l3 .

Недостатке этого устройства является невысокая достоверность контррля.

Наиболее близким техническим решением к изобретению является устройство для контроля блоков оперативной памяти, содержащее блок упраления, регистр числа, элемент И, I первый счетный триггер, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и счетчики 2j .

Недостатком данного устройства является невысокая точность контроля, поскольку оно не выявляет потерю информации в статических запоминающих устройствах при длительной паузе обращения к какому-либо столбцу, а также не позволяет контролиротвать правильность регенерации динамических интегральных схем памятия

Целью изобретения является повышение точности достоверности контроля.

Поставленная цель достигается тем, что устройство дли контроля оперативной памяти, содержащее счетчик, выходы которого являются адресными выходами устройства, вход первого счетчика подключен к выходу первого элемента ЗАПРЕТ, первый вход которого подключен к выходу первого одновибратора, второй вход первого элемента ЗАПРЕТ подключен к первому входу первого одновибра тсв)а и одному из входов информационного регистра, выходы которого являются информационнь та выходами устройства, второй вход первого одновибратора подключен ко входу блока управления, к из входов сумматора и к выходу первого счетного триггед а, вход котрого подключен к соответствующему выходу первого счётчика, выход сумматора подключен к первым управляющим зходам коквлутаторов первой группы, выхода которых подключены к другим входам инфо1 ационного регистра, второй и третий управляющие входы кс «мутаторов первой группы подключены соответственно к прямому и инверсному выходам отаро.го счетного триггера, четвертые входы к(1мутаторов первой группы подключены к выходам соответствующих коммутаторов второй группы, одни и

другие. входы которых подключены j, выходам соответственно второго и третьего счетчиков, входы второго и третьего счетчиков подключены к первому выходу блока управления, вто5 рой и третий выходы которого подключены соответственно к пятому и шестому входам коммутаторов первой группы, четвертый выход блока управления является управляющим выходом устройства, содержит дешифЕ)атор, элементы , элементы ИЛИ, второй Одновибратед и второй элемент ЗАПРЕТ, выход которого подключен ко второму входу первого элемента ЗАП15 PET, первый и второй входы второго элемента ЗАПРЕТ, первый и jBXoaa второго элемента ЗАПРЕТ подвключены соответственно к первс му выходу блока управления и к выходу

Q второго однЬвибратора, вход которого подключен к выходу первого элемента И, первый вход первого элемента И подключен к одному из выходов дешифратора к одному из входов второго элемента И и к установочному входу второго счетного триггера, счетный вход которого подключен к выходу первого элемента ИЛИ, первйй и входы первого элемента ИЛИ подключены соответственно к

выходу второго элемента ЗАПРЕТ и к выходу первого счетного триггера, второй вход первого элемента И подключен к четверТс 1у выходу блока управления, третий вход первого

5 элемента И подключен к соответствующему выходу первого счетчика и другому входу второго элемента И, выход которого подключен к седьмому входу кс «мутаторов первой группы,

0 другие выходы дешифратсчра подаслючены ко входам второго элемента ИЛИ, выход которого подключен к третьему входу первого одновибрато-. ра, входы дешифратора подключены ко

5 второму и третьему выходам блока управления.

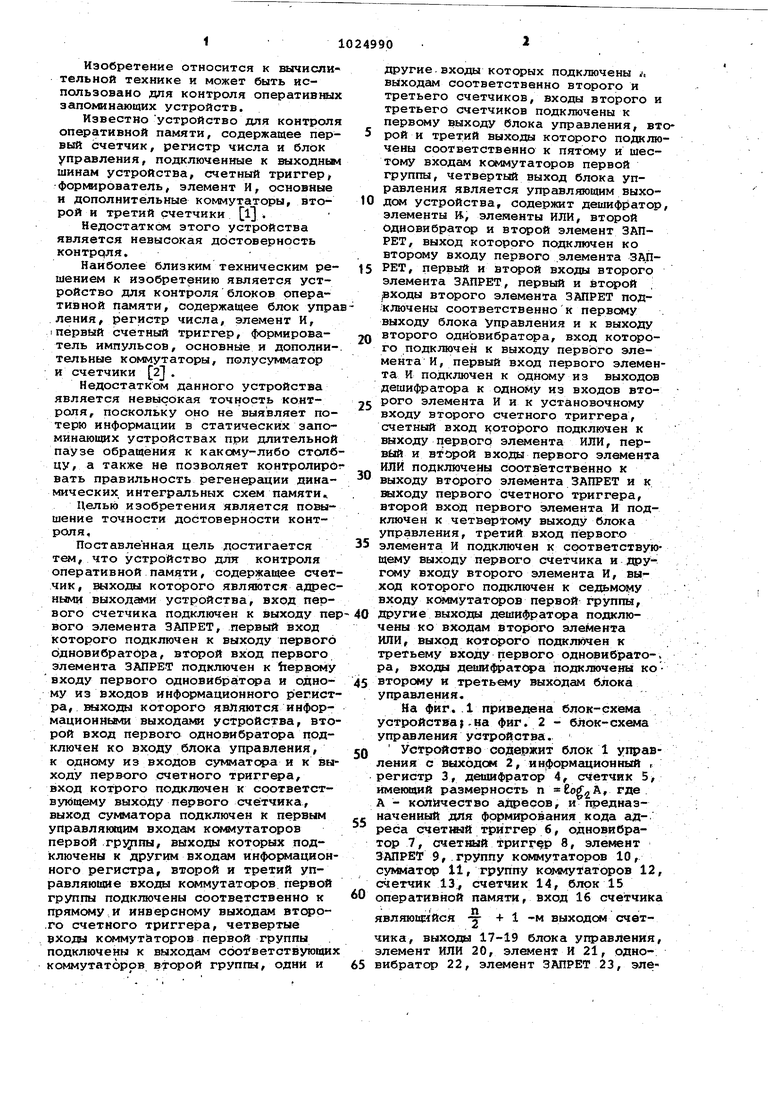

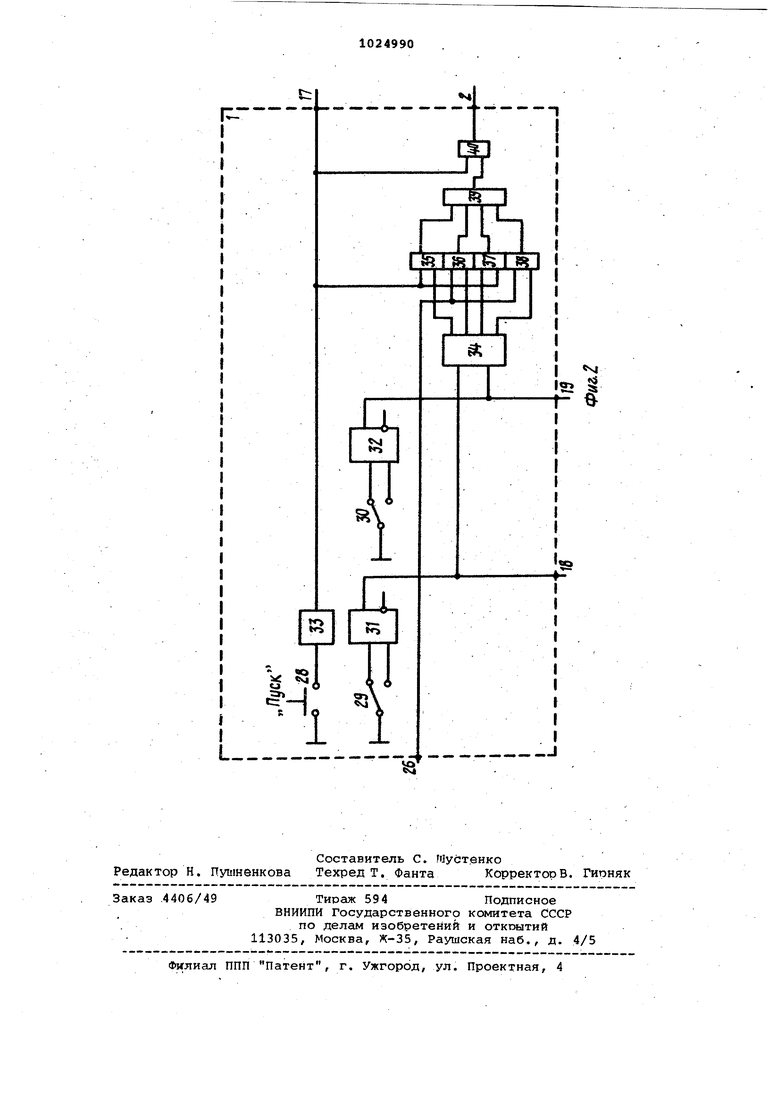

На фиг.. 1 приведена блок-схема устройства г на фиг. 2 - блок-схема управления устрой ства.

0 Устройсзтво содержит блок 1 управления с выхода 2, ин|формационный ,. регистр 3, дешифратор 4, счетчик 5 имекяаий размерность п яе А - количество адресов, и предназ, наченный дяя формирования кода аД ресза счетшай триггер 6, одновибратор 7, счетаай триггер 8, элемент ЗАПРЕТ 9, группу коммутаторов 10, сулматор 11, группу коммутаторов 12, счетчик 13, счетчик 14, блок 15

0 оперативной памяти, вход 16 счетчика

являющ:1йся -у + 1 -м выходом счетчика, выходы 17-19 блока управления, элемент ИЛИ 20, элемент И 21, одно5 вибратор 22, элемент ЗАПРЕТ 23, элемент ИЛИ 24, элемент И 25, входную 26 и выходную 27 шины,

Влок 1 управления содержит кнопку 28, переключатели 29 и 30 кода теста, антйдребезговые тpиггeiзы 31 и 32, генератор 33 тактовых импульсов, в качестве которого может быть использован любой стандартный генератор импульсов, например Г5-48-, дешифратор 34 кода теста, элементы И 35-38, элемент ИЛИ 39, элемент И 40.

Блок управления (фиг. 2) предназначен для выдачи на выходах 18 и 19 с помощью переключателей (или программно) кода выбранного контрольного теста. Выход 2 блЬка 1 управления управляет режимом работы Запись - считывание. Выход 17 предназначен для выдачи тактовой последвательности импульсов. В режимах теста Шахматный код и Адресный код во время нечетных подциклов (сигнал О на выходной шине 26) присходит считывание ин()ормации и импульсы записи на шине 2 не вырабатываются, во время же четных подциклов сигнал 1 на шине 26 разрешает прохождение тактовых импульсов на выходную шину 2 для каждого кода адреса. В качестве дешифратора кода теста 34 может быть ис1юльзован дешифратор 4.

При необходимости переключатели 29 и 30 могут быть заменены любым стандартным устройством ввода. Кулевое состояние двши атсчра 35 является резервнь, и элемент if 36 может остутствовать, поскольку в устройстве реализовано только три типа тестов.,

Одновибратор 7 обеспечивает выделение отрицательного фронта сигНсша.

Счетчик 14 имеет разрядность

п + . :. ; ,.,.

Дешифратор 4 обеспечивает включение или отктночение тех или иных элет ентов в зависимости от выбранного кода.

Элемент И 21, одновибратор 22 и элемент ЗАПРЕТ 23 обеспечивает ббрап1ения к блоку 15 памяти переходе от одного к другому на время, определяемое параметрами одновибратора 22.

Счетный триггер 8 обеспечивает формирование теста типа махматный код.

Счетчики 13 и 14 обеспечивают формирование теста типа Адресный кой. ..

Расолотрим работу устройства в режиме Дождь. Двоичный код на шинах 18 и 19 блока 1 управления через дешифратор 4 обнуляет триггер 8 и блокирует его работу, запирает элемент И 21, а через элемент

ИЛИ 20 разрешает работу одновибратора 7. Этот же код подключает выход сумматора 11 через кокви1утаторы 10 ко входу регистра 3. При этом источником инфорь &ции, записываемой

в регистр 3, является сумматор 11. При нажатии кнопки Пуск в блоке 1 управления начинает вырабатываться тактовая последовательность импульсов, которая поступает на вход счетчиков 13 и 14 и через открытые элементы ЗАПРЕТ 23 и 9 - на вход счетчика 5. В первом подцикле счетчики 5 и 14 работают син:фонно от одних и тех же тактов блока 1. При

этом На входах сумматора 11 код одинаковый, а на его выходе, низкий уровень ф соответствуквций записи кода О по адресам памяти. По окончании первого подцикла.одновибраторсм 7

выделяется задний фронт сигнала с выхода.триггера б, и производится запрет (в элементе 9) одного импульса продвижения в счетчик 5. В результате второй подцикл в счетчике

5 закончится на один такт (равный периоду обращения) позже, чем в счетчике 14, и сумматс«) 11 зафиксирует неравнозначность в конце второго подцикла. Поэтому по втором подцикле во всех адресах памяти,.кроме последнего, будут записаны коды О, а в последнем -. 1. По окончании второго ПОДЦИКЛа точно также произойдет aaitpeT еще одного импульса продвижения 8 счетчмк 5. СоотвеТственно, неравнозначность зафиксируется 9 двух последних адресах третьегоподцикла, куда и будет записан код 1. Таким образом, блок 15 бперативной памяти, заполненный

в первом п одцикле нулями пост епе нно (начиная с.поеледнего ajiQpeca) заполняется в следующих пОдциклах единт ами, т.е. пррисходит процесс набегания единиц, харакТерний для теста Дождь. Когда пройдет А подцвклов, коды на входах сумматора 11 будут инверстош, и блок 15 будет,заполнен единицами. В слйдуюйих подциклах точно /

также, начиная с последнего адреса код единиц смеянтся кодом нулей, 2 А поациклов заканчивается полмьй теста.

Расс ютрим работу устройства при формироваяии теста типа Адресный

кОд, В этом случав управляюиие

сигнал 18 и 1& с блока 1 подключают, к в сояам регистры 3 выходы счетчика 14 (через коммутаторы 12 и 10/. По-прежнему блокирована работа счетного Т1 1ггера 8, закрыт элемент И 21 и разрешна работа одновибратора 7. Работа коммутаторов 10 аналогичных их работе в режиме Дождь за исключениел того, что источником ««

ФО «ации является не сумматор 11,

а счетчик 14, причем счетчики 14 и 5 имеют расхождение по частоте, равА

ное -j . При этом код числа, записываемый в блок 15, меняется с каж дьм адресом. Благодаря наличии коммутаторов 12, управляемых счетчиком

13,обеспечивается подключение к соответствующим разрядам регистра числа 3 различных разрядов счетчика

14.Этим достигается выравнивание динамики работы разных разрядов.

Рассмотрим работу устройства в режиме формирования теста типа Шахматный код. В этсял случае на выходных шинах 18 и 19 блока 1 управления устанавливается код, запрещающий работу одновибратора 7, открывающий элепент И 21 и разрешающий работу счетного триггера 8. Сигналы с выходов 18 и 19 блока 1 .управления

и f 5 1/ -го выхода счетчика 5 {через открытый элемент И 21) пода лючают ко входам регистра числа 3 выходы счетнозто .триггера 8 через коммутатоЕял 10.

При работе с некоторьвли М)ЗП запоминг ощимн устройствами статического типа наблкздается потеря информации в отдельных элементах памяти при длительной паузе обращения к какомулибо столбцу матрицы пгиняти. Для обнаружения потери информации в этот случае при контроле тестем Шахматный код в режиме считывания между столбцами делается пауза длительностью Т per - до 10(с для динамического ЗУ Т per выбирается в соответствии с нсчэмативной документацией) . Эта задержка осуществляется с помощью одновибратора 22 с регулируемой длительностью импульса.

В режиме записи элемент И 21 закрыт сигналом с выхода 2 блока 1 управления. Импульсы с выхода 17 через открытые элементы 23 и, 9 поступают на вход счетчика 5, ас выхода элемента 23 через элемент ИЛИ 24 на счетный вход триггера 8. Во вретля первого такта обращения первого подцикла происходит запись кода О в

первый .адрес блока 15. Затем на выводе счетного триггера 8 появляется 1, и код 1 записывается во второй адрес блока 15. Далее в третий гщрес блока 15 записывается код О. 5 Так продолжается до адреса. Таким образом, первая строка первого каНсша блока 15 заполнена перемё-. жающимися единицами и нулями, ПосQ.

Q ле заполнения 2 адресов на , +

выходе первого счетчика 5 устанавливается уровень логической 1, который через открытый элемент И 25 поступает на один из управляющих входов

5 коммутатора 10, разрешая тем самым прохождение в следующие тактов обращения сигнала с Инверсного выхода триггера 8 на входы регистра 3. В течение первого подцИкла записи

0 каждалй канал блока 15 будет заполнен шахматньам кодом. В режиме считывания на выхрдё 2 блока 1 управления устанавливается сигнал 1, который разрешает работу элементу

5 И 21. Поэтому после 2. адресов (обращение ко всем строкам одного столбца) , т.е. при переходе к следующему

столбцу, сигнал с выхода + 1 счетчика 5 через элемент И 21 запускает одновибратор 22, выходной импульс которого запрещает прохождение тактовой последовательности черезэлемент 23 на счетчик 5 и счетный триггер 8. В остальнсад работа происходит так 5 же, как и при записи. При этом проверяется сохранность информации в блоке 15 памяти. Во время второго записи в блок 15 будет записан инверсный Шахматный код, 0 правильность записи и сохранность информации котсч ого проверяется во время второго считывания.

Преимущество предложенного устройства заключается в более высокой, по сравнению с известными устройствами, точности контроля статических ЗУ, а также в расширении области применения за счет возможности контроля динамических ЗУ.

«SI

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля оперативной памяти | 1980 |

|

SU955208A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Устройство для отладки мультипрограммных систем | 1989 |

|

SU1735855A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ .ОПЕРАТИВНОЙ ПАМЯТИ, содержамее первый счетчик, выходы которого ЯВЛЯ-, ются адресными выхода и устройства, вход первого счетчика подключен к выходу первого эелемента ЗАПРЕТ, первый вход которого подключен к выходу.первого одновибратора, второй вход первого элемента ЗАПРЕТ подключен к первому входу первого одновибратора и к одному из входов информационного регистра, выходы которого являются информационными выходами устройства, второй вход первого одновибрато ра подключен ко входу блока управления, к одному из входов сумматора и к выходу первого счетного триггера, вход которого подключен к соответствующему выходу первого счетчика, выход сумматора подкгаочен к первым управляющим входам коммутаторов первой группы, выходы которых подключены к другим входам информационного регист. ра, в торой и третий управляющие входы коммутаторов первой группы под-, ключены соответственно к прямому и инверсному выходам второго счетного триггера, четвертые входы коммутаторов первой группы подключены к . выходам соответствующих коммутатоpolB. второй группы, одни и другие входы которых подключены к выходам соответственно второго и третьего счетчиков, входы второго и третьеГб счетчиков подключены к первому выходу блока управления, второй и третий выходы которого подключены соответственно к пятому и шестсму входам кокмутаторов первой группы, четвертый выход блока управления является управляющим выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно содержит дешифратор, элементы И, элементы ИЛИ, второй одновибратор и второй элемент ЗАПРЕТ, выход которого подключен ко второму входу первого элемента ЗАПРЕТ, первый и втсдаой входы второго элемента ЗАПРЕТ подключены соответственно к первому выходу блока управления и к выходу второго одновиб: ратод а, вход которого подключен к выходу первого элемента И, первый вход первого элемента И подключен к одному из выходов дешифратора, к одному из входов элемента И и к установочному входу второго счетного Триггера, счетный вход коto jToporo подколочен к выходу первого 4 элемента ИЛИ, первый и второй входы первого элемента ИЛИ подключены соСО ответственно к выходу второго элемента ЗАПРЕТ и к выходу первого счетного триггера, второй вход первого элемента И подключен к четвертому выходу блока управления, третий вход первого элемента И подключен к соответствующему выходу первого счетчика и другому входу второго элемента И, выход которого подключен к седьмому входу коммутаторов rpynru, другие выходы дешифратора подключены ко входам второго элемента ИЛИ, выход которого подклочен к третьему входу первого одновибратора, вхоф дешифратора подключены ко-второму и третьему выходам блока управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 2988371/18-24, кл G 11 С 29/00, 1980 (прототип). | |||

Авторы

Даты

1983-06-23—Публикация

1982-02-05—Подача