Изобретение относится к электросвязи, а именно к обнаружению и коитролю ошибок в закодированной информации в телеграфии.

Известные устройства для оценки качества сигиала при приеме передач частотной телеграфии, содержащие входиой блок с сумматором, блоки оценки качества сигналов, блок формирования кодовых сигналов, характеризуются невысокой вероятностью обнаружения ошибочно принятых кодовых симоволов, а также низкой достоверностью обнаружения кодовых комбииаций.

Цель изобретения - повышение вероятности обнаружения ошибочно иринятых кодовых символов, а также обнаружение кодовых комбинаций низкой достоверности.

Для этого в предлагаемом устройстве сумматор входного блока включен параллельно интегратору, выход интегратора подключен через второй квадратор к управляемому усилителю и соединен с блоком вычитания. На выходе последнего подключен интегратор средних значений квадрата огибаюшей сигнала, причем к входу последнего подсоединен второй квадрат. Выход усилителя подключен через коммутатор к входам амплитудных селекторов, а выход последних подключен к счетчику, соединенному через дешифраторы состояния счетчика с кодопреобразователем.

Достоверность принимаемого сигнала оценивается поэлементно путем нзмерения для каждого элементарного сигнала «весового коэффициента

(.2

Z,- -

где - квадрат оценки среднего значения амплитуды демоду.тированиого элементарного сигнала на временном интервале т (здесь т - интервал усреднения, Т - длительность элементарного сигнала);

- оценка дисперсии амплитуды сигнала на временном интервале т. Параметр L- , измеренный таким образом, является коэффициентом достоверности.

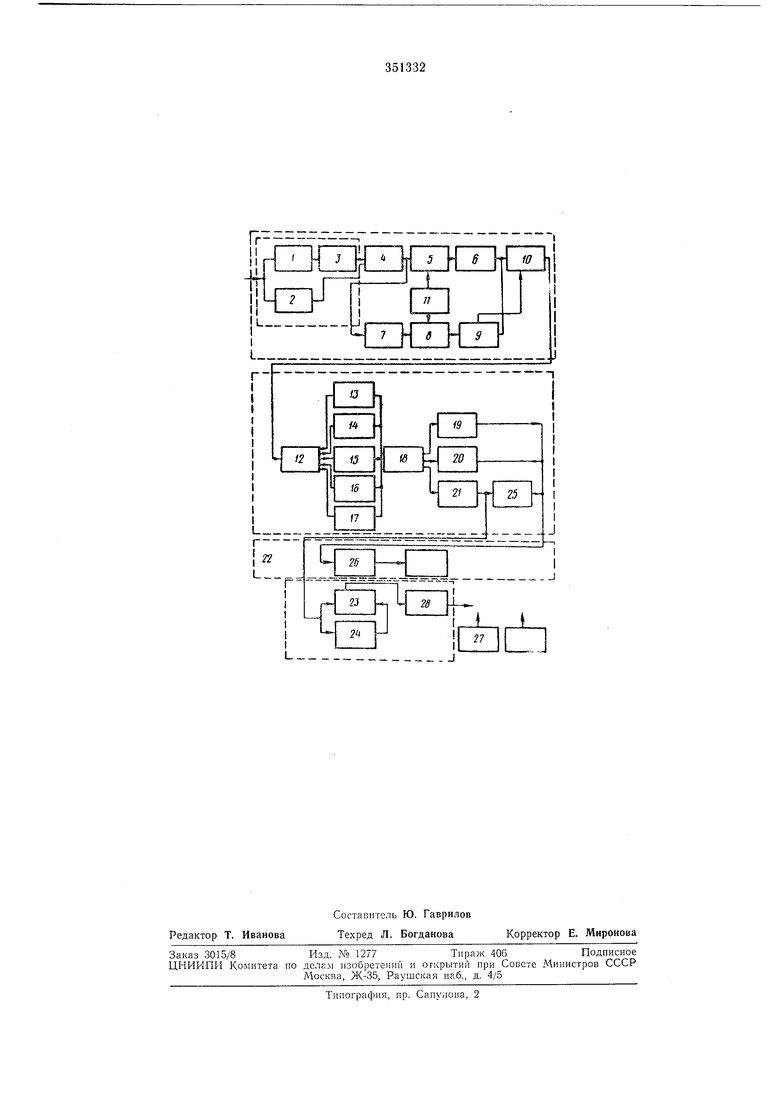

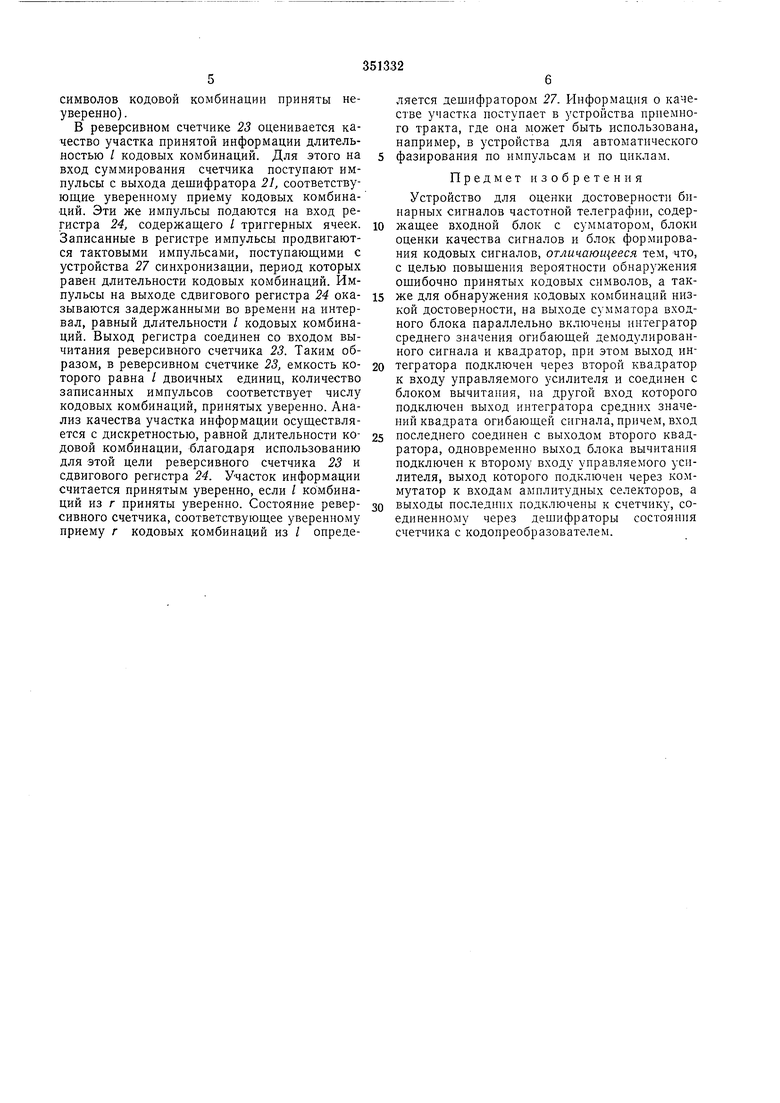

Па чертеже изображеиа блок-схема нредлагаемого устройства.

Сигнал двух полярностей с дифференциальной нагрузки квадратичиых детекторов каналовыделяющего апнарата поступает на диодные ограничители / и 2. Диодный ограничитель У имеет нулевой порог и производит ограничение отрицательных значений видеосигнала (ограничитель снизу). Диодный ограничитель 2 осундествляет ограничение при нулевом пороге положительных значений видеосигнала (ограничитель сверху). В фэзоинверторе 3 происходит поворот на 180° фазы сигнала, поступающего с ограничителя /. Сигналы, приведенные к одной полярности, складываются в сумматоре 4 н после сложения поступают на интегратор 5 и квадратор 6. В интеграторе для каждого элементарного сигнала вычисляется оценка среднего значения принятой реализации элементарного сигнала S (т) на интервале т. Процесс управления работой интегратора (подача напряжения на интегратор на время т и разряд интегратора перед началом следующего цикла) осуществляется устройством 7 управления. С выхода интегратора 5 напряжение поступает на интеграторе 8, в котором в процессе интегрирования значения напряжения возводятся в квадрат. Квадратор 6 возводит в квадрат значения напряжения сигнала, поступающего с сумматора 4. С выхода квадратора 6 сигнал поступает на интегратор 8, где производится вычисление оценки среднего значения квадрата амплитуды элементарного сигнала. Выходы квадратора 6 и интегратора 8 подключены к блоку 9 вычитания, где происходит вычитание напряжений, вычисленных квадратором 6 и интегратором 8. Разностное напряжение в моменты окончания интегрирования сигналов интеграторами 5 и S является оценкой дисперсии реализации элементарного сигнала. Напряжение с выхода квадратора 6 поступает на управляемый усилитель 10. Устройство 11 управляет интеграторами 5 и 5. Управление коэ-ффициентом усиления усилителя осуществляет напряжение, поступающее с блока 5.: В моменты окончания процесса интегрирования сигналов интеграторами 5 и S величина напряжения на выходе управляемого усилителя пропорЦиональна величине коэффициента достоверности f/, /Г, макс с S Выход управляемого усилителя 10 соединяется с коммутатором 12, который производит поочередное подключение через интервалы времени, равные длительности элементарных сигналов, напряжения с выхода управляемого усилителя 10 на входы амплитудных селекторов 13-17 в моменты окончания интегрирования. Селектор 13 служит для оценки достоверности первого элементарного сигнала, селектор 14 - второго и т. д., селектор 17 - пятого элементарного сигнала. Амплитудные селекторы находятся в закрытом состоянии, если уровень напряжения, поступающего с управляемого усилителя U-. t/o. где t/o величина напряжения, соответствующая пороговому значению коэффициента достоверности . Если , селектор, который в данный момент подключен к выходу управляемого усилителя, переходит в открытое состояние, при этом на счетчик 18, подключенный к выходам селекторов, поступает импульс. После отключения коммутатором входного напряжения амплитудный селектор возвращается в исходное состояние. Таким образом,, за один цикл работы коммутатора, равный длительности кодовой комбинации, на вход счетчика 18, емкость которого должна быть п двоичных единиц, поступает определенное число импульсов с выходов амплитудных селекторов. Достоверность кодовой комбинации тем выше, чем большее количество импульсов поступает на вход счетчика 18. Степень достоверности кодовой комбинации оценивается К-/ дешифраторами состояния счетчика 18. По схеме, изображенной на чертеже, достоверность кодовой комбинации оценивается четырьмя градациями качества (К-4). Дешифраторы 19, 20, 21 подключены к счетчику 18 таким образом, что импульс на выходе дешифратора 19 появляется при поступлении на вход счетчика п-2 импульсов, т. е. появление импульса на выходе дешифратора 19 (при отсутствии импульсов с дешифраторов 20 и 21) соответствует неуверенному приему двух кодовых символов анализируемой комбинации. Появление импульса на выходе дешифратора 20 (при отсутствии импульса с дешифратора 21) соответствует неуверенному приему одного символа кодовой комбинации. Импульс на выходе дешифратора 21 появляется при полном заполнении счетчика, что соответствует уверенному приему всех п символов кодовой комбинации. При поступлении на вход счетчика 18 менее п-2 импульсов, на выходах дешифраторов 19, 20 и 21 импульсы будут отсутствовать, что соответствует неуверенному приему более двух символов кодовой комбинации. |По окончании цикла оценки достоверности кодовой комбинации счетчик 18 сбрасывается в исходное состояние. , Выходы дешифраторов 19 и 20 соединены с блоком 22 формирования кодовых сигналов, соответствующих различным степеням достоверности кодовой комбинации. Выход дешифратора 21 соединен с реверсивным счетчиком 23, сдвиговым регистром 24 и через развязывающую цепь 25 с кодопреобразователем 26. Последний формирует следующие двухзначные кодовые сигналы: появлении импульса на выходе дешифратора 21 (уверенный прием всех символов кодовой комбинации); «01 - при появлении импульса на выходе дещифратора 20 и отсутствии импульса с дешифратора 21 (один из символов кодовой комбинации принят неуверенно); «01 - при повлении импульса на выходе дещифратора 19 и отсутствии импульсов с дешифраторов 20 и 1 (два символа кодовой комбинации приняты еуверенно): «11 - при отсутствии импульов на выходах дешифраторов (более двух

символов кодовой комбинации приняты неуверенно) .

В реверсивном счетчике 23 оценивается качество участка принятой информации длительностью / кодовых комбинаций. Для этого на вход суммирования счетчика поступают импульсы с выхода дешифратора 21, соответствующие уверенному приему кодовых комбинаций. Эти же импульсы подаются на вход регистра 24, содержащего / триггерных ячеек, Записанные в регистре импульсы продвигаются тактовыми импульсами, поступающими с устройства 27 синхронизации, период которых равен длительности кодовых комбинаций. Импульсы на выходе сдвигового регистра 24 оказываются задержанными во времени на интервал, равный длительности / кодовых комбинаций. Выход регистра соединен со входом вычитания реверсивного счетчика 23. Таким образом, в реверсивном счетчике 23, емкость которого равна / двоичных единиц, количество записанных импульсов соответствует числу кодовых комбинаций, принятых уверенно. Анализ качества участка информации осуществляется с дискретностью, равной длительности кодовой комбинации, благодаря использованию для этой цели реверсивного счетчика 23 и сдвигового регистра 24. Участок информации считается принятым уверенно, если / комбинаций из г приняты уверенно. Состояние реверсивного счетчика, соответствующее уверенному приему г кодовых комбинаций из / определяется дешифратором 27. Информация о качестве участка поступает в устройства приемного тракта, где она может быть использована, например, в устройства для автоматического фазирования по импульсам и по циклам.

Предмет изобретения

Устройство для оценки достоверности бинарных сигналов частотной телеграфии, содержащее входной блок с сумматором, блоки оценки качества сигналов и блок формирования кодовых сигналов, отличающееся тем, что, с целью повыщения вероятности обнаружения ошибочно принятых кодовых символов, а также для обнаружения кодовых комбинаций низкой достоверности, на выходе сумматора в.ходного блока параллельно включены интегратор среднего значения огибаюшей демодулированного сигнала и квадратор, при этом выход интегратора подключен через второй квадратор к входу управляемого усилителя и соединен с блоком вычитания, на другой вход которого подключен выход интегратора средних значений квадрата огибающей сигнала, причем, вход последнего соединен с выходом второго квадратора, одновременно выход блока вычитания подключен к второму входу управляемого усилителя, выход которого подключен через коммутатор к входам амплитудных селекторов, а выходы последних подключены к счетчику, соединенному через дешифраторы состояния счетчика с кодопреобразователем.

.nnr

10

. J

. J

| название | год | авторы | номер документа |

|---|---|---|---|

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Устройство контроля качества дискретных каналов связи с переменными параметрами | 1982 |

|

SU1072270A1 |

| Многоканальное устройство функционального контроля | 1988 |

|

SU1596311A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Анализатор спектра | 1985 |

|

SU1345132A1 |

| Многоканальный приемник с кодовым разделением каналов для приема квадратурно-модулированных сигналов повышенной структурной скрытности | 2016 |

|

RU2610836C1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

| Устройство для оценки неоднородности дисперсии случайных процессов | 1990 |

|

SU1764066A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

Даты

1972-01-01—Публикация