и второй выходы генератора соединены с первьми входами соответственно первого и второго умножителей, выходы которых соединены с первыми входами соответственно первого и второго интеграторов, выходы которых соединены соответственно с первым и вторьм входами вычитателя, вторые входы первого и второго умножителей объединены и являются первым входом демодулятора, вход генератора является вторьм входом демодулятора, вторые входы первого и второго интеграторов объединены и являются третьим входом демодулятора, выход вычитателя является выходом демодулятора.

3. Устройство по п. 1, отличающееся тем, что блок управления содержит генераторы импульсов, элементы задержки, элементы ИЛИ формирователи импульсов, триггер и счетчик, выход первого генератора импульсов через последовательно соедненные первый и второй элементы задержки соединен с входами первого фомирователя импульсов, третьего элемента задержки и первым входом первого элемента ИЛИ, выход третьего элемента задержки соединен с первым входом второго элемента ИЛИ и через четвертый элемент задержки - с входами второго формирователя имтхульсов и пятого эл-емента задержки, выход пятого элемента задержки соединен с вторым входом второго элемента ИЛИ, первым входом третьего элемента ИЛИ и через шестой элемент задержки - с вторым входом третьего элемента ИЛИ и входом седьмого элемента задержки, выход седьмого элемента задержки соединен с вторым входом первого элемента ИЛИ и с входом восьмого элемента задержки, выход восьмого элемента задержки соединен через девятый элемент задержки с третьим входом третьего элемента ИЛИ и с входом десятого элемента задержки, выход десятого элемента за держки соединен с первым входом четвертого элемента ИЛИ, выход третьего элемента ИЛИ соединен с первым входо триггера, выход которого через второй генератор импульсов соединен с входом счетчика, выход счетчика соединен с вторым входом триггера, вход первого генератора импульсов и второй вход четвертого элемента ИЛИ являются соответственно первым и вторым входами блока управления, выходы первого генератора импульсов, первого элемента задержки, первого элемента ИЛИ,,второго элемента ИЛИ, второго генератора импульсов, восьмого элемента задержки, первого формирователя импульсов, второго элемента задержки, второго формирователя импуль-сов и четвертого элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым и десять1м входами блока управления,

4,Устройство по п. 1, отличающееся тем. Что решающий блок содержит генератор, элемент ИЛИ элементы сравнения и ключи, выход генератора соединен с первыми входами элементов сравнения, выходы которых соединены соответственно с первыми входами ключей и входами элемента ИЛИ, выход элемента ИЛИ соединен с первым входом генератора и вторыми входами ключей, вторые входы элементов сравнения являются первыми входами решающего блока, второй вход генератора является вторым входом решающего блока, выходы ключей являютс выходами решающего блока.

5,Устройство по п. 1, отличающееся тем, что формирователь управляющих сигналов содержит умножители, сумматоры и вычитатель, выходы первых и вторых умножителей соединены с первыми входами соответственно первого и второго сумматоров, выходы которых соединены соответственно с первым и вторым входами вычитателя, первые входы rtepвых и вторых умножителей являются соответственно первыми и вторыми входами формирователя управляющих сигналов, вторые входы первых умножителей объединены соответственно с вторыми входами вторых умножителей

и являются третьими входами формирователя управляющих сигналов, вторые входы первого и второго сумматоров объединены и являются четвертым входом формирователя управляющих сигналов, выход вычитателя

является выходом формирователя управляющих сигналов,

6,Устройство по п. 1, отличающееся тем, что блок регистров содержит регистры, ключи

и элемент ИЛИ|. выход первого регистра соединен с первыми входами первого ключа и второго регистра, выход

второго регистра соединен с первым входом второго ключа, выходы первого и второго ключей соединены с соответствующими первым и вторым входами элемента ИЛИ, первый вход первого ключа является первым входом блока регистров, вторые входы первого и второго ключей объединены и

107146

являются вторым входом блока регистров, вторые входы первого и второго регистров объединены и являются третьим входом блока регистров, вьосоды второго регистра, элемента ИЛИ и первого регистра являются соответственно первыми, вторым и третьими выходами блока регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для приема и обработки избыточной информации | 1983 |

|

SU1140141A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1985 |

|

SU1282184A1 |

1..УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее демодулятор, первый вход которого является входом устройства, выход демодулятора соединен с первьм входом блока памяти, выходы которого соединены с соответствующими первыми входами решающего блока, выходы решающего блока соединены с соответствующими первыми входами блока сумматоров, вторые входы которого подключены к соответствующим выходам первого регистра, первый декодер, первый выход которого соединен с первым входом первого элемента ИЛИ, второй вь1ход - с. первыми входами первого регистра и второго декодера, выход второго декодера соединен с первым входом блока регистров, первые выходы и второй вход которого соединены соответственно с первыми входами и выходом формирователя управляющих сигналов, второй выход блока регистров соединен с вторьм входом первого элемента ИЛИ, выход которого является выходом устройства, пороговый селектор, отличающееся тем, что, с целью повьшения достоверности принимаемой информации, в него введены второй регистр, блок управления и второй элемент ИЛИ, первые входы второго регистра подключены к соответствующим выходам блока сумматоров, выход соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом первого декодера, выход демодулятора подключен через пороговый селектор к второму входу второго элемента ИЛИ, вторые входы формирователя управляющих сигналов W подключены к соответствующим третьим выходам блока регистров, третьи входы - к соответствующим выходам блока памяти, первый и второй входы блока управления подключены соответственно к входу устройства и первому выходу первого декодера, первый и второй выходы соединены соответственно с вторым и третьим входами демодулятора, третий выход - с вторым входом блока памяти, четвертый выход - с вто рьм входом второго декодера, пятый вы4 ход - с третьим входом блока регистОд ров, шестой выход - с четвертым входом формирователя управляющих сигналов, седьмой выход - с вторым входом первого регистра, восьмой выход с вторьм входом решающего блока и девятый выход - с вторым входом второго регистра. 2. Устройство по п. 1, отличающееся тем, что Демодулятор содержит умножители, интеграторы, генератор и вычигатель, первый

1

Изобретение относится к электросвязи и может быть использовано в системах передачи информации для приема составных сигналов с избыточностью, использующих длинные и сверхдлинные помехоустойчивые коды.

Известно устройство для приема избыточной информации, содержащее аналоговый демодулятор, первый и второй решающие блоки С1.

Недостатком такого устройства является низкая достоверность приема информации, поскольку в нем недостаточно полно используется аностериорная информация о принятом сложном сигнале с избыточностью.

Известно также устройство для приема дискретной информации, содержащее блок отсчета сигнала, блок сра нения, блок памяти, блок пороговых уровней напряжений, блок опроса и решающий блок С 2Д.

Недостатком данного устройства является ограниченная область функциональных возможностейj так как уст ройство обрабатьгеает ограниченный класс сигналов, формируемых на основ мажоритарно декодируемых кодов.

Наиболее близким к предлагаемому является устройство для приема избыточной информации, содержащее демодулятор, первый код которого является входом устройства, выход демодулятора соединен с входом блока памяти, первые выходы которого соединены через решающий блок ссоответствующими первыми входами блока сумматоров, вторые входы которого подключены к соответствующим выходам .первого регистра, выходы блока сумматоров соединены с соответствующими входами первого декодера, первый выход которого соединен с перв ым входом элемента ИЛИ, вторые выходы - с соответствующими входами второго регистра, выход которого ссзединен с первым входом второго декодера, выход второго декодера соединен с первым входом блока регистров, первый выход второго декодера соединен с первым входом блока регистров, первый выхо которого соединен с вторым входом элемента ИЛИ, вторые выход и вход ; подключены соответственно к первым входу и выходу формирователя управляющих сигналов, второй вход формирователя управляющих сигналов объединен с входом порогового селектора и подключен к второму выходу блока памяти, выход порогового селектора соединен с входом третьего декодера, первый выход которого соединен с входом первогохрегистра и вторым входом второго декодера, второй выход третьего декодера соединен с третьим входом элемента ИЛИ, выход которого является выходом устройства СЗ.

Недостатком известного устройства является низкая достоверность приема информации.

Цель изобретения - повышение достоверности принимаемой информаци

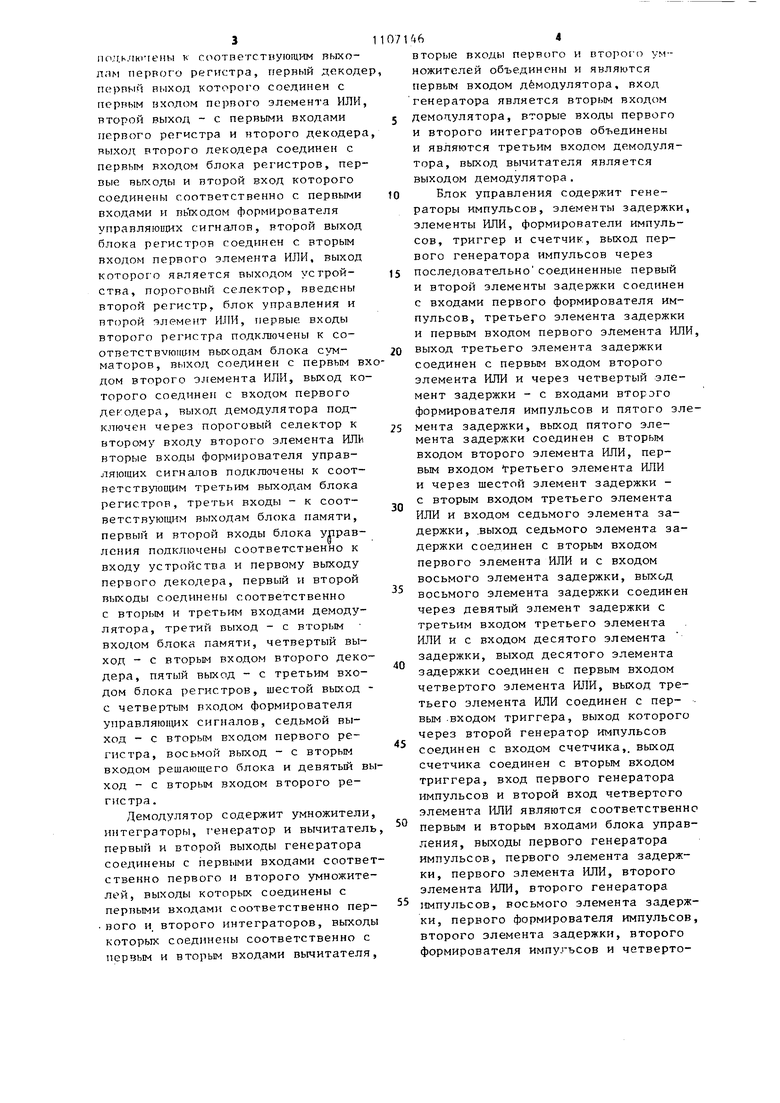

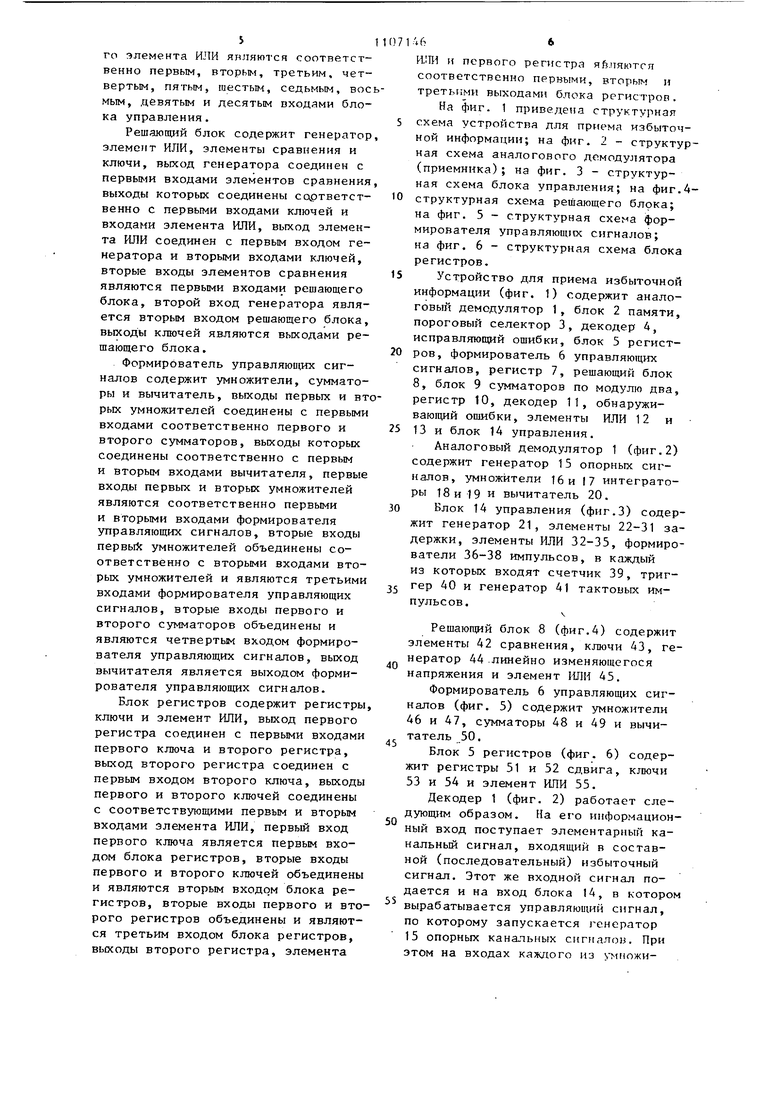

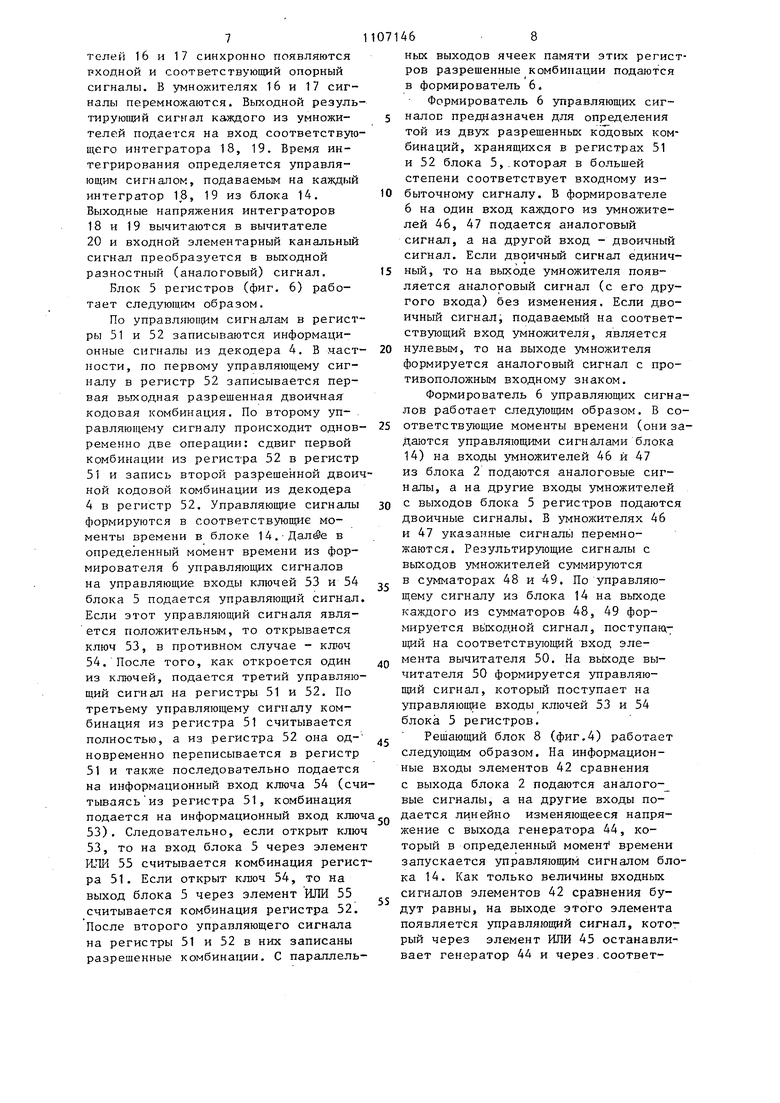

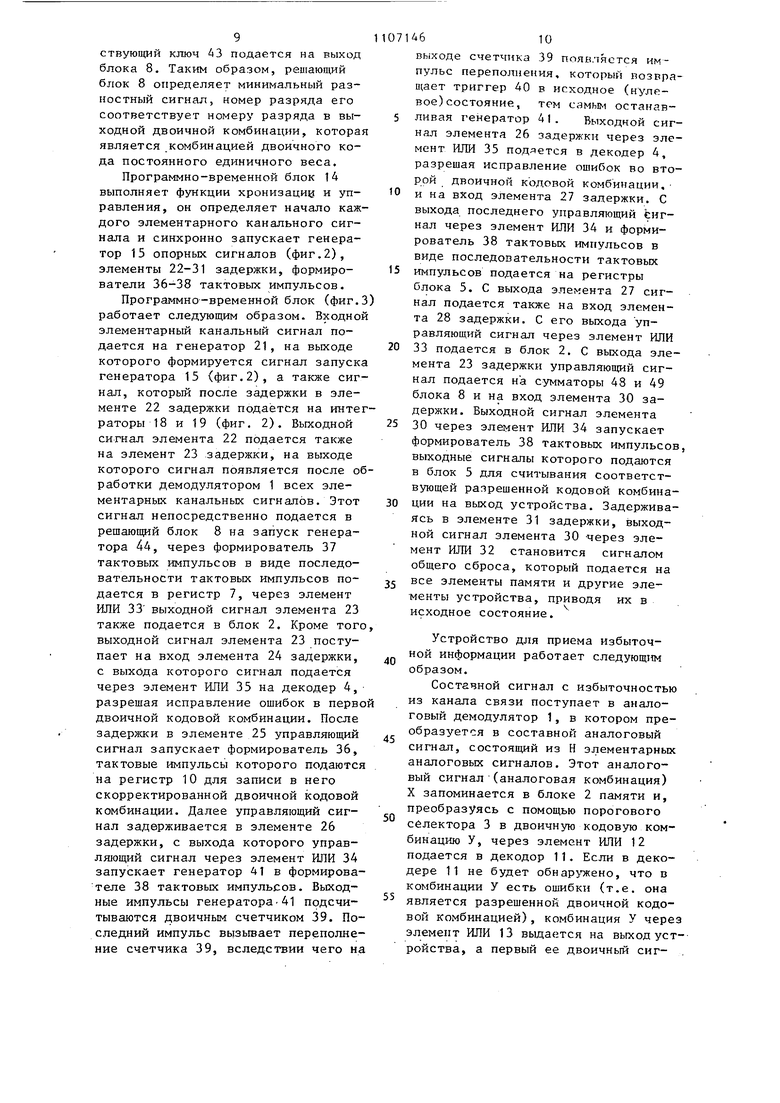

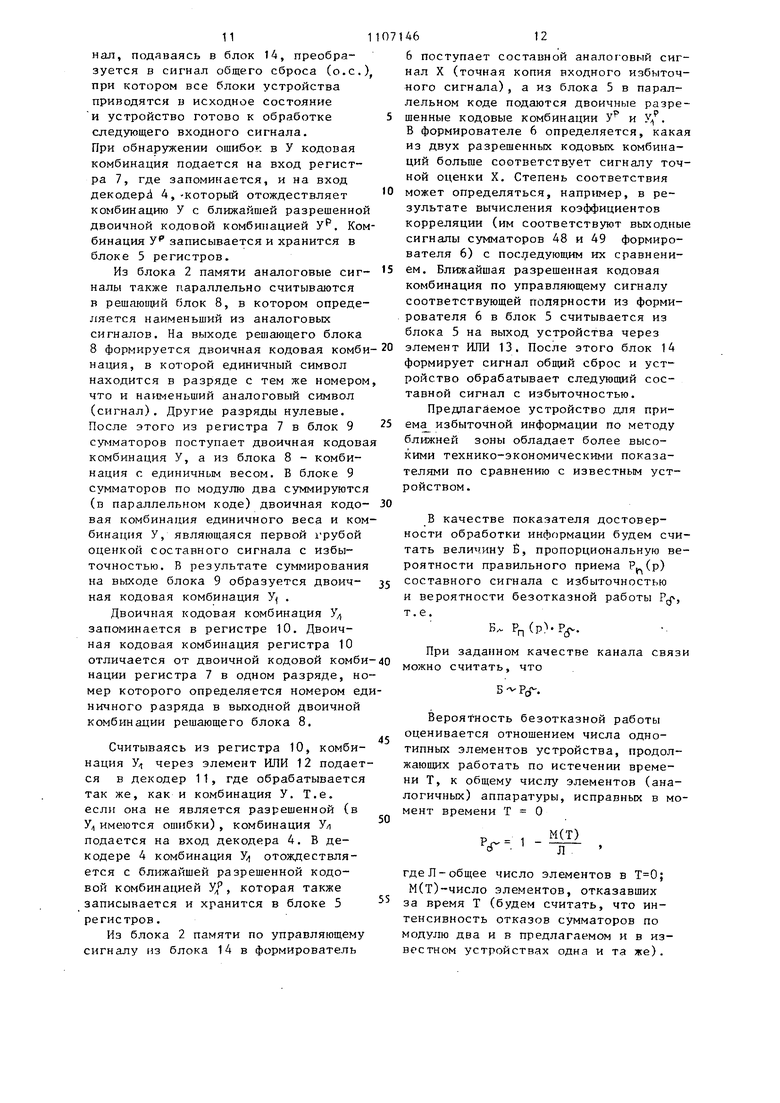

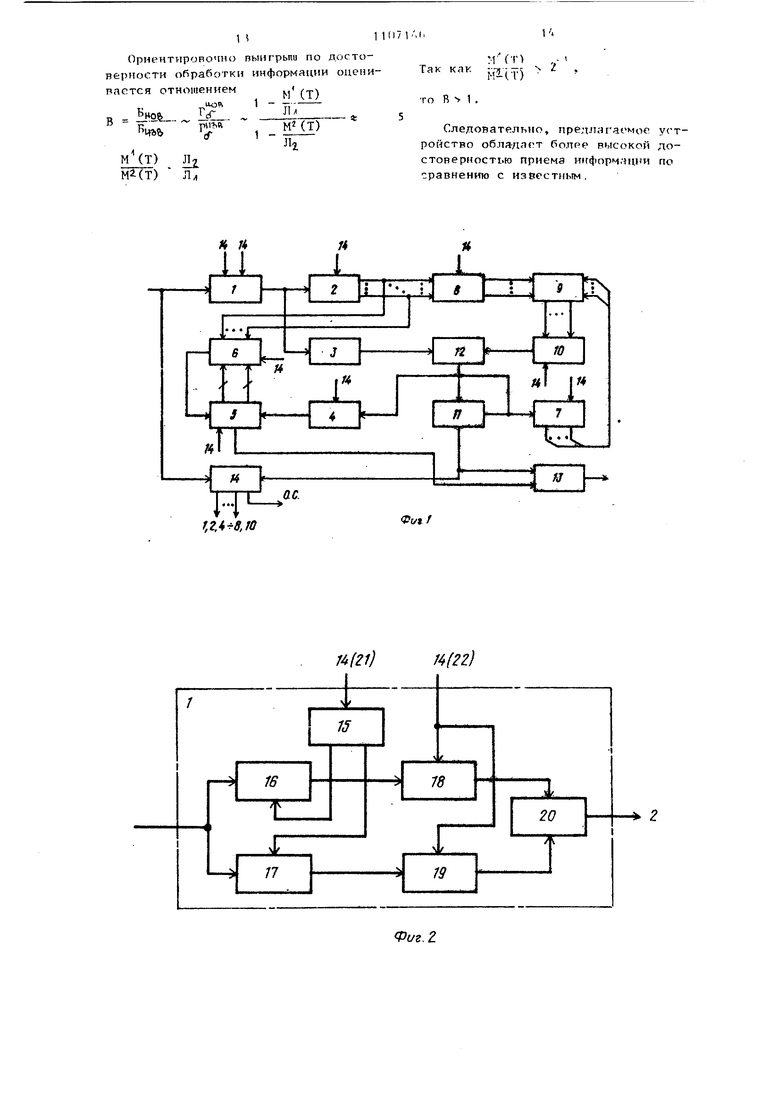

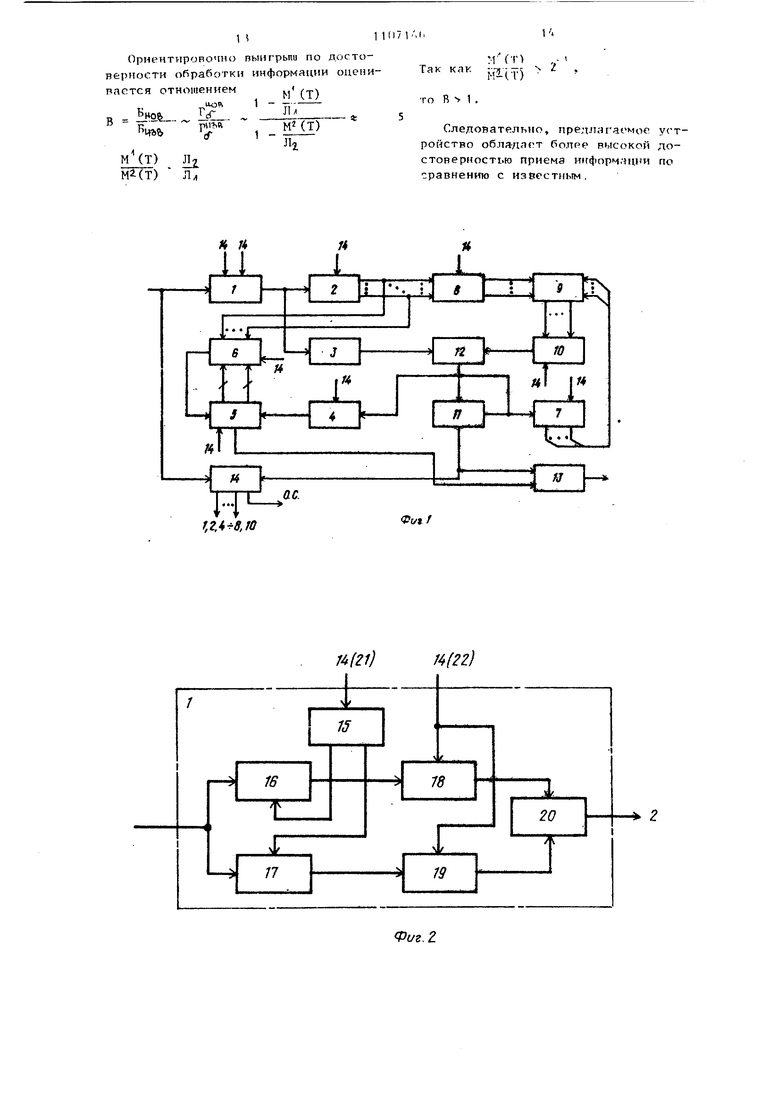

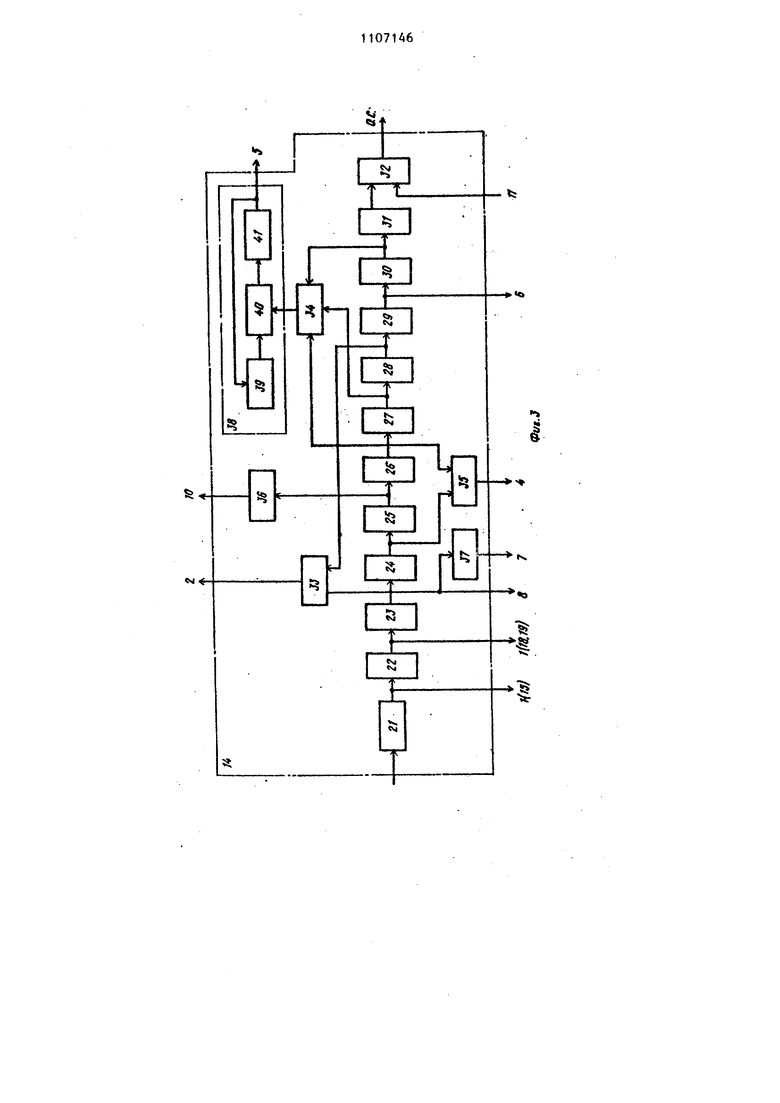

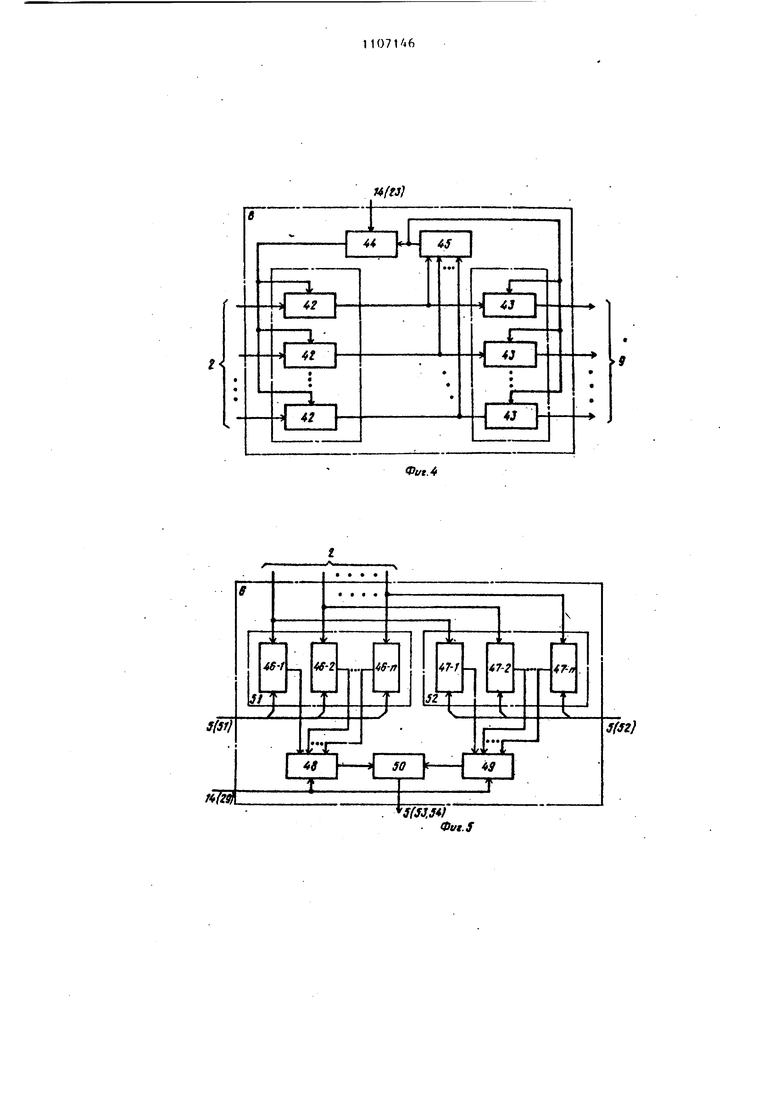

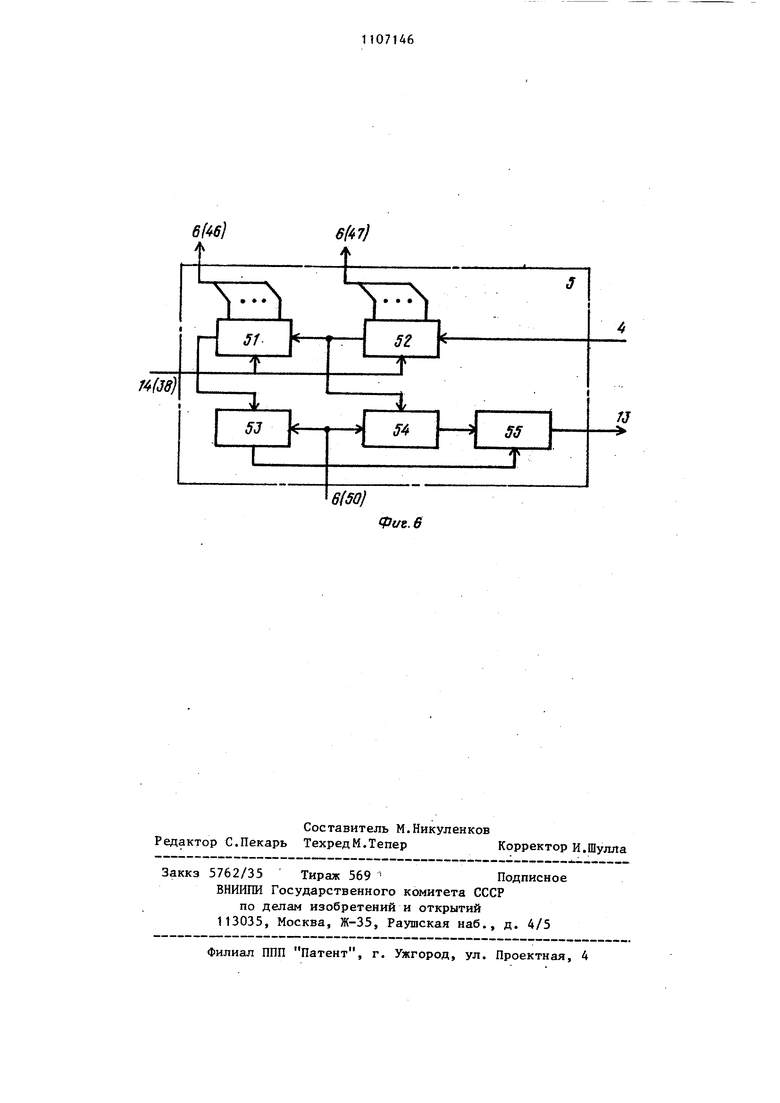

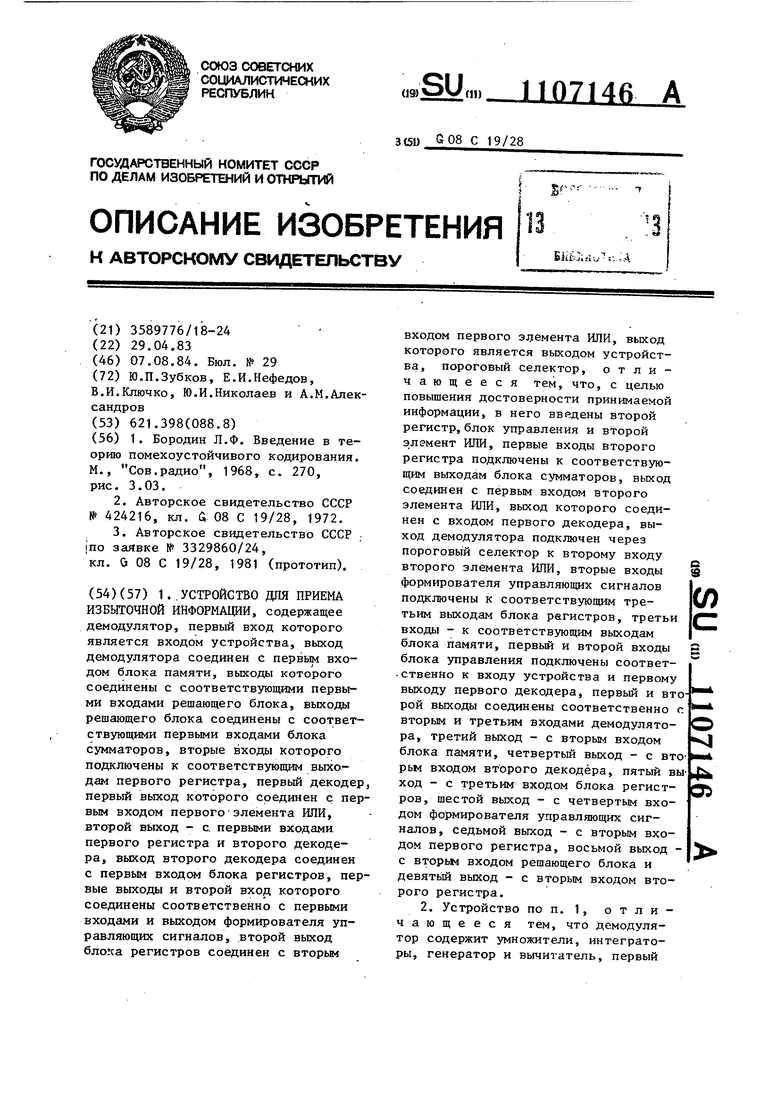

Указанная цель достигается тем, что в устройство для приема избыточной информации, содержащее демодулятор, первый вход которого является входом устройства, выход демодулятора соединен с первым входом блока памяти, выходы которого соединены с соответствующими первыми- входами решающего блока, выходы решающего блока соединены с соответствующими первыми входами блока сумматоров, вторые входы которого 11пл,клк1гены к соответствующим выхоп.)м перрого регистра, перный декод первый которого соединен с первым входом первого элемента ИЛИ второй выход - с первыми вкодами первого регистра и второго декодер выход второго декодера соединен с первым входом блока регистров, пер вые выходы и второй вход которого соединены соответственно с первыми входами и вьгходом формирователя управляюищх сигнапов, второй выход блока регистров соединен с вторым входом первого элемента ИЛИ, выход которого является выходом устройства, пороговый селектор, введены второй регистр, блок управления и второй элемент ИЛИ, первые входы второго регистра подключены к соOTBeTCTBvroinHM выходам блока сумматоров, выход соединен с первым в дом второго элемента ИЛИ, выход ко торого соединен с входом первого декодера, выход демодулятора подключен через пороговый селектор к второму входу второго элемента ИЛЬ вторые входы формирователя управляющих сигнштов подключены к соответствующим третьим выходам блока регистров, третьи входы - к соответствующим выходам блока памяти, первый и второй входы блока управления подключены соответственно к входу устройства и первому выходу первого декодера, первый и второй выходы соед 1нены соответственно с вторым и треты-iM входами демодулятора, третий выход - с вторым входом блока памяти, четвертый выход - с вторым входом второго деко дера, пятый выход - с третьим входом блока регистров, шестой выход с четвертым входом формирователя управляющих сигналов, седьмой выход - с вторым входом первого регистра, восьмой выход - с вторым входом решающего блока и девятый в ход - с вторым входом второго регистра. Демодулятор содержит умножители интеграторы, тенератор и вычитател первый и второй выходы генератора соединены с первыми входами соотве ственно первого и второго умножите лей, выходы которых соединены с первыми входами соответственно пер вого и второго интеграторов, выход которых соединены соответственно с первым и вторым входами вычитателя 464 вторые входы первого и второго умножителей объединены и являются первым входом демодулятора, вход генератора является вторым входом демодулятора, вторые входы первого и второго интеграторов объединены и являются третьим входом демодулятора, выход вычитателя является выходом демодулятора. Блок управления содержит генераторы импульсов, элементы задержки, элементы ИЛИ, формирователи импульсов, триггер и счетчик, выход первого генератора импульсов через последовательносоединенные первый и второй элементы задержки соединен с входами первого формирователя импульсов, третьего элемента задержки и первым входом первого элемента ИЛИ, выход третьего элемента задержки соединен с первым входом второго элемента ИЛИ и через четвертый элемент задержки - с входами второго формирователя импульсов и пятого элемента задержки, выход пятого элемента задержки соединен с вторым входом второго элемента ИЛИ, первым входом гретьего элемента ИЛИ и через шестой элемент задержки с вторым входом третьего элемента ИЛИ и входом седьмого элемента задержки, .выход седьмого элемента задержки соединен с вторым входом первого элемента ИЛИ и с входом восьмого элемента задержки, выход восьмого элемента задержки соединен через девятый элемент задержки с третьим входом третьего элемента ИЛИ и с входом десятого элемента задержки, выход десятого элемента задержки соединен с первым входом четвертого элемента ИЛИ, выход третьего элемента ИЛИ соединен с первым .входом триггера, выход которого через второй генератор импульсов соединен с входом счетчика,, выход счетчика соединен с вторым входом триггера, вход первого генератора импульсов и второй вход четвертого элемента ИЛИ являются соответственно первым и вторым входами блока управления, выходы первого генератора импульсов, первого элемента задержки, первого элемента ИЛИ, второго элемента ИЛИ, второго генератора импульсов, восьмого элемента задержки, первого формирователя импульсов, второго элемента задержки, второго формирователя импугьсов и четверто5го элемента ИЛИ являются соответственно первым, вторьвч, третьим, четвертым, пятым, шестым, седьмым, вос мым, девятым и десятым входями блока управления. Решающий блок содержит генератор элемент ИЛИ, элементы сравнения и ключи, выход генератора соединен с первыми входами элементов сравнения выходы которых соединены сортветственно с первыми входами ключей и входами элемента ИЛИ, выход элемента ИЛИ соединен с первым входом генератора и вторыми входами ключей, вторые входы элементов сравнения являются первыми входами решающего блока, второй вход генератора является вторым входом решающего блока выходы ключей являются выходами решающего блока. Формирователь управляющих сигналов содержит умножители, сумматоры и вычитатель, выходы первых и вт рых умножителей соединены с первыми входами соответственно первого и второго сумматоров, выходы которых соединены соответственно с первым и вторьсм входами вычитателя, первые входы первых и вторых умножителей являются соответственно первыми и вторыми входами формирователя управляющих сигналов, вторые входы первьйс умножителей объединены соответственно с вторыми входами вторых умножителей и являются третьими входами формирователя управляющих сигналов, вторые входы первого и второго сумматоров объединены и являются четвертым входом формирователя управляющих сигналов, выход вычитателя является выходом формирователя управляющих сигналов. Блок регистров содержит регистры ключи и элемент ИЛИ, выход первого регистра соединен с первыми входами первого ключа и второго регистра, выход второго регистра соединен с первым входом второго ключа, выходы первого и второго ключей соединены с соответствующими первым и вторым входами элемента ИЛИ, первый вход первого ключа является первым входом блока регистров, вторые входы первого и второго ключей объединены и являются вторым входом блока регистров, вторые входы первого и вто рого регистров объединены и являются третьим входом блока регистров, вьосоды второго регистра, элемента 6 ИЛИ и первого регистра яйлтяютс г соответственно первыми, вторым и третьими выходами блока регистров. На фиг. 1 приведена структурная схема устройства для приема избыточной информации; на фиг. 2 - структурная схема аналогового демодулятора (приемника); на фиг. 3 - структурная схема блока управления; на фиг.4структурная схема решающего блока; на фиг. 5 - структурная схема формирователя управляющих сигналов; на фиг. 6 - структурная схема блока регистров. Устройство для приема избыточной информации (фиг. 1) содержит аналоговый демодулятор 1, блок 2 памяти, пороговый селектор 3, декодер 4, исправляющий ошибки, блок 5 регистров, формирователь 6 управляющих сигналов, регистр 7, решающий блок 8, блок 9 сумматоров по модулю два, регистр 10, декодер 11, обнаруживающий ощибки, элементы ИЛИ 12 и 13 и блок 14 управления. Аналоговый демодулятор 1 (фиг.2) содержит генератор 15 опорных сигналов, умножители 16 и 17 интеграторы 18 и 19 и вычитатель 20. Блок 14 управления (фиг.З) содержит генератор 21, элементы 22-31 задержки, элементы ИЛИ 32-35, формирователи 36-38 импульсов, в каждый из которых входят счетчик 39, триггер 40 и генератор 41 тактоыых импульсов. Решающий блок 8 (фиг.4) содержит элементы 42 сравнения, ключи 43, генератор 44 линейно изменяющегося напряжения и элемент ИЛИ 45. Формирователь 6 управляющих сигналов (фиг. 5) содержит умножители 46 и 47, сумматоры 48 и 49 и вычитатель 50. Блок 5 регистров (фиг. 6) содержит регистры 51 и 52 сдвига, ключи 53 и 54 и элемент ИЛИ 55. Декодер 1 (фиг. 2) работает следующим образом. На его информационный вход поступает эл смен тарный канальный сигнал, входящий в составной (последовательный) избыточный сигнал. Этот же входной сигнал подается и на вход блока 14, в котором вырабатывается управляющий сигнал, по которому запускается генератор 15 опорных канальных сигяалоь. При этом на входах каждого из умгюжи7телей 16 и 17 синхронно появляются входной и соответствующий опорный сигналы. В умножителях 16 и 17 сигналы перемножаются. Выходной резуль тирующий сигнал каждого из умножителей подается на вход соответствую щего интегратора 18, 19. Бремя интегрирования определяется управляющим сигналом, подаваемым на каждый интегратор 18, 19 из блока 14. Выходные напряжения интеграторов 18 и 19 вычитаются в вычитателе 20 и входной элементарный канальный сигнал преобразуется в выходной разностный (аналоговый) сигнал. Блок 5 регистров (фиг. 6) работает следующим образом. По управляющим сигналам в регист ры 51 и 52 записываются информационные сигналы из декодера 4. В част ности, по первому управляющему сигналу в регистр 52 записывается первая выходная разрешенная двоичная кодовая комбинация. По второму управляющему сигналу происходит однов ременно две операции: сдвиг первой комбинации из регистра 52 в регистр 51 и запись второй разрешенной двои ной кодовой комбинации из декодера 4 в регистр 52. Управляющие сигналы формируются в соответствующие моменты времени в блоке 14. в определенны момент времени из формирователя 6 управляющих сигналов на управляющие входы ключей 53 и 54 блока 5 подается управляющий сигнал Если этот управляющий сигналя является положительным, то открывается ключ 53, в противном случае - ключ 54. После того, как откроется один из ключей, подается третий управляю щий сигнал на регистры 51 и 52. По третьему управляющему сигналу комбинация из регистра 51 считывается полностью, а из регистра 52 она одновременно переписывается в регистр 51 и также последовательно подается на информационный вход ключа 54 (сч тьшаясьиз регистра 51, комбинация подается на информационный вход ключа 53). Следовательно, если открыт ключ 53, то на вход блока 5 через элемент ИЛ1-1 55 считывается комбинация регистра 51. Если открыт ключ 54, то на выход блока 5 через элемент ИЛИ 55 считывается комбинация регистра 52. После второго управляющего сигнала на регистры 51 и 52 в них записаны разрешенные комбинации. С параллель46ных выходов ячеек памяти этих регистров разрешенные комбинации подаются в формирователь 6. Формирователь 6 управляющих сигналов предназначен для определения той из двух разрешенньос кодовых комбинаций, хранящихся в регистрах 51 и 52 блока 5,.которая в большей степени соответствует входному избыточному сигналу. В формирователе 6 на один вход каждого из умножителей 46, 47 подается аналоговый сигнал, а на другой вход - двоичный сигнал. Если двоичный сигнал единичный, то на выходе умножителя появляется аналоговый сигнал (с его другого входа) без изменения. Если двоичный сигнал, подаваемый на соответствующий вход умножителя, является нулевым, то на выходе умножителя формируется аналоговый сигнал с противоположным входному знаком. Формирователь 6 управляющих сигналов работает следующим образом. В соответствующие моменты времени (они задаются управляющими сигийлами блока 14) на входы умножителей 46 и 47 из блока 2 подаются аналоговые сигналы, а на другие входы умножителей с выходов блока 5 регистров подаются двоичные сигналы. В умножителях 46 и 47 указанные сигналы перемножаются. Результирующие сигналы с выходов умножителей суммируются в сумматорах 48 и 49. По управляющему сигналу из блока 14 на выходе каждого из сумматоров 48, 49 формируется вькодной сигнал, поступаю,щий на соответствующий вход элемента вычитателя 50. На выходе вычитателя 50 формируется управляющий сигнал, который поступает на управляюцц е входы ключей 53 и 54 блока 5 регистров. Решающий блок 8 (фиг.4) работает следующим образом. На информационные входы элементов 42 сравнения с выхода блока 2 подаются аналого- вые сигналы, а на другие входы подается линейно изменяющееся напряжение с выхода генератора 44, который в определенный MOMeHf времени запускается управляющим сигналом блока 14. Как только величины входных сигналов элементов 42 сравнения будут равны, на выходе этого элемента появляется управляющий сигнал, который через элемент ИЛИ 45 останавливает генератор 44 и через.соответ9ствующий ключ 43 подается на выход блока 8, Таким образом, решающий блок 8 определяет минимальный разностный сигнал, номер разряда его соответствует номеру разряда в выходной двоичной комбинации, которая является комбинацией двоичного кода постоянного единичного веса. Программно-временной блок 14 выполняет функции хронизации и управления, он определяет начало каждого элементарного канального сигнала и синхронно запускает генератор 15 опорных сигналов (фиг.2), элементы 22-31 задержки, формирователи 36-38 тактовых импульсов. Программно-временной блок (фиг. работает следующим образом. Входной элементарный канальный сигнал подается на генератор 21, на выходе которого формируется сигнал запуска генератора 15 (фиг.2), а также сиг нал, который после задержки в элементе 22 задержки подаётся на инте раторы 18 и 19 (фиг, 2). Выходной сигнал элемента 22 подается также на элемент 23 задержки, на выходе которого сигнал появляется после об работки демодулятором 1 всех элементарных канальных сигналов. Этот сигнал непосредственно подается в решающий блок 8 на запуск генератора 44, через формирователь 37 тактовых импульсов в виде последовательности тактовых импульсов подается в регистр 7, через элемент ИЛИ 33 выходной сигнал элемента 23 также подается в блок 2. Кроме тог выходной сигнал элемента 23 поступает на вход элемента 24 задержки, с выхйда которого сигнал подается через элемент ИЛИ 35 на декодер 4, разрешая исправление ошибок в перв двоичной кодовой комбинации. После задержки в элементе 25 управляющий сигнал запускает формирователь 36, тактовые импульсы которого подаютс на регистр 10 для записи в него скорректированной двоичной кодовой комбинации. Далее управляющий сигнал задерживается в элементе 26 задержки, с выхода которого управляющий сигнал через элемент ИЛИ 34 запускает генератор 41 в формирова теле 38 тактовых импульсов. Выходные импульсы генератора41 подсчитываются двоичным счетчиком 39. По следний импульс вызьшает переполне ние счетчика 39, вследствии чего н 4610 выходе счетчика 39 появляется импульс переполнения, который позврап(ает триггер 40 в исходное (нулевое) состояние, тем самым останавливая генератор 4I. Выходной сигнал элемента 26 задержки через элемент ИЛИ 35 подяется в декодер 4, разрешая исправление ошибок во второй двоичной кодовой комбинации, и на вход элемента 27 задержки. С выхода последнего управляющий сигнал через элемент ИЛИ 34 и формирователь 38 тактовых импульсов в виде последовательности тактовых импульсов подается на регистры блока 5. С выхода элемента 27 сигнал подается также на вход элемента 28 задержки. С его выхода управляющий сигнал через элемент ИЛИ 33 подается в блок 2. С выхода элемента 23 задержки управляющий сигнал подается на сумматоры 48 и 49 блока 8 и на вход элемента 30 задержки. Выходной сигнал элемента 30 через элемент ИЛИ 34 запускает формирователь 38 тактовых импульсов, выходные сигналы которого подаются в блок 5 для считывания соответствующей разрешенной кодовой комбинации на выход устройства. Задерживаясь в элементе 31 задержки, выходной сигнал элемента 30 -через элемент ИЛИ 32 становится сигналом общего сброса, который подается на все элементы памяти и другие элементы устройства, приводя их в исходное состояние. Устройство для приема избыточной информации работает следующим образом. Составной сигнал с избыточностью из канала связи поступает в аналоговый демодулятор 1, в котором преобразуется в составной аналоговый сигнал, состоящий из Н элементарных аналоговых сигналов. Этот аналоговый сигнал (аналоговая комбинация) X запоминается в блоке 2 памяти и, преобразуясь с помощью порогового селектора 3 в двоичную кодовую комбинацию У, через элемент ИЛИ 12 подается в декодор 11. Если в декодере 11 не будет обнаруткено, что в комбинации У есть ошибки (т.е. она является разрешенной двоичной кодовой комбинацией), комбинация У через элемент ИЛИ 13 выдается на выход устройства, а первый ее двоичный сиг- , 11 нал, подаваясь в блок 14, преобразуется в сигнал общего сброса (о.с. при котором все блоки устройства приводятся в исходное состояние и устройство готово к обработке следующего входного сигнала. При обнаружении ошибок в У кодовая комбинация подается на вход регистра 7, где запоминается, и на вход декодер 4,-который отождествляет комбинацию У с ближайшей разрешенно двоичной кодовой комбинацией У, Ко бинация У записывается и хранится в блоке 5 регистров. Из блока 2 памяти аналоговые сиг налы также параллельно считываются в решаюищй f5лoк 8, в котором опреде ляется наименьший из аналоговых сигналов. На выходе решающего блока 8 формируется двоичная кодовая комб нация, в которой единичный символ находится в разряде с тем же номеро что и наименьший аналоговый символ (сигнал). Другие разряды нулевые. После этого из регистра 7 в блок 9 сумматоров поступает двоичная кодов комбинация У, а из блока 8 - комбинация с единичным весом. В блоке 9 сумматоров по модулю два суммируютс (в параллельном коде) двоичная кодо вая комбинация единичного веса и ко бинация У, являющаяся первой грубой оценкой составного сигнала с избыточностью. В результате суммировани на выходе блока 9 образуется двоичная кодовая комбинация У . Двоичная кодовая комбинация У/| запоминается в регистре 10. Двоичная кодовая комбинация регистра 10 отличается от двоичной кодовой комб нации регистра 7 в одном разряде, н мер которого определяется номером ед ничного разряда в выходной двоичной комбинации решающего блока 8. Считываясь из регистра 10, комбинация У через элемент ИЛИ 12 подает ся Б декодер 11, где обрабатывается так же, как и комбинация У. Т.е. если она не является разрешенной (в У имеются ошибки) , комбинация У/i подается на вход декодера 4. В декодере 4 комбинация У/i отождествляется с ближайшей разрешенной кодовой комбинацией У/, которая также записывается и хранится в блоке 5 регистров. Из блока 2 памяти по управляющему сигналу из блока 14 в формирователь 6 поступает составной аналоговый сигнал X (точная копия входного избыточного сигнала), а из блока 5 в параллельном коде подаются двоичные разрешенные кодовые комбинации У и У. В формирователе 6 определяется, какая из двух разрешенных кодовых комбинаций больше соответствует сигналу точной оценки X. Степень соответствия может определяться, например, в результате вычисления коэффициентов корреляции (им соответствуют выходные сигналы сумматоров 48 и 49 формирователя 6) с пocJ7eдyющим их сравнением. Ближайшая разрешенная кодовая комбинация по управляющему сигналу соответствующей полярности из формирователя 6 в блок 5 считывается из блока 5 на выход устройства через элемент ИЛИ 13. После этого блок 14 формирует сигнал общий сброс и устройство обрабатывает следующий составной сигнал с избыточностью. Предлагаемое устройство для приема избыточной информации по методу ближней зоны обладает более высокими технико-экономическими показателями по сравнению с известным устройством. В качестве показателя достоверности обработки информации будем считать величину Б, пропорциональную вероятности правильного приема Р(«((р) составного сигнала с избыточностью и вероятности безотказной работы Р, т.е. Б. РП(. При заданном качестве канала связи можно считать, что Б Рср-. Вероятность безотказной работы оценивается отношением числа однотипных элементов устройства, продолжающих работать по истечении времени Т, к общему числу элементов (аналогичных) аппаратуры, исправных в момент времени Т О v 1 где л-общее число элементов в М(Т)-число элементов, отказавших за время Т (будем считать, что интенсивность отказов сумматоров по модулю два и в предлагаемом и в известном устройствах одна и та же).

1 (

Ориентировочно выигрьпи по достоверности оРработкн информации оцени1.

М-(ТЧ Так как ;-,-, L ,

Фиг.2.

f

(fJ.

Фиг.У

fift. в

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Сов.радио, 1968, с | |||

| Приспособление для уменьшения дымовой тяги паровоза | 1920 |

|

SU270A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-29—Подача