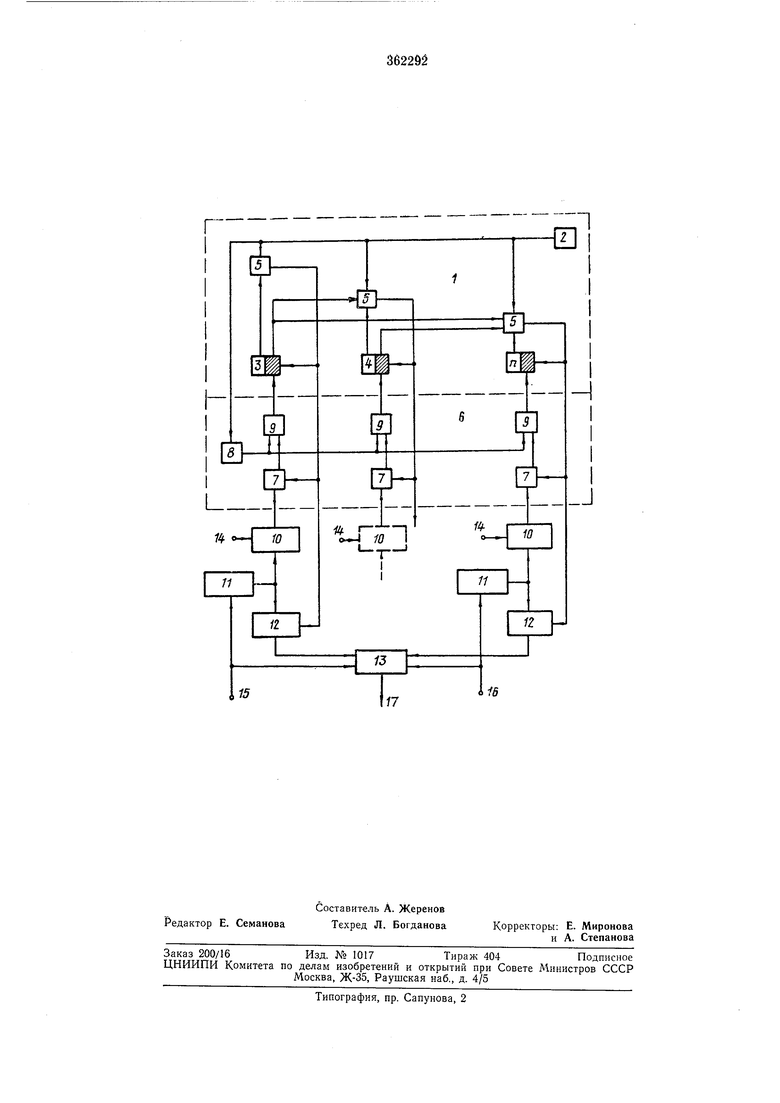

Изобретение относится к области вычислительной техники и может быть использовано для предварительной обработки дискретной информации и связи с цифровой вычислительной машиной. Известны устройства для селекции кодов. Известные устройства не обладают способностью выделять оперативную выборочную информацию из всего информационного потока, поступающего на их входы, поэтому с помощью таких устройств невозможно уплотнить поток оперативной информации, тем самым увеличить количество одновременно обслуживаемых линий связи. Цель изобретения состоит в том, чтобы уплотнить выборочные взаимно несинхронизированные потоки информации. Сущность изобретения заключается в том, что устройство для селекции кодов содержит блоки программ, первые входы которых подключены к выходам одноименных узлов ввода кодов, а вторые входы соединены с щиной ввода программ, выход каждого блока программ через блок фазирования соединен соответствующим входом блока анализа приоритета, каждый выход которого соединен со входом одноименного узла считывания кодов. На чертеже представлена схема устройства для селекции кодов. с Она содержит блок анализа приоритета Л в состав которого входит генератор импульсов 2, триггеры 3, 4, ..., п и схемы совпадения 5; блок фазирования 6, включающий ячейки памяти 7, формирователь импульсов 8 и схемы совпадения 9; блоки программ 10, узлы // ввода кодов, узлы 12 считывания кодов, выходной блок 13, шину 14 ввода программ, входы 15 и 16 и выход 17 устройства. Блок программ 10 состоит из связанных между собой запоминающего устройства и устройства сравнения кодов. Запоминающее устройство подключено к одному из входов устройства сравнения кодов. К другому входу этого устройства сравнения кодов подключен выход узла 11. Выход схемы сравнения (он же выход блока программ) связан с ячейкой памяти 7. В запоминающем устройстве блока программ хранятся коды чисел, необходимые для выборки, и программа выборки этих кодов. Узел // представляет собой запоминающее устройство, где могуг быть записаны числовые коды и признаки данной линии. Выходы узлов 12 подключены к выходу 17 через выходной блок 13. В этом блоке одноименные разряды числовых кодов от всех узлов 12 объединены и выведены на общую шину. Устройство для селекции кодов работает следующим образом.

В исходном состоянии сигнал на входах 15 и 16 отсутствует. В блоки программ 10 по шине 14 введена некоторая программа выборки кодов. Триггеры 3, 4, ..., п запреш,ают сигналы на выходах схем совпадения 5. Ячейки памяти 7 очищены и на их входы сигналы не поступают. Тактовые импульсы от генератора импульсов 2 динамического воздействия на элементы схемы не оказывают. На выходе 17 сигналы отсутствуют.

При работе устройства на входы 15 и 16 поступают коды чисел из несинхронизированных между собой линий связи. Эти коды фиксируются в узлах 11. Затем для каждой линии связи в отдельности происходит сравнение кодов чисел, находящихся в узлах 11, и кодов чисел, заданных в блоке программ 10. При совпадении кодов, устройство сравнения блока iHipoirpaiMM вырабатывает сигнал paiBOHCTBa кодов. Этот сигнал поступает на вход ячейки памяти 7 и там запоминается.

Очередной тактовый импульс от генератора импульсов 2 своим передним фронтом, который выделен формирователем импульсов 8, переводит информацию, записанную во всех ячейках памяти 7, через схемы совпадения 9 в триггеры 3, 4, ..., п,-1. Перевод информации из ячеек памяти в триггерыпараллельным кодом означает привязку по времени сигналов равенства кодов ,фазе тактрвьгхим.п льсов генератора. Опросньши импульсами для всех ячеек памяти 7 является каждый тактовый импульс генератора. Параллельное фазирование сигналов равенства кодов устраняет зависимость периода поступления кодов на входы устройства от периода тактовых импульсов.

Код, записанный в триггерах 3, 4, ..., п, анализируется схемами совпадения 5 на предмет присвоения приоритета по важности обслуживаемой линии и по времени поступления кодов на входы устройства. Пусть, например, сигналы равенства кодов поступают одновременно на триггер 3 и триггер п. В этом случае триггеры 3 и я переключатся в состояние, отличное от исходного. Схема совпадения 5, подключенная к левому плечу триггера 3, подготавливается, а схемы совпадения, подключенные к правому плечу триггера 3, закрыты, поэтому тактовый импульс, переключающий триггеры 3 и п, проходит только через одну схему совпадения 5, в частности схему, подключенную к левому плечу триггера 5, с выхода которой импульс поступает на вход узла 12 и тем самым пропускает информацию из узла ill в выходной блок 13. Задний фронт этого же тактового импульса устанавливает триггер 5 в исходное состояние и очищает ячейку памяти 7. Схема совпадения, подключенная в левое плечо триггера 3, переходит в исходное состояние, а схема совпадения, подключенная в левое плечо триггера п,

подготавливается к работе.

Очередной второй тактовый импульс проходит через схему совпадения 5, подключенную к левому плечу триггера я. Остальные схемы находятся в исходном состоянии и не пропуекают тактовые импульсы. На выходе 17 появляются сигналы кода выбранного числа, относящегося к п-му входу 16. Элементы схемы, относящиеся к п-му входу, задним фронтом второго тактового импульса приводятся в

исходное состояние. Если в момент поступления ;второг,о TaiKTOtBoro ,ИМ1пулыса 1в:ключается триггер 4, то подготавливается к работе схема совпадения, подключенная к левому плечу этого триггера, а все другие схемы совпадения

5 выключены.

Третий тактовый импульс обслуживает коды, поступающие по входу 16, однако этот вход не обслуживается, если с приходом третьего тактового импульса включается хотя

бы один из триггеров с меньщим номером.

Таким образом, коды, поступающие через входы с меньщим порядковым номером, передаются на выход 17 в первую очередь и, следовательно, имеют приоритет перед кодами,

поступивщими через входы с больщим порядковым номером.

Предмет изобретения

Устройство для селекции кодов, содержащее узлы ввода кодов, узлы считывания кодов, блок фазирования, блок анализа приоритета и выходной блок, отличающееся тем, что, с целью уплотнения выборочных взаимно несинхронизированных потоков информации, оно содержит блоки программ, первые входы которых яодключены к IBыходам одноим иных узлов ввода кодов, а вторые входы соединены с щиной ввода программ, выход каждого блока программ через блок фазирования соединен с соответствующим входом блока анализа приоритета, каждый выход которого соединен со входом одноименного узла считывания кодов.

А/5

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1981 |

|

SU1840934A1 |

| УСТРОЙСТВО для СЕЛЕКЦИИ КАНАЛОВ СВЯЗИ | 1972 |

|

SU329677A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Адаптивное устройство для приема информации с рассредоточенных объектов | 1990 |

|

SU1751798A1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Адаптивное устройство для приема информации с рассредоточенных объектов | 1991 |

|

SU1807509A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

Авторы

Даты

1973-01-01—Публикация