1

Изобретение относится к технике передачи данных.

Известны устройства по основному авт. св. № 206169, содержащие регистры с обратной связью, рекуррентные датчики, кодирующие устройства, сумматоры по модулю два и логические схемы.

В известном устройстве для исправления многократных ошибок ограничена скорость передачи информации.

Предлагаемое устройство отличается тем, что с целью увеличения быстродействия оно содержит дополнительные регистры по числу разрядов рекуррентного датчика, транзисторные ячейки типа «Запрет, триггеры, сумматоры по модулю два, кодирующие блоки корректирующего кода, регистры сдвига и схемы совпадения. Выходы разрядов рекуррентного датчика соединены через соответствующие кодирующие блоки со входами соответствующих сумматоров по модулю два, другие входы которых подключены к выходу входного регистра.

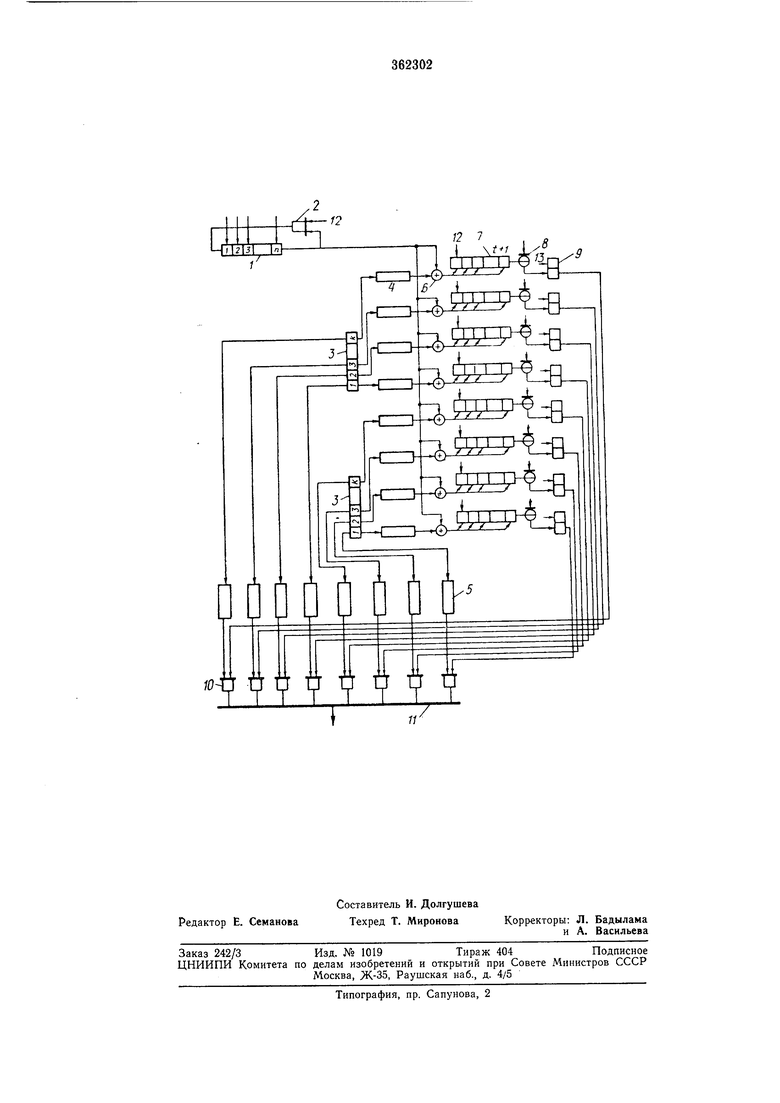

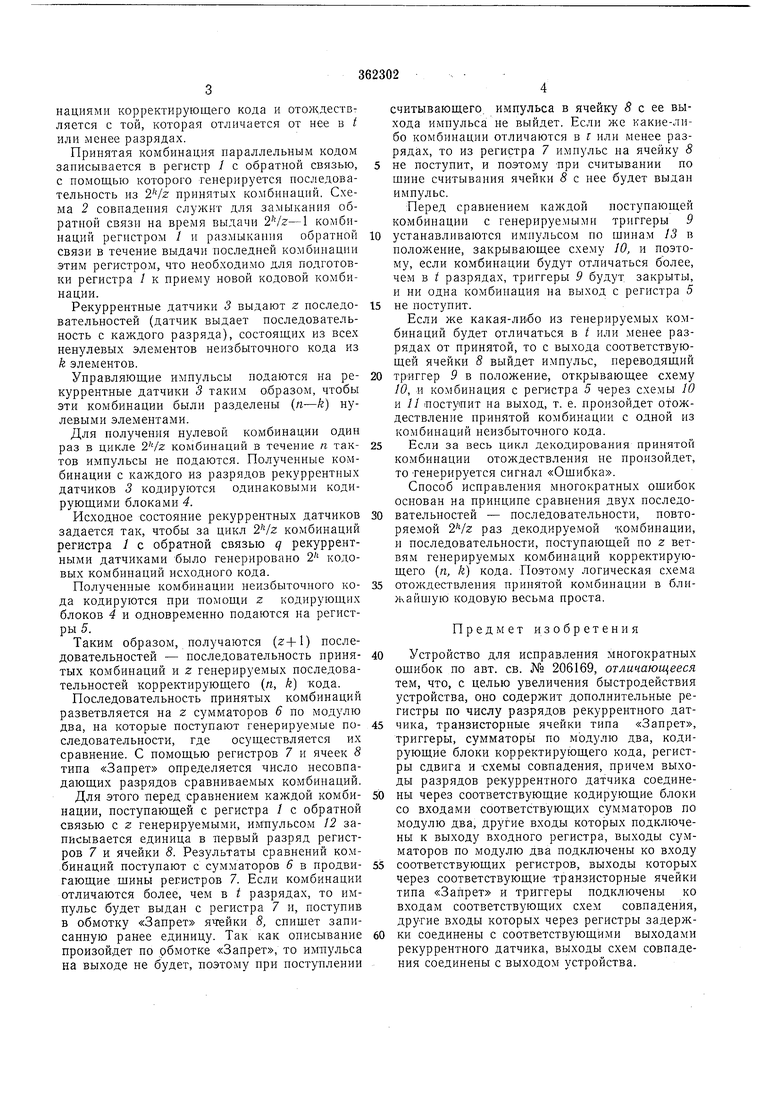

Выходы сумматоров по модулю два подключены ко входу соответствующих регистров, выходы которых через соответствующие транзисторные ячейки типа «Запрет и триггеры подключены ко входам соответствующих схем совпадения, другие входы которых через регистры задержки соединены с соответствующими выходами рекуррентного датчик,... Выходы схем совпадения соединены с выходом устройства. На чертеже представлена блок-схема описываемого устройства.

Она содержит регистр / на /г разрядов с обратной связью, схему 2 совпадения, q рекуррентных датчиков 3 исходного безызбыточного кода на k разрядов, z кодирующих блоков 4 корректирующего кода, z регистров 5 сдвига на k разрядов, г схем сравнения (сумматор 6 по модулю два), z регистров 7 на (t+l) разрядов, z ферротранзисторных ячеек 8 типа «Запрет, z триггеров 9, z схем W совпадения и сборку 11.

Пусть передача информации осуществляется корректирующим (п, k) кодом, в котором п - общее число двоичных элементов, а k - число информационных элементов.

Если в принятой комбинации искажено t

или менее элементов, то при t , где

d - расстояние Хемминга, она будет отличаться от (2-I) генерируемых больше, чем в t разрядах, а от одной в t или менее разрядах.

Следовательно, для исправления ошибок

кратности t и менее принятая кoм бинaция

сравнивается со всеми генерируемыми комбинациями корректирующего кода и отокдествляется с той, которая отличается от нее в / или менее разрядах.

Принятая комбинация параллельным кодом записывается в регистр / с обратной связью, с помощью которого геиерируется последовательность из 2Vz принятых комбинаций. Схема 2 совпадения служит для замыкания обратной связи на время выдачи 2Vz-1 комбинаций регистром / и размыкания обратной связи в течение выдачи последней комбииации этим регистром, что необходимо для подготовки регистра 1 к приему новой кодовой комбинации.

Рекуррентные датчики 3 выдают z последовательностей (датчик выдает последовательность с каждого разряда), состоящих из всех ненулевых элементов неизбыточного кода из k элементов.

Управляющие импульсы подаются на рекуррентные датчики 5 таким образом, чтобы эти комбинации были разделены (п-k) нулевыми элементами.

Для получения нулевой комбинации один раз в цикле комбинаций в течение п тактов импульсы не подаются. Полученные комбинации с каждого из разрядов рекуррентных датчиков 3 кодируются одинаковыми кодирующими блоками 4.

Исходное состояние рекуррентных датчиков задается так, чтобы за цикл 2/2 комбинаций регистра / с обратной связью q рекуррентными датчиками было генерировано 2 кодовых комбинаций исходного кода.

Полученные комбинации иеизбыточного кода кодируются при ПОМОЩИ Z кодирующих блоков 4 и одновременно подаются на регистры 5.

Таким образом, получаются (z+) последовательностей - последовательность принятых комбинаций и 2 генерируемых последовательностей корректирующего (п, k) кода.

Последовательность принятых комбинаций разветвляется на z сумматоров 6 по модулю два, на которые поступают генерируемые последовательности, где осуществляется их сравнение. С помощью регистров 7 и ячеек 8 типа «Запрет определяется число несовпадающих разрядов сравниваемых комбинаций.

Для этого перед сравнением каждой комбинации, поступающей с регистра / с обратной связью с z генерируемыми, импульсом 12 записывается единица в первый разряд регистров 7 и ячейки 8. Результаты сравнений ком.бинаций поступают с сумматоров 6 в продвигающие щины регистров 7. Если комбинации отличаются более, чем в t разрядах, то импульс будет выдан с регистра 7 и, поступив в о.бмотку «Запрет ячгейки 8, спищет записанную ранее единицу. Так как описывание произойдет по обмотке «Запрет, то импульса на выходе не будет, поэтому при поступлении

считывающего, импульса в ячейку § с ее выхода импульса не выйдет. Если же какие-либо комбинации отличаются в г или менее разрядах, то из регистра 7 импульс на ячейку 8 не поступит, и поэтому при считывании по щине считывания ячейки 8 с нее будет выдан импульс.

Перед сравнением каждой поступающей комбинации с генерируемыми триггеры 9

устанавливаются импульсом по щинам 13 в положение, закрывающее схему 10, и поэтому, если комбинации будут отличаться более, чем в / разрядах, триггеры 9 будут закрыты, и ни одна комбинация на выход с регистра 5

не поступит.

Если же какая-ли бо из генерируемых комбинаций будет отличаться в t или менее разрядах от принятой, то с выхода соответствующей ячейки 8 выйдет имнульс, переводящий

триггер 9 в иоложение, открывающее схему 10, и комбинация с регистра 5 через схемы 10 и // поступит на выход, т. е. произойдет отождествление принятой комбинации с одной из комбинаций неизбыточного кода.

Если за весь цикл декодирования принятой комбинации отождествления не произойдет, то Генерируется сигнал «Ощибка.

Способ исправления многократных ошибок основан на принципе сравнения двух последовательностей - последовательности, повторяемой раз декодируемой комбинации, и последовательности, поступающей по z ветвям генерируемых комбинаций корректирующего (п, k) кода. Поэтому логическая схема

отождествления принятой комбинации в ближайп1ую кодовую весьма проста.

Предмет изобретения

Устройство для исправления многократных ощибок по авт. св. № 206169, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит дополнительные регистры по числу разрядов рекуррентного датчика, транзисторные ячейки типа «Запрет, триггеры, сумматоры по модулю два, кодирующие блоки корректирующего кода, регистры сдвига и Схемы совпадения, причем выходы разрядов рекуррентного датчика соединены через соответствующие кодирующие блоки со входами соответствующих сумматоров по модулю два, другие входы которых подключены к выходу входного регистра, выходы сумматоров по модулю два подключены ко входу

соответствующих регистров, выходы которых через соответствующие транзисторные ячейки типа «Запрет и триггеры подключены ко входам соответствующих схем совпадения, другие входы которых через регистры задержки соединены с соответствующими выходами рекуррентного датчика, выходы схем совпадения соединены с выходом устройства.

12

/2 7 t

/IT

III I / f /

т I I I I 11-4 43 4) -41

- nil -j. Iiq;

-1 I I I I I b-B n 4 -2±2±: TlZt

1 ШГТьф ЧП / / / I-4l

DUD DO

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК | 1967 |

|

SU206169A1 |

| УСТРОЙСТВО ИСПРАВЛЕНИЯ СТИРАНИЙ | 1973 |

|

SU396826A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| Устройство исправления стираний | 1975 |

|

SU581589A2 |

| Устройство исправления стираний | 1977 |

|

SU651479A2 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

Авторы

Даты

1973-01-01—Публикация