Известны устройства для исправления ошибок в кодовой комбинации кратности /. В этих устройствах исправление производится в результате обнаружения и опознавания позиций искаженных символов. При этом для исправления /-кратных ошибок необходимо применить корректирующий код с кодовым расстоянием d 2t + 1.

Предлагаемое устройство обеспечивает исправление кpaтныx ошибок при использовании корректирующего кода с кодовым расстоянием . Это обеспечивается тем, что выход регистра сдвига, соответствующий интегральному методу регистрации принимаемых сигналов, соединен с входом первого устройства обнаружения ошибок, выход которого соединен с одним входом второй ячейки памяти, соединенной своим выходом с входом третьей ячейки памяти, другой вход которой подключен к выходу ячейки запрета, а выход через триггер соединен с одним входом второй схемы совпадения и с входом первого регистра памяти, выход которого подключен к входу сумматора по модулю два, другой вход которого соединен с выходом второй схемы совпадения, а выход соединен с входом второго регистра памяти и с входом второго устройства обнаружения ошибок, выход которого соединен с одним входом четвертой ячейки памяти. Выход первой ячейки памяти соединен с другим входом второй ячейки памяти, с входом счетчика ошибок, один выход которого соединен с другим входом четвертой ячейки памяти, другие выходы через коммутатор подключены к входу ячейки запрета, с другим входом ячейки заирета и с входом регистратора ошибок, выход которого подсоединен к другому входу второй схемы совпадения.

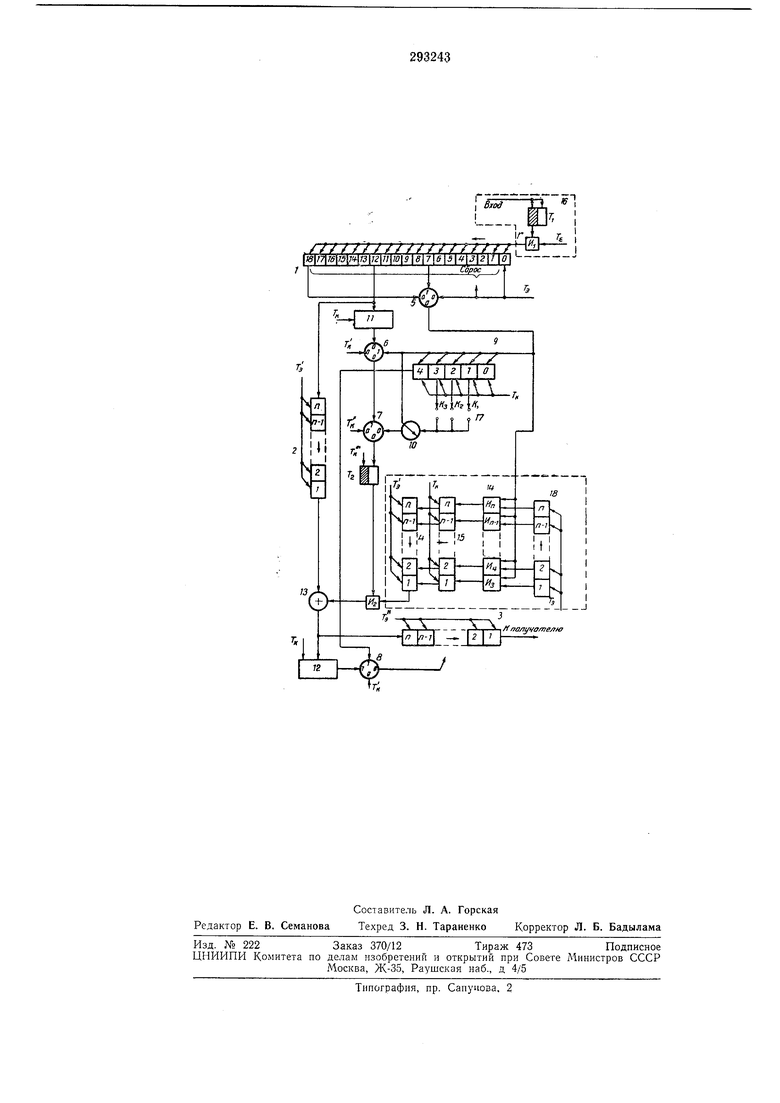

На чертеже приведена схема описываемого устройства.

Оно содержит прпемный регистр 1 сдвига, регистры 2 - 4 памяти, ячейки 5 - 5 памяти, счетчик ошибок 9, ячейку 10 запрета, устройства 11 и 12 обнарулсения ошибок, схемы совпадения «HI - Ип, триггеры TI и TZ, сумматор 13 по модулю два, регистратор 14 ошибок, буферный накопитель 15 и входное устройство 16.

В предлагаемом устройстве регистрация принимаемых импульсов осуществляется интегральным методом с помощью одного восемнадцатиразрядного регистра 1 сдвига, к двенадцатой ячейке которого подключено устройство 11 обнаружения ошибок в кодовой комбинации и регистр 2 памяти, что составляет блок регистрации импульсов интегральным методом. Этот же регистр используется для анализа кодовых элементов. Анализатор кодосдвига с выводами из ячеек 7 и 18 и ячейку 5 памяти.

Приводимое на чертеже устройство изображено для случая, когда принимаемые элементарные импульсы сканируются в е точках (е 25), .при зоне неопределенности Ь И, что составляет 44%.

На схеме показаны таклсе тактовые импульсы, обеспечивающие работу устройства:

Т -для сканирования принимаемых элементарных сигналов и формирования импульсов сдвига;

/, еЛ 25Л - для показанного случая, где В--число точек сканирования, Л - скорость телеграфирования. Гэ-для считывания элементарных сигналов с частотой следования . равной скорости телеграфирования; Гк - для считывания результатов проверки кодовых комбинаций с частотой следования /к, равной скорости передачи комбинации /к NIn, где п - разрядность кодовой комбинации.

Тактовые импульсы Г, Т, Т , Т , сдвинуты по фазе от основных на время, необходимое для нормальной работы схемы.

Регистрация принимаемых импульсов интегральным методом осуществляется следующим образом.

При .поступлении на вход устройства положительного импульса триггер TI открывает схему совпадения «И, на другой вход которой поступают тактовые импульсы, и единица, записанная в «О ячейке приемного регистра /, продвигается влево. Если с выхода схемы совпадения «Hi поступит 13 и более импульсов, то единица будет продвинута в 13-ую ячейку и далее. При этом на выходе 12-й ячейки регистра появится импульс, поступающий на вход устройства 11 обнаружения ошибок и регистра 2 памяти.

По окончании приема элементарного сигнала тактовым импульсом Гэ производится сброс всех ячеек регистра в «О, а в нулевую ячейку записывается единица. После этого начинается прием следующего элементарного импульса.

Если при приеме «1 число продвигающих импульсов (с выхода схемы совпадения «Н) будет не больше 12, то в регистр 2 и в устройство 11 обнаружения ошибок запишется «О, что соответствует приему кодового элемента с ошибкой. При приеме «О число продвигающих импульсов должно быть меньше 13, в противном случае будет неправильная регистрация.

При использовании циклического (п, к) кода устройство // обнаружения ошибок производит деление последовательности из символов на порождающий полином. Получение остатка при делении будет свидетельствовать о наличии ошибки в кодовой комбинации, тогда сигнал с выхода устройства // считывает записанную в ячейке 6 единицу, в противном случае она стирается тактовым импульсом Т. Запись «1 в ячейку 6 производится путем анализа кодовой комбинации. С выхода 7-й ячейки .приемного регистра 1 в ячейку 5 памяти записывается «1 только в том случае, если

в регистр / будет подано не менее 8 продвигающих импульсов. В случае, если в регистр I поступит не менее 19 импульсов, она будет стерта. Если число продвигающих импульсов 8 Г 18, то она будет считана тактовым

импульсом Го и подана на вход счетчика ошибок 9 и регистратора 14 ошибок.

Счетчик ошибок 9 вырабатывает следуюшие решения: если число обнаруженных с помощью АКЭ ошибок не превышает а (для данного устройства применен циклический код с гарантийным обнаружением а-3-кратных ошибок), а устройство 11 не обнаружило ошибок, то принятая комбинация передается получателю без исправления; если число ошибок, обнаруженных АКЭ, не превышает трех, а с выхода устройства // поступил сигнал «ошибка, то в принятой комбинации может быть исправлено от одной до трех ошибок в разрядах, в которых АКЭ обнаружены ошибки (количество исправляемых ошибок зависит от коммутации схемы).

Счетчик ошибок работает следующим образом.

В исходном положении в нулевой ячейке

счетчика записана «1. При поступлении с выхода ячейки 5 сигнала «ошибка, единица из нулевого разряда счетчика продвигается в соседнюю ячейку. Одновременно в ячейку записывается единица.

В зависимости от результата анализа кодовой комбинации устройством 11 обнаружения ошибок «единица из ячейки 6 может быть стерта либо продвинута в ячейку 7 (при обнаружении ошибки).

С помощью указанного на схеме коммутатора 17 может быть изменена логика работы схемы исправления ошибок. Так, например, если будут замкнуты только клеммы К, то исправляться будет одна ошибка, при замыкаНИИ клемм /Ci и /(2--две ошибки, наконец, при замыкании всех трех клемм /С - К - исправление трех ошибок в кодовой комбинации.

Продвижение «1 из ячейки 7 на выход триггера Га производится только в том случае,

если, например, при замыкании всех трех клемм коммутатора в счетчике будет находиться «1 в ячейках 1, 2 w. 3, т. е. когда устройством АКЭ будет обнаружено в кодовой комбинации от одной до трех ошибок. В этом

случае тактовый импульс Гк, считывая из счетчика информацию, через ячейку 10 запрета подает импульс, который считает «1 из ячейки 7 и подает на вход триггера Гг, который перейдет в состояние, открываюшее схему ступать импульсы от устройства исправления ошибок на вход сумматора 13 по модулю два. Исправление ошибок производится с помощью регистратора 14 ошибок, который состоит из распределителя, избирательной схемы, буферного накопителя 15 и регистра 4. Каждая ячейка избирательной схемы имеет два входа. На первые их входы одиовременно на все ячейки подается сигнал ошибки с выхода ячейки, а на их вторые входы - напряжение с ОД1НОЙ из ячеек распределителя. На выходе каждой ячейки последовательно будет появляться высокое напряжение только в том случае, если на ее входе будет подано высокое напряжение как с выхода соответствуюш:ей ячейки распределителя так и с выхода ячейки 5. В результате в буферном накопителе 15 будут записаны «1 только в тех ячейках, номера которых совпадают с номерами разрядов ошибочных символов, обнаруженных в кодовой комбинации с помош.ью АКЭ. В дальнейшем тактовым импульсом Тк записанные «1 из буферного накопителя 15 после приема кодовой комбинации одновременно считываются в регистр 4. Если при считывании информации из регистров 2 и 4 схема совпадения «HZ будет открыта, высокое напряжение с выхода регистра 4, появляющееся при считывании разрядов, в которых обнаружена ошибка, в схеме сумматора 13 будут исправляться поступающие с выхода регистра 2 символы на обратные («1 на «О и «О на «1). После этого исправленная комбинация записывается в регистр 3 и проверяется «а наличие ошибок. При отсутствии ошибок комбинация выдается получателю, в противном случае стирается и посылается запрос на повторную передачу. Предмет изобретения Устройство для исправления ошибок в кодовой комбинации, содержащее регистр сдвига, ячейки памяти, ячейки запрета, сумматор, регистратор ошибок, схемы совпадения, устройства обнаружения ошибок, счетчик ошибок, отличающееся тем, что, с целью повышения эффективности обнаружения и исправления ошибок в кодовой комбинации, выход регистра сдвига, соответствующий интегральному методу регистрации принимаемых сигналов, соединен с входом первого устройства обнаружения ошибок, выход которого соединен с одним входом второй ячейки памяти, соединенной своим выходом с входом третьей ячейки памяти, другой вход которой подключей к выходу ячейки запрета, а выход через триггер соединен с одним входом второй схемы совпадения и с входом первого регистра памяти, выход которого подключен к входу сумматора по модулю два, другой вход которого соединен с выходом второй схемы совпадения, а выход соединен с входом второго регистра памяти и с входом второго устройства обнаружения ошибок, выход которого соединен с одним входом четвертой ячейки памяти, выход первой ячейки памяти соединен с другим входом второй ячейки памяти, с входом счетчика ошибок, один вход которого соединен с другим входом четвертой ячейки памяти, другие выходы через коммутатор подключены к входу ячейки запрета, с другим входом ячейки запрета и с входом регистратора ошибок, выход которого подсоединен к другому входу второй схемы совпадения.

///////////////// /1 Ьт

| |/71д |«17 р1 г|;/|;о| |г|7 5 г| |г|/|0|

I игл JlA

J 1 .J.-J

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ЭКСПЕРИМЕНТАЛЬНОГО ИССЛЕДОВАНИЯ | 1971 |

|

SU297963A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для исправления ошибокВ КОдОВОй КОМбиНАции | 1978 |

|

SU805315A1 |

| Тренажер радиотелеграфиста | 1983 |

|

SU1119057A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ | 1969 |

|

SU251253A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для исправления модульных ошибок | 1988 |

|

SU1522414A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК | 1967 |

|

SU206169A1 |

| СПОСОБ ИСПРАВЛЕНИЯ МНОГОКРАТНЫХРАЗНЕСЕННЫХ И СОСРЕДОТОЧЕННЫХВ ПАКЕТЫ ОШИБОК | 1972 |

|

SU428435A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

ff /галучоте/гю

Даты

1971-01-01—Публикация