u.i.J

Фиг. I

1462492

Изобретение относится к электросвязи и может быть использовано в системах передачи информгщии с решающей обратной связью.

Цель изобретения - повышение достоверности устройства,

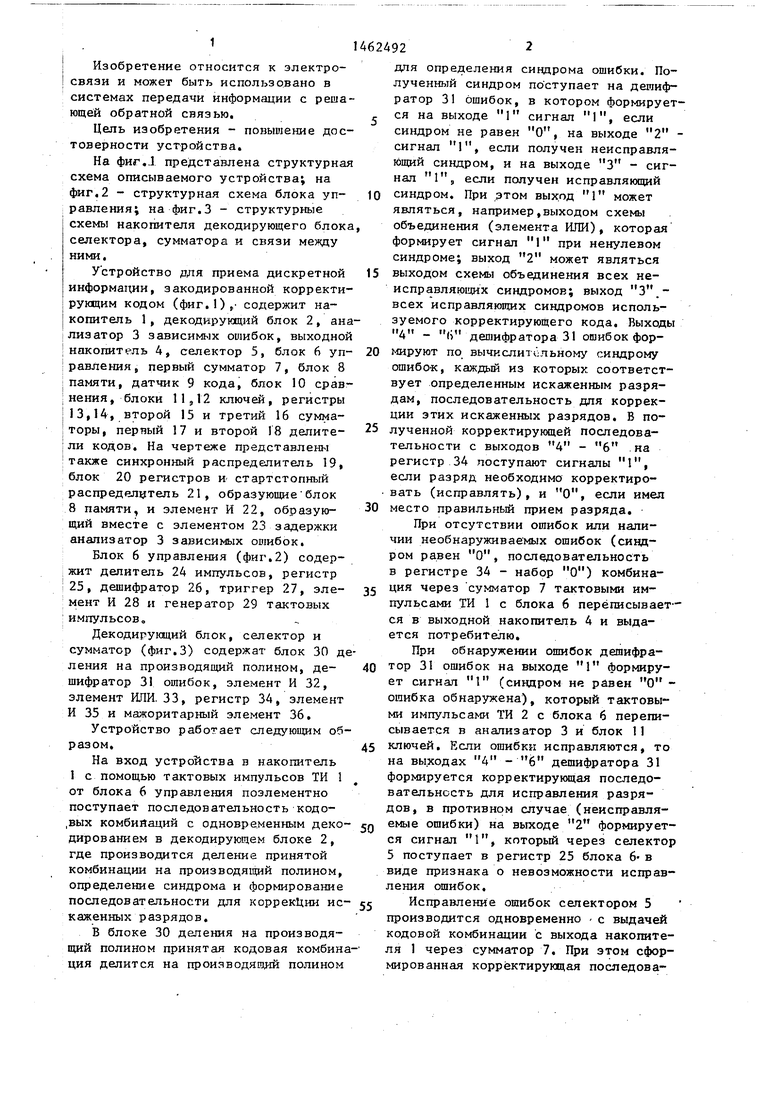

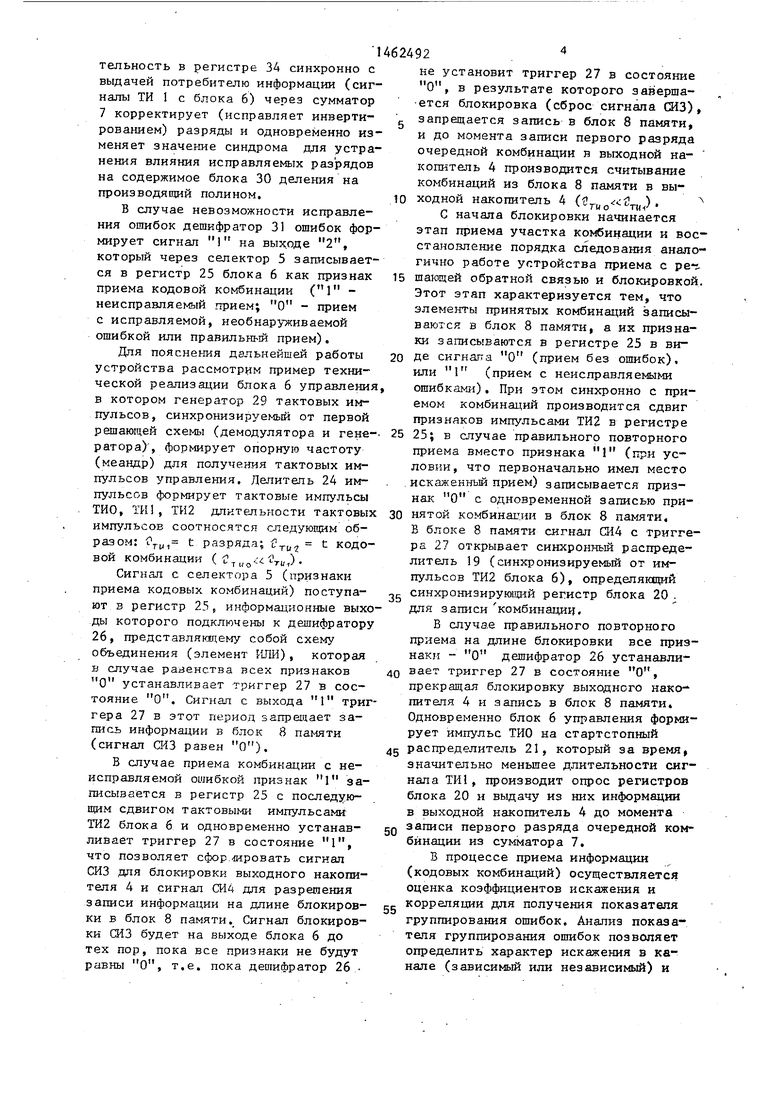

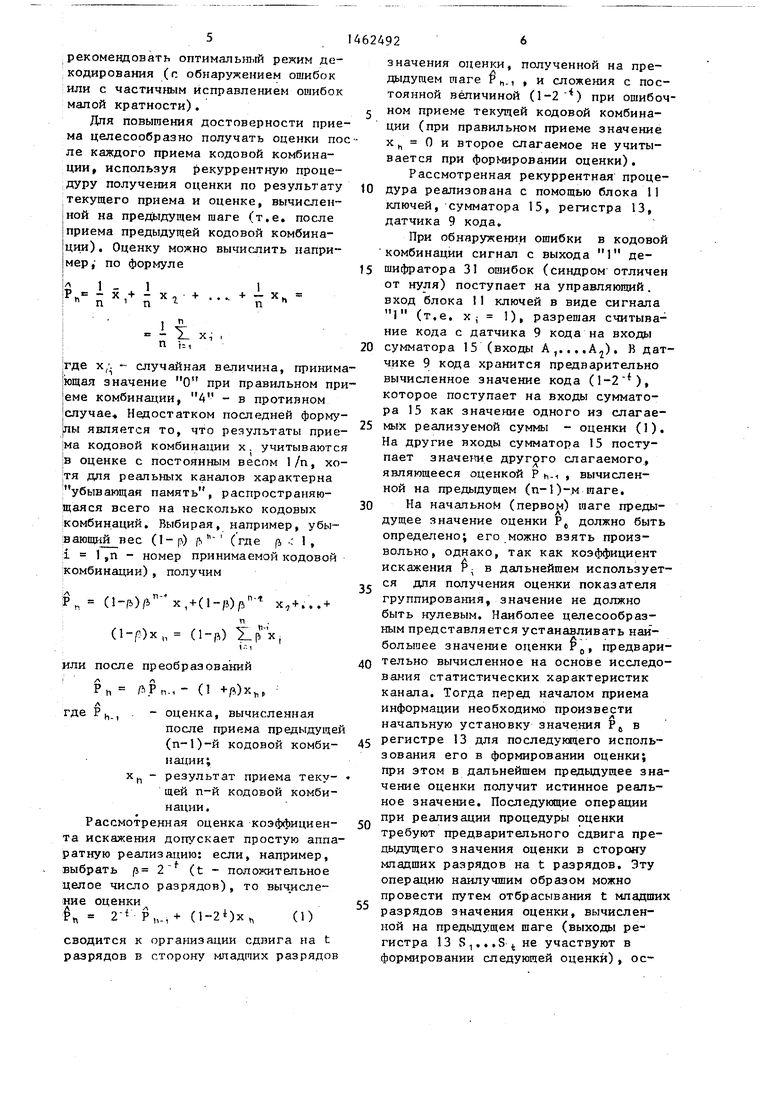

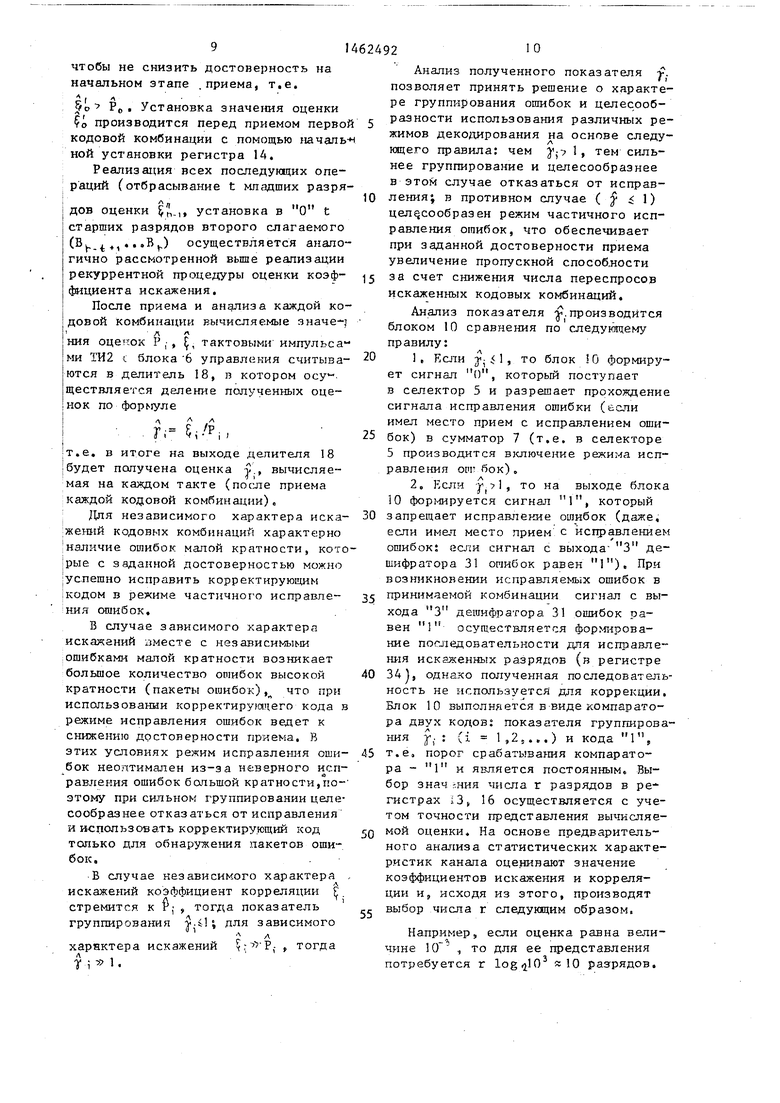

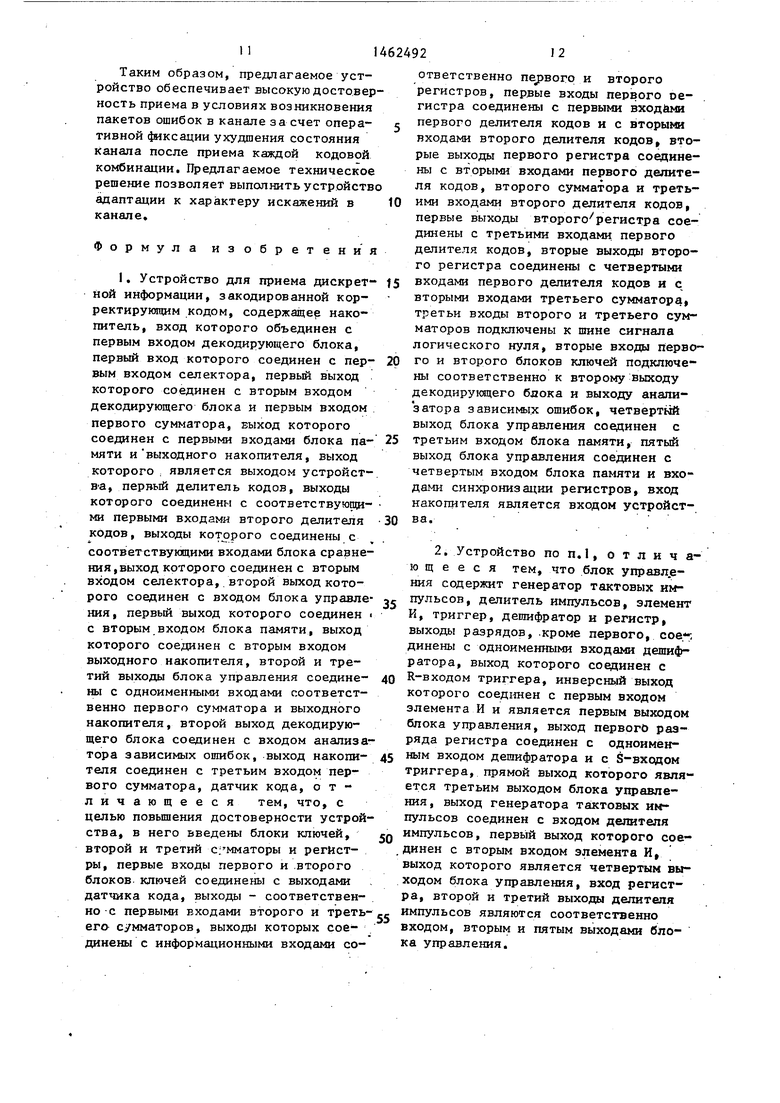

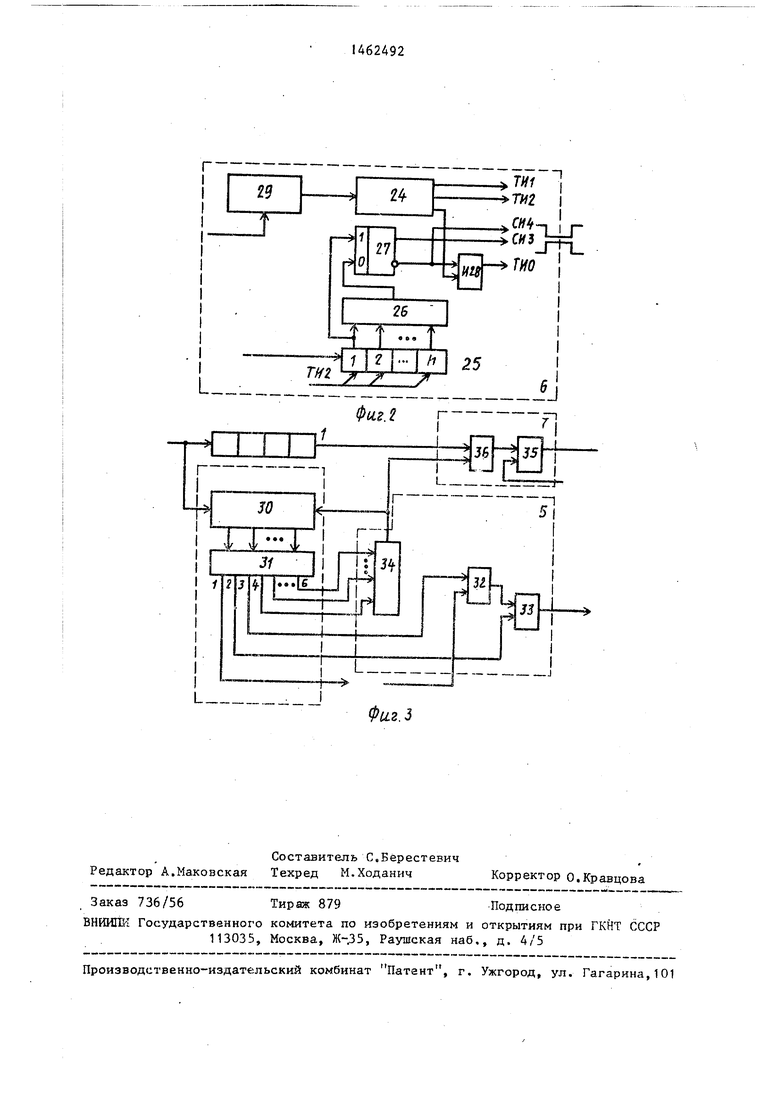

На фиг.. представлена структурная схема описываемого устройства; на фиг,2 - структурная схема блока уп- Ю равления; на фиг,3 - структурные схемы накопителя декодирующего блока, селектора, сумматора и связи между ними.

Устройство для приема дискретной информации, закодированной корректирующим кодом (фиг,1),- содержит на15

копитель 1, декодирующий блок 2, анаизатор 3 зависимых ошибок, выходной накопитель 4, селектор 5, блок 6 управления, первый сумматор 7, блок 8 памяти, датчик 9 кода, блок 10 сравнения, блоки 11 ,,12 ключей, регистры 13,14, второй 15 и третий 16 сумматоры, первый 17 и второй 18 делитеи кодов. На чертеже представлены также синхронный распределитель 19, блок 20 регистров и стартстопный аспределитель 21, образующие блок 8 памяти, и элемент И 22, образую- 30 щий вместе с элементом 23 задержки анализатор 3 зависимых ошибок.

Блок 6 управления (фиг,2) содер- ит делитель 24 импульсов, регистр 25, дешифратор 26, триггер 27, эле- 35 мент И 28 и генератор 29 тактовых импульсов.

Декодирующий блок, селектор и сумматор (фиг,3) содержат блок 30 деения на производящий полином, де- 40 ифратор 31 ошибок, элемент И 32, элемент ИЛИ. 33, регистр 34, элемент 35 и мажоритарный элемент 36,

Устройство работает следующим образом,45

На вход устройства в накопитель 1 с помощью тактовых импульсов ТИ 1 от блока 6 упраншения поэлементно поступает последовательность кодо- вых комбинаций с одновременным декодированием в декодирующем блоке 2, где производится деление принятой комбинации на производящий полином, определение синдрома и формирование последовательности для коррекции ис- 55 ажеиных разрядов,

В блоке 30 деления на производяий полином принятая кодовая комбинаия делится на гфоиаводяшцй полином

дл лу ра ся си си Ю1Ц на си яв

об фо си вы ис вс зу 4

20 ми ош ву да ци

25 лу

50

тел

ре есл ват ме

чии ром в р ция пул ся етс

тор ет оши ми сыв клю на фор ват дов емы ся 5 п вид лен

про код ля мир

Ю

15

30

5

0

5

5

для определения сиццрома ошибки. Полученный синдром по ступает на дешифратор 31 ошибок, в котором формируется на выходе I сигнал 1, если синдром не равен О, на выходе 2 - сигнал 1, если получен неисправля- Ю1ЦИЙ синдром, и на выходе 3 - сигнал 1, если получен исправляющий синдром. При этом выход 1 может являться, например,выходом схемы

объединения (элемента ИЛИ), которая формирует сигнал 1 при ненулевом синдроме; выход 2 может являться выходом схемы объединения всех не- исправлягощих синдромов; выход 3.- всех исправляющих синдромов используемого корректирующего кода. Выходы 4 - ( дешифратора 31 ошибок фор20 мируют по вычислительному синдрому ошибо-к, каждый из которых соответствует определенным искаженным разрядам, последовательность для коррекции этих искаженных разрядов, В по25 лученной корректирующей последова0

тельности с выходов 4

Л

6

регистр 34 поступают сигналы I, если разряд необходимо корректировать (исправлять), и О, если имел место правильный прием разряда.

При отсутствии ошибок или наличии необнаруживаемых ошибок (синдром равен О, последовательность в регистре 34 - набор О) комбинация через сумматор 7 тактовыми импульсами ТИ 1 с блока 6 переписывается в выходной накопитель 4 и выдается потребителю.

При обнаружении ошибок дешифратор 31 ошибок на выходе 1 формирует сигнал 1 (синцром не равен О - ошибка обнаружена), который тактовыми импульсами ТИ 2 с блока 6 переписывается в анализатор 3 и блок 11 ключей. Если ошибки исправляются, то на выходах 4 - 6 дешифратора 31 формируется корректирующая последовательность для исправления разрядов, в противном случае (неисправляемые ошибки) на выходе 2 формируется сигнал 1, который через селектор 5 поступает в регистр 25 блока 6- в виде признака о невозможности исправления ошибок.

Исправление ошибок селектором 5 производится одновременно с выдачей кодовой комбинации с выхода накопителя 1 через сумматор 7, При этом сформированная корректирующая посяедова10

1462492

тельность в регистре 34 синхронно с выдачей потребителю информации (сигналы ТИ I с блока 6) через сумматор 7 корректирует (исправляет инвертированием) разряды и одновременно изменяет значение синдрома для устранения влияния исправляемых разрядов на содержимое блока 30 деления на производящий полином,

В случае невозможности исправления ошибок дешифратор 31 ошибок формирует сигнал 1 на выходе 2, который через селектор 5 записывается в регистр 25 блока 6 как признак приема кодовой комбинации (1 - неисправляемый прием; О - прием с исправляемой, необнаруживаемой ошибкой или правильный прием).

Для пояснения дальнейшей работы устройства рассмотрим пример технической реализации блока б управления, в котором генератор 29 тактовых импульсов, синхронизируемый от первой

не установит триггер 27 в состояни О, в результате которого заверша ется блокировка (сброс сигнала СИЗ запрещается запись в блок 8 памяти и до момента записи первого разряд очередной комбинации в выходной накопитель 4 производится считывание комбинаций из блока 8 памяти в выходной накопитель 4 ()

С начала блокировки начинается этап приема участка комбинации и во становление порядка следования анал гично работе устройства приема с ре 15 тающей обратной связью и блокировко Этот этап характеризуется тем, что элементы принятых комбинаций записы ваются в блок 8 памяти, а их призна ки записываются в регистре 25 в виде сигнала О (прием без ошибок), или 1 (прием с неисправляемыми ошибками). При этом синхронно с при емом комбинаций производится сдвиг признаков импульсами ТИ2 в регистре

20

- iii jrionniv jr nniiyjijDUciMJi В регистре

решающей схемы (демодулятора и гене-. 25 25; в случае правипьного повторного

ратораУ, формирует опорную частоту (меандр) для получения тактовых импульсов управления. Делитель 24 импульсов формирует тактовые импульсы ТИО, ТИ1, ТН2 длительности тактовых импульсов соотносятся следующим образом:

О (- rwi разряда; f

TU Z

t кодовой комбинации (.).

Сигнал с селектора 5 (признаки приема кодовых комбинаций) поступают в регистр 25, информационные выходы которого подключены к дешифратору 26, представлягацему собой схему объединения (элемент ИЛИ), которая в случае равенства всех признаков О устанавливает триггер 27 в состояние О, Сигнал с выхода 1 триггера 27 в этот период запрещает запись информации в блок 8 памяти (сигнал СИЗ равен О),

В случае приема комбинации с неисправляемой ошибкой признак 1 записывается в регистр 25 с последующим сдвигом тактовыми импульсами ТИ2 блока 6 и одновременно устанавливает триггер 27 в состояние 1, что позволяет сфор,даровать сигнал СИЗ для блокировки выходного накопителя 4 и сигнал СИ4 для разрешения записи информации на длине блокировки в блок 8 памяти. Сигнал блокировки ШЗ будет на выходе блока 6 до тех пор, пока все признаки не будут равны О, т,е, пока дешифратор 26

приема вместо признака 1 (при условии , что первоначально имел место

. искаженный прием) записывается признак О с одновременной записью при30 нятой комбинагдш в блок 8 памяти,

В блоке 8 памяти сигнал СИ4 с тригге ра 27 открывает синхронный распределитель 19 (синхронизируемый от импульсов ТИ2 блока 6), определяющий

25 синхронизирующий регистр блока 20 . для записи комбинации.

В случае правильного повторного приема на длине блокировки все приз наки - О дешифратор 26 устанавли40 вает триггер 27 в состояние О,

прекращая блокировку выходного накопителя 4 и запись в блок 8 памяти. Одновременно блок 6 управления форми рует импульс ТИО на стартстопный

45 распределитель 21, который за время, значительно меньшее длительности сиг нала ТИ1, производит опрос регистров блока 20 и выдачу из них информации в выходной накопитель 4 до момента

gg записи первого разряда очередной ком бинации из сумматора 7,

В процесса приема информации (кодовых комбинаций) осуществляется оценка коэффициентов искажения и

55 корреляции для получения показателя группирования ошибок. Анализ показателя группирования ошибок позволяет определить характер искажения в канале (зависимый или независимый) и

10

не установит триггер 27 в состояние О, в результате которого завершается блокировка (сброс сигнала СИЗ), запрещается запись в блок 8 памяти, и до момента записи первого разряда очередной комбинации в выходной на копитель 4 производится считывание комбинаций из блока 8 памяти в выходной накопитель 4 ()

С начала блокировки начинается этап приема участка комбинации и восстановление порядка следования аналогично работе устройства приема с ре- 5 тающей обратной связью и блокировкой. Этот этап характеризуется тем, что элементы принятых комбинаций записываются в блок 8 памяти, а их признаки записываются в регистре 25 в виде сигнала О (прием без ошибок), или 1 (прием с неисправляемыми ошибками). При этом синхронно с приемом комбинаций производится сдвиг признаков импульсами ТИ2 в регистре

0

iii jrionniv jr nniiyjijDUciMJi В регистре

5 25; в случае правипьного повторного

25 25; в случае правипьного повторного

приема вместо признака 1 (при условии , что первоначально имел место

искаженный прием) записывается признак О с одновременной записью при30 нятой комбинагдш в блок 8 памяти,

В блоке 8 памяти сигнал СИ4 с триггера 27 открывает синхронный распределитель 19 (синхронизируемый от импульсов ТИ2 блока 6), определяющий

5 синхронизирующий регистр блока 20 . для записи комбинации.

В случае правильного повторного приема на длине блокировки все признаки - О дешифратор 26 устанавли0 вает триггер 27 в состояние О,

прекращая блокировку выходного накопителя 4 и запись в блок 8 памяти. Одновременно блок 6 управления формирует импульс ТИО на стартстопный

5 распределитель 21, который за время, значительно меньшее длительности сигнала ТИ1, производит опрос регистров блока 20 и выдачу из них информации в выходной накопитель 4 до момента

g записи первого разряда очередной комбинации из сумматора 7,

В процесса приема информации (кодовых комбинаций) осуществляется оценка коэффициентов искажения и

5 корреляции для получения показателя группирования ошибок. Анализ показателя группирования ошибок позволяет определить характер искажения в канале (зависимый или независимый) и

рекомендовать оптимальн1)1й режим декодирования (г. обнаружением ошибок или с частичным исправлением ошибок малой кратности).

Для повышения достоверности приема целесообразно получать оценки поле каждого приема кодовой комбинации, используя рекуррентную проце- ;дуру получения оценки по результату .текущего приема и оценке, вычислен- |ной на предыдущем шаге (т.е. после I приема предыдущей кодовой комбина- |ции), Оценку можно вычислить напри- |мер,- по формуле

1

|где X,: - случайная величина, приним |ющая значение О при правильном при |еме комбинации, 4 - в противном (случае Недостатком последней форму- лы является то, что результаты прие- |ма кодовой комбинации х. учитываются IB оценке с постоянным весом 1/п, хо- {тя для реальных каналов характерна убывающая память, распространяю- 1цаяся всего на несколько кодовых :комбинаций. Выбирая, например, убыдающий вес (1- р.)

11(где /i .: 1 ,

i 1 ,n - номер принимаемой кодовой комбинации), получим

ЗР. (1-р), + (1-/})- х, + ...+ (l-f)x, (1-э) i.

ИЛИ после преобразований

Р /.Рп- - (1 /)Х, л

где Р J, , - оценка, вычисленная

после приема предыдущей (п-1)-й кодовой комби- наци и J

х - результат приема теку- щей п-й кодовой комбинации.

Рассмотренная оценка коэффициента искажения допускает простую аппаратную реализацию: если, например, выбрать /5 2 (t - положительное целое число разрядов), то вычисление Оценки „ 2- Р„.,+ (1-2)х (1)

сводится к организации сдвига на t разрядов в сторону младших разрядов

10

15

20

25

30

5

0

5

0

5

значения оценки, полученной на предыдущем шаге .1 , и сложения с постоянной величиной (1-2) при ошибочном приеме текущей кодовой комбинации (при правильном приеме значение X О и второе слагаемое не учитывается при формировании оценки).

Рассмотренная рекуррентная процедура реализована с помощью блока 11 ключей, сумматора 15, регистра 13, датчика 9 кода.

При обнаружении ощибки в кодовой комбинации сигнал с выхода 1 дешифратора 31 ошибок (синдром отличен от нуля) поступает на управляющий, вход блока I1 ключей в виде сигнала 1 (т.е. Xi 1), разрешая считывание кода с датчика 9 кода на входы сумматора 15 (входы А,....А,,). В датчике 9 кода хранится предварительно вычисленное значение кода (1-2), которое поступает на входы сумматора 15 как значение одного из слагаемых реализуемой суммы - оценки (1). На другие входы сумматора 15 поступает значетаде другого слагаемого., являющееся оценкой Р ь--. , вычисленной на предыдущем (п-1)-м щаге.

На начальной (первом) щаге предыдущее значение оценки Р должно быть определено; его можно взять произвольно, однако, так как коэффициент искажения Р; в дальнейшем используется для получения оценки показателя группирования, значение не должно быть нулевым. Наиболее целесообразным представляется устанавливать наибольшее значение оценки Р, предварительно вычисленное на основе исследования статистических характеристик канала. Тогда перед началом приема информации необходимо произвести начальную установку значе:ния Р в регистре 13 для последующего использования его в формировании оценки; при этом в дальнейшем предьщущее значение оценки получит истинное реальное значение. Последующие операции при реализации процедуры оценки требуют предварительного сдвига предыдущего значения оценки в сторону младщих разрядов на t разрядов. Эту операцию наилучшим образом можно провести путем отбрасывания t младщих разрядов значения оценки, вычисленной на предьздущем шаге (выходы регистра 13 S,...S не участвуют в формировании следующей оценки), ос1

20

тальные (г - t) разрядов оценки (вы- ходы регистра 13 S., ,...S,) подклю- чить к соответствующим (г - t) входам второго слагаемого сумматора 15 (В ,., ,B(..t ) , а оставтиеся свободными t входов старгаих разрядов второго слагаемого (входы сумматора 15 Bh-t ...В) установить в состояние О (г - общее число разрядов, необходимых для формирования оценки с заданной точностью), В связи с тем, что указанные операции выполняются постоянно, то подобные действия (Сдвиг в сторону младших разрядов на t разрядов, отбрасывание t младших разрядов, обнуление t старших разрядов, сложение и т.д.) целесообразно реализовать с помощью жесткой логики ( как предложено в устройстве) , а не программным путем,

Таким образом, на выходе регистра 13 (выходы S...sp будет сформирована текущая оценка коэффициента искажения, вычисляемая на каждом такте (пос-25 ле приема очередной кодовой комбинации).

Анализатор 3 зависимых ошибок функционирует по правилу: при поступлении на вход двух смежных 1 на выходе элемента И 22 - последователь-30 ность при поступлении трех .смежных 1 на выходе элемента VI 22 - 011, при поступлении j смежных

U-t)

на выходе элемента И 22 - оГГГГГТ. Таким образом, анализатор 3 формирует последовательность смежных искаженных кодовых комбинаций. Последовательность смежных искажений кодовых комбинаций представляет собой случайную величину С ,, принимагадую значение О при отсутствии двух смежных искаженных кодовых комбинаций в противном случае.

Оценка коэффициента корреляции производится по формуле

Л -к

К , J- число искаженных смежных кодрвы х комбинаций среди К искаженных кодовых комбинаций на объеме контролируемой выборки п.

Применение аналогичной рекуррентной процедуры для оценки коэффициента корреляции требует следующих очевидны, преобразований:

146

35

40

45

50

-

55

Ki

к

- К/Г1 . , л К/п - /Р

8

0

Л

где f - оценка вероятности возникновения искаженных смежных кодовых колебаний;

Л

Р - оценка коэффициента искажения, которая вычисляется согласно (Ос помощью датчика 18 кодов, блока 11 ключей, сумматора 15, penict- ра 13.

Оценку коэффициента корреляции производят следующим образом,

Случайная величина С., формируемая анализатором 3 ошибок, может быт испсшьзована для вычисления оценки согласно рассмотренной вьш1е рекуррентной процедуры, т,е, аналогично (1) получим

Е -{. л .

2 .,

.(1-2-),

(2)

что реализуется с помощью анализатора 3 ошибок, блока 12 ключей, сумматора 16, регистра 14, датчика . кода.

Формирование оценки коэффициента корреляции производится по оассмот30

л

hл . ,Л

/РГ,

35

40

5

ренной выше формуле ;, /Р делителем 17 путем деления значения кода

г л

назначение кода Р. При этом,

и л

так как оценки Р„ определены

после приема каждой кодовой комбинаI

|ции, то и оценка будет вычислять|Ся после приема каждой кодовой комбинации .

При наличии смежных искаженных кодовых комбинаций сигнал с выхода анализатора 3 ошибок поступает на управлякнций вход блока 12 ключей в виде сигнала 1 (С; 1),.разрешая считывание кода с датчика 5 кода на входы сумматора 16 А,.,Ар.

На другие входы сумматора 16

поступают значения

(входы B.j,..B

0

другого слагаемого оценка ), На начальном этапе приема оценки ё

можно выбрать правильно, так как в дальнейшем на следующих шагах она примет истинное значение, однако с запасом можно рекомендовать такой

- f

5 выбор о, чтобы обеспечить включение

режима декодирования, наиболее целесообразного для плохого состояния канала, т,е, обнаружения ошибок ,

10

чтобы не снизить достоверность на начальном этапе .приема, т.е.

fЛ

о PC. Установка значения оценки

ff o производится перед приемом первой 5

кодовой комбинации с помощью началь-н

ной установки регистра 14.

Реализация всех последугадих операций (отбрасывание t мпадших разряI дов оценки h-i установка в О t I старших разрядов второго слагаемого ( - осуществляется аналогично рассмотренной выше реализации рекурреитной процедуры оценки коэф- циента искажения.

I После приема и анализа каждой ко- довой Комбинации вычисляемые значе }

I лл

ния оценок Р;, , тактовыми импульса ми ТИ2 t блока 6 управления считываются в делитель 18, в котором осу-, ществляется деление полученных оценок по формуле

лАЛ

Г . Р /Р

(1 1 /i i )

15

20

т.е. в итоге на выходе делителя 18 Iбудет получена оценка ., вычисляемая на каждом такте (пос-ле приема каждой кодовой комбинации).

Для независимого характера иска- :жещ1й кодовых комбинаций характерно :наличие ошибок малой кратности, кото- рые с заданной достоверностью можно |успешно исправить корректирующим 1кодом в режиме частичного исправления ошибок.

В случае зависимого характера искажений вместе с независимыми ошибками малой кратности возникает большое количество ошибок высокой кратности (пакеты ошибок), что при использовании корректиругадего кода в режиме исправления ошибок ведет к снижению достоверности приема. В этих условиях режим исправления оши- бок неоптимален из-за неверного исправления ошибок бапьшой кратности,по- этому при сильном группировании целесообразнее отказаться от исправления и использовать корректирующий код только для обнаруже шя пакетов ошибок.

В случае независимого характера , искажений коэффициент корреляции . стремится КГ;, тогда показатель группирования для зависимого

харнктера искажений тогда

.

146249210

Анализ полученного показателя f. позволяет принять решение о характере группирования ошибок и целесообразности использования различных режимов декодирования на основе следующего правила: чем 7 I , тем сильнее группирование и целесообразнее в этом случае отказаться от исправления j в противном случае ( J 1) целесообразен режим частичного исправления ошибок, что обеспечивает при заданной достоверности приема увеличение пропускной способности за счет снижения числа переспросов искаженных кодовых комбинаций.

Анализ показателя j.производится блоком 10 сравнения по следующему правилу:

1.Еа1и у i 1 , то блок 0 формирует сигнал О, который поступает

в селектор 5 и разрешает прохождение сигнала исправления ошибки (если имел место прием с исправлением оши- 25 бок) в сумматор 7 (т.е. в селекторе 5 производится взшючение режима исправления ошт бок).

2.Если Jf i, то на выходе блока 10 фор шруется сигнал 1, который запрещает исправление ошибок (даже, если имел место прием с исправлением ошибок: есгш сигнал с выхода 3 дешифратора 31 ошибок равен 1). При возникновении исправляемых ошибок в принимаемой комбинации сигнал с выхода 3 дешифратора 3 ошибок равен осуществляется формирование погледовательности для исправления искаженных разрядов (в регистре 34 J, однако полученная последовательность не используетсй для коррекции. Блок 10 выполняется в-виде компаратора двух кодов: показателя группирова30

35

40

45

50

55

ния Tf.; (i 1,2,...) и кода 1, т.е. порог срабатывавши компаратора - 1 и является постоянным. Выбор знач -ния числа г разрядов в регистрах 13, 16 осуществляется с учетом точности представления вычисляемой оценки На основе предварительного анализа статистических характеристик канала оценивают значение коэффициентов искажения и корреляции и, исходя из этого, производят выбор числа г следукщим образом.

Например, если оценка равна величине 10

г

то для ее представления

потребуется г log,jlO я 10 разрядов,

ния Tf.; (i 1,2,...) и кода 1, т.е. порог срабатывавши компаратора - 1 и является постоянным. Выбор знач -ния числа г разрядов в регистрах 13, 16 осуществляется с учетом точности представления вычисляемой оценки На основе предварительного анализа статистических характеристик канала оценивают значение коэффициентов искажения и корреляции и, исходя из этого, производят выбор числа г следукщим образом.

Например, если оценка равна величине 10

г

то для ее представления

потребуется г log,jlO я 10 разрядов,

11

Таким образом, предлагаемое устройство обеспечивает высокую достовеность приема в условиях возникновения пакетов ошибок в канале за счет опера- тивной фиксации ухудшения состояния канала после приема каждой кодовой комбинации. Предлагаемое техническо решение позволяет выполнить устройст адаптации к характеру искажений в

канапе.

Формула

изобретения

I. Устройство для приема дискрет ной информации, закодированной корректирующим кодом, содержащер накопитель, вход которого объединен с первым входом декодирующего блока, первый вход которого соединен с первым входом селектора, первый выход которого соединен с вторым входом декодирующего блока и первым входом первого сумматора, выход которого соединен с первыми входами блока памяти и выходного накопителя, выход которого ; является выходом устройст- В а, первый делитель кодов, выходы которого соединены с соответствуюсци- ми первыми входами второго делителя кодов, выходы которого соединены с

,

соответствующими входами блока сравнения, выход которого соединен с вторым входом селектора, второй выход которого соединен с входом блока управления , первый выход которого соединен с вторым входом блока памяти, выход которого соединен с вторым входом выходного накопителя, второй и третий выходы блока управления соединены с одноименными входами соответственно первого сумматора и выходного накопителя, второй выход декодирующего блока соединен с входом анализатора зависимых ошибок, выход накопи- теля соединен с третьим входом первого сумматора, датчик кода, отличающееся тем, что, с целью повьпления достоверности устройства, в него введены блоки ключей, второй и третий с; мматоры и регистры, первые входы первого и .второго блоков, ключей соединены с выходами датчика кода, выходы - соответственно с первыми входами второго и треть- era с/мматоров, выходы которых соединены с информационными входами со

12

с10

20

25

30

ts

5 Q

35

0

ответственно первого и второго регистров, первые входы первого ое- гистра соединены с первыми вхсдйми первого делителя кодов и с вторыми входами второго делителя кодов вторые выходы первого регистра соединены с вторыми входами первого делителя кодов, второго сумматора и третьими входами второго делителя кодов, первые выходы второго регистра соединены с третьими входами, первого делителя кодов, вторые выходы второго регистра соединены с четвертыми входами первого делителя кодов и с вторыми входами третьего сумматора, третьи входы второго и третьего сумматоров подключены к шине сигнала логического нуля, вторые входы первого и второго блоков ключей подключены соответственно к второму выходу декодирующего блока и выходу анализатора зависимых ошибок, четвертый выход блока управления соединен с третьим входом блока памяти, пятый выход блока управления соединен с четвертым входом блока памяти и входами синхронизации регистров, вход накопителя является входом устройства,

2, Устройство по П.1, отличающееся тем, что блок управл.е- ния содержит генератор тактовых импульсов, делитель импульсов, элемент И, триггер, дешифратор и регистр, выходы разрядов, .кроме первого, сое.-; динены с одноименными входами дешифратора, выход которого соединен с R-входом триггера, инверсный выход которого соед1шен с первым входом элемента И и является первым выходом блока управления, выход первого разряда регистра соединен с одноименным входом дешифратора и с S-входом триггера, прямой выход которого является третьим выходом блока управления, выход генератора тактовых импульсов соединен с входом делителя импульсов, первый выход которого соединен с вторым входом элемента И, выход которого является четвертым выходом блока управления, вход регистра, второй и третий выходы делителя импульсов являются соответственно входом, вторым и пятым выходами блока управления.

I.,

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1601754A1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1709544A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1716610A2 |

| Декодер линейного кода | 1986 |

|

SU1405118A1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

Изобретение относится к электросвязи и может быть использовано в системах передачи информации с решающей обратной связью. Цепь изобретения - повышение достоверности устройства. Устройство для приема дискретной информации, закодированной кор- ректирующим кодом,содержит накопитель 1, декодирующий блок 2, анализатор 3 зависимых овшбок, выходной накопитель 4, селектор 5, блок 6 управления, первый сумматор 7, блок В памяти, датчик 9 кода, блок 10 сравнения, блоки 11,12 ключей, регистры 13,14, второй 15 и третий 16 сумматоры, первый 17 и второй 18 делители кодов. 1 з.п. ф-лы, 3 ил. а

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1978 |

|

SU680189A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гибкий шланг | 1947 |

|

SU72022A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-10—Подача