1

Предлагаемый цифровой интегратор относится к цифровым вычислительным устройствам, в которых для вычисления интеграла используются приращения функций.

Известны цифровые интеграторы последовательного типа, содержащие сумматоры и регистры. Однако такие схемы при последовательной обработке каждого разряда функций и приращений имеют большое время интегрирования.

Цель предлагае.мого изобретения заключается в увеличении быстродействия и точности цифрового интегратора.

В предлагаемом цифровом интеграторе эта цель достигается путем использования параллельных регистров и сумматоров, а также тем, что для умножения приращений используются два параллельных сумматора, которые объединяются управляющими сигналами в один сумматор для суммирования и умножения функций.

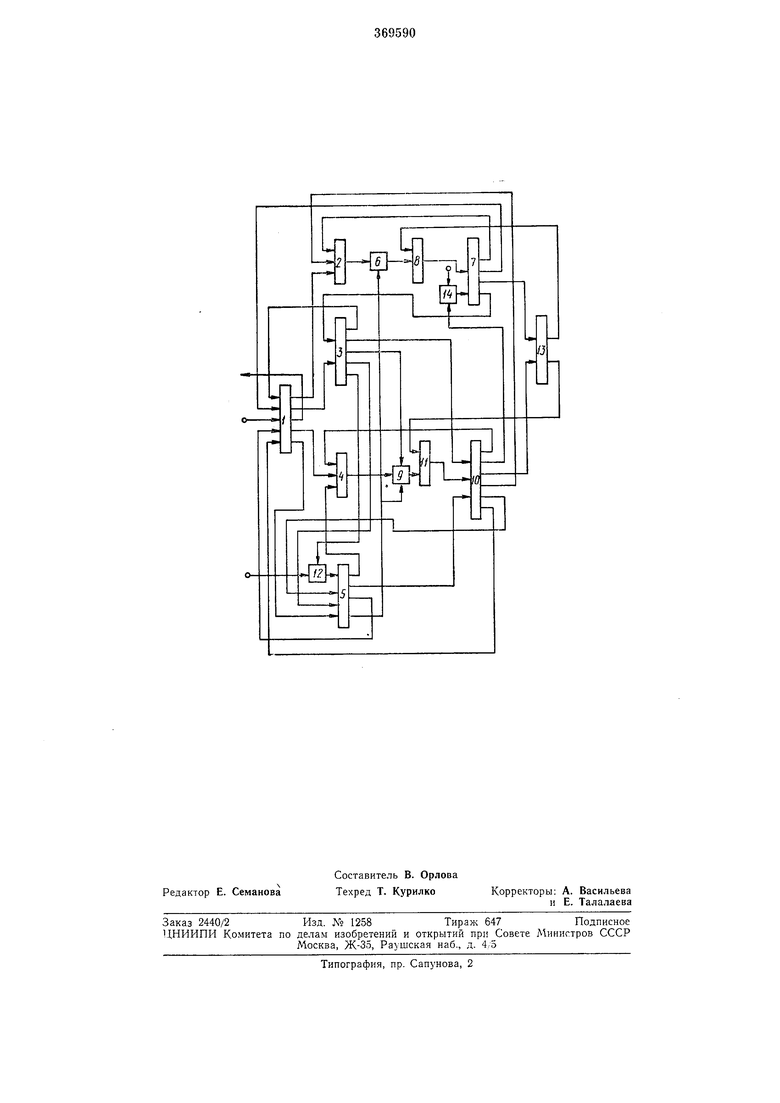

На чертеже представлена блок-схема интегратора.

Буферный регистр У является регистром, через который происходит обмен информацией цифрового интегратора. Выходы буферного регистра соединены с входами первого регистра множимого 2 для передачи приращений подынтегральной функции, старших разрядов подынтегральной функции и старших разрядов

остатка. Выходы буферного регистра / также соединены со входами первого регистра множителя 5 для передачи приращений переменной интегрирования. Кроме того, выходы буферного регистра соединены со входами второго регистра множимого 4 для передачи приращений подынтегральной функции и младщих разрядов остатка. Соединение выходов буферного регистра У со входами второго регистра множителя 5 используется для передачи приращений переменной интегрирования. .Выходы первого регистра множимого 2 через вентили 6 умножения первого сумматора 7 соединены со входами промежуточного регистра S первого сумматора таким образом, что в зависимости от управляющего сигнала, подаваемого с выходов т младших разрядов второго регистра множителя 5 на управляющие входы вентилей 5 умножения первого сумматора, число, записанное в первом регистре множимого 2, может быть передано либо в прямом коде, либо в дополнительном коде, либо со сдвигом влево, т. е. умножено на т младших разрядов числа, находящегося во

втором регистре .множителя 5. Аналогично, выходы второго регистра множимого 4 через вентили 9 умножения второго сумматора 10 соединены со входами промежуточного регистра // второго сумматора таким образом, что в

зависимости от управляющего сигнала, подаваемого либо с выходов т младших разрядов первого регистра множителя 3, либо с выходов т младших разрядов второго регистра множителя 5 на управляюш.ие входы вентилей 9 умножения второго сумматора W, число, записанное во втором регистре множимого 4, может быть передано либо в прямом коде, либо в дополнительном коде, либо со сдвигом влево. Выходы промежуточного регистра 8 первого сумматора 7 соединены со входами первого сумматора, а выходы промежуточного регистра 11 второго сумматора 10 соединены со входами второго сумматора.

Первый регистр множителя 3 и второй регистр множителя 5 являются сдвигающими регистрами, в которых информация может сдвигаться вправо на m разрядов, причем выходы т младших разрядов первого регистр а множителя 3 через управляюш,ие вентили сдвига 12 соединены цепью сдвига с т старшими разрядами второго регистра множителя 5, так что эти регистры могут в зависимости от сигналов управления, подаваемых на управляющие вентили сдвига 12, объединяться в один сдвигающий регистр для умножения числа, находящегося в первом регистре множимого 2, на число, находящееся в объединенном сдвигающем регистре, либо для умножения числа, старшие разряды которого находятся в первом регистре множимого 2, а младшие - во втором регистре множимого 4, на число в объединенном сдвигающем регистре.

Выходы первого регистра множителя 3 соединены со входами буферного регистра / для выдачи информации из цифрового интегратора. Кроме того, выходы первого регистра множителя 5 соединены со входами второго сумматора 10 для суммирования полноразрядиых чисел. Выходы первого регистра множителя 3 соединены со входами второго регистра множителя 5 для передачи чисел.

Для промежуточного хранения информации выходы первого сумматора 7 соединены со входами старших разрядов промежуточного регистра 13 (выходы тех же разрядов промежуточного регистра 13 соединены со входами промежуточного регистра 8 первого сумматора 7). Выходы второго сумматора 10 соединены со входами младших разрядов промежуточного регистра 13 (выходы тех же разрядов промежуточного регистра 13 соединены со входами промежуточного регистра // второго сумматора 10).

Первый сумматор 7 своими выходами соединен со входами первого регистра множимого 2 для того, чтобы старшие разряды полноразрядного числа, находящегося в первом и втором сумматорах 7 и 10, могли быть переданы из первого сумматора 7 в первый регистр множимого 2 для последующего умножения или суммирования. Для этой же цели выходы второго сумматора 10 соединены со входами второго регистра множимого 4.

Для сохранения младших разрядов произведения выходы т младших разрядов первого сумматора 7 соединены со входами т старших разрядов первого регистра множителя 3. Для этого же выходы m младших разрядов второго сумматора 10 соединены со входами т старших разрядов второго регистра множителя 5.

Выходы первого и второго сумматоров соединены со входами буферного регистра / для вывода информации из цифрового интегратора. Чтобы передать старшие разряды произведения для последующего суммирования, выходы второго сумматора /О соединены со входами первого регистра множимого 2. Выходы m старших разрядов второго сумматора соединены цепями переноса через управляющие вентили переносов 14 с младщими разрядами первого сумматора 7. Это позволяет объединять в нужное время первый и второй сумматоры в один сумматор.

Предлагаемый цифровой интегратор может выполнить следующий алгоритм численного интегрирования; метод квадратных парабол

V .i) (ур, + Y 7 Уpk,,) V у,, JJ

+

+ -(V Ур,,, V у,,, - V Ур,, V у,, +

+ 0..,,

который выполняется в следующей последовательности:

П. , 7У,,,,

n, Vyp,,-Vy,,,j, 2. П,-П,

-nkS..

2,гп, + о,,,

Vi P«(;4l) Zj Pi + Т ( + 1)

. + bДля реализации метода трапеций

)vy,v,i) +

/,1)()

+ 0,

г

ВЫПОЛНЯЮТСЯ пункты 4, 5, б алгоритма (2).

Алгоритм (2) реализуется в цифровом интеграторе в следующей последовательности. Устройством управления, которое на схеме не показано, подается последовательность управляющих сигналов, по которым в буферный

регистр 1 из запоминающего устройства поступают приращения ypki и Vz/ps . Затем приращение Vi/pu передается в первый регистр множимого 2, а приращение Vz/ps -

во второй регистр множимого 4. После этого

в буферный регистр / поступают приращения Vyqkf и , откуда приращение

передается затем в первый регистр множителя 3, а приращение Vz/, - во второй регистр множителя 5.

После этого начинается одновременное умножение приращения ypkn+iy находящегося в первом регистре множимого 2, на приращение Vt/gki , находящееся во втором регистре множителя 5, и приращения ypk{ , находящегося во втором регистре множимого 4, на приращение Vz/ ,, находящееся в первом регистре множителя 3.

Получение произведения

n: Vy;,,,ft,

происходит следующим образом.

В соответствии с кодом, записанным в m младщих разрядах второго регистра множителя 5, приращение находящееся в первом регистре множимого 2, через вентили 6 умножения первого сумматора 7 и промежуточный регистр первого сумматора передается в сумматор прямым или обратным кодом или со сдвигом влево.

Затем приращение Vtjqki , находящееся во втором регистре множителя 5, сдвигается на т разрядов вправо, одновременно на т разрядов вправо сдвигается содержимое первого сумматора 7, причем младщие разряды из сумматора записываются в старщие разряды первого регистра множителя 3.

После этого умножения повторяются в течение определенного времени, пока не будет получена величина ТТ..

После окончания умножения старщие разряды произведения П1 располагаются в первом сумматоре 7, а младшие разряды - в первом регистре множителя 3.

Аналогично, во втором сумматоре 10 происходит умножение приращения Vt/D, находящегося во втором регистре множимого 4, на приращение , находящееся в первом регистре множителя 3. После выполнения умножения старщие разряды произведения Пз расположены во втором сумматоре 10, а младщие - во втором регистре множителя 5.

Для получения разности Ei ni-Tlz старшие разряды произведения Uz передаются из второго сумматора 10 в первый регистр множимого 2, а младщие разряды - из второго регистра множителя 5 во второй регистр множимого 4. Первый и второй сумматоры 7 и 10 подачей управляющих сигналов на управляющие вентили переносов 14 объединяются на один сумматор.

Младщие разряды произведения П1 из первого регистра множителя 3 передаются во второй сумматор 10, затем произведение Пг через вентили 5 и 9 умножения первого и второго сумматоров 7 и 10 и промежуточные регистры 8 и 11 первого и второго сумматоров вычитаются в первом и втором сумматорах из произведения Пь Для получения величины

п,..

разность Si из первого и второго сумматоров переписывается в первый и второй регистры множимого 2 т 4. Одновременно из буферного регистра / в первый и второй регистры мноО 1

жителя J и о записывается число в двоичном коде (старшие разряды записываются в первый регистр множителя 3, а младшие - во второй регистр множителя 5).

Через управляющие вентили сдвига 12 по управляющему сигналу первый и второй регистры множителя 3 н 4 объединяются в один сдвигающий регистр.

При умножении анализируются т младших

1

разрядов числа, находящиеся во втором

регистре множителя 5. Результат анализа передается на вентили 5 и 9 умножения первого

и второго сумматоров, через которые множнмое передается в промел уточные регистры первого и второго сумматоров и затем в первый и второй сумматор. Затем множитель сдвигается в первом и втором регистрах множителя 5 и 5 на т разрядов. Цикл умножения повторяется определенное время до образования величины Пз.

Во время умножения буферный регистр / поступает остаток интеграла , полученный на предыдущем щаге. После окончания умножения остаток Ozki из буферного регистра / поступает во второй множимого 4 и затем через вентили 5 умножения второго сумматора и промежуточный регистр второго сумматора суммируется в объединенном первом и втором сумматоре с величиной Пя, образуя So , . Результат суммирования записывается из сумматоров в промежуточный регистр 13 для промежуточного хранения.

Для образования нового значения подынтегральной функции

Ур(1-1)+

55

приращения Vr/pft,.,) и Vz/p из запоминающего устройства поступают в буферный регистр /, откуда Vy,,i; засылается во второй регистр множителя 5, а Vr/pj jj- в первый регистр мнол ителя 3. Вслед за этим в буферный регистр / записывается i/rft() и затем

старшие разряды подынтегральной функции переписываются в пергый регистр множимого

7

2, а младшие - во втором регистре множимого 4. откуда функция ypk,) через вентили 6 и 9 умножения первого и второго сумматоров и промежуточные регистры первого и второго сумматоров суммирз ется в первом и втором сумматорах с приращением VJ/PU , выдаваемым на второй сумматор 10 из второго регистра множителя 5. Затем t/ps записывается из первого и второго сумматоров в буферный регистр } для вывода нового значения подынтегральной функции в запоминающее устройство, а также в первый и второй регистры множимого 2 и 4. Одновременно приращение Vi/pft() сдвигается в первом регистре множителя 3 на один разряд вправо, образуя величину - Vi/pA(,-+j), переписывается во втором

регистре множителя 5 для последующего суммирования с ypki . Через вентили б и 9 умножения первого и второго сумматоров и промежуточные регистры первого и второго сумматоров ypki суммируется на первом и втором

сумматорах с приращением - V(/pft(;,j, находящимся в регистре 5, для образования величины

S

g - yPkt+ У УРК(1 + 1Г

Полученная сумма переписывается из первого и второго сумматоров в первый и второй регистры множимого 2 и 4. Одновременно из промежуточного регистра 13 в промежуточные регистры первого и второго сумматоров переписывается величина Ез, откуда она переписывается в первый и второй сумматоры 7 и 10.

Одновременно с этим в буферный регистр / из запоминающего устройства заносится приращение Учш+гу Из буферного регистра оно пересылается во второй регистр множителя 5.

После этого начинается умножение величины ЕЗ, находящейся в первом и втором регистрах множимого 2 и 4, на приращение ), находящееся во втором регистре множителя 5. Так как к этому времени в сумматоре была записана величина 22, то в результате умножения образуется искомое приращение

V2,,+j)S3Vi/,., + 2.

или, учитывая выражение (2),

V2ft(,- + i) + - Vypft(i,) (i + i)) +

+ -( - ypit X

12

X 7Уqkf l+Ozk

После окончания умножения приращение интеграла Vz.jj передается в буферный регистр } и далее в запоминающее устройство для дальнейшего использования.

Предмет изобретения

Пифровой интегратор, содержащий буферный регистр, выходы которого соединены с первым и вторым регистрами множимого и множителя, выход первого пегистра множимого через вентили, вторые входы которых подключены ко второму регистру множителя, связан с промежуточным регистром первого сумматора, первый выход первого регистра множителя соединен с буферным регистром, второй - с управляющими вентилями сдвига,

выходы которых через второй регистр множителя подключены ко второму регистру множимого, а третий - с вентилями, вторые и третьи входы которых связаны со вторыми регистрами множимого и множителя, а выходы - с промежуточным регистром второго сумматора; выход промежуточного регистра первого сумматора соединен с первым сумматором, выходами подключенным к первым регистрам множимого и множителя, к буферному регистру; выход промежуточного регистра второго сумматора соединен со вторым сумматором, выходами подключенным к буферному регистру, ко вторым регистрам множимого и множителя и к управляющим вентилям переносов, выходы которых соединены с первым сумматором, отличающийся тем, что, с целью повышения быстродействия, точности вычисления, он содержит дополнительный промежуточный регистр, входами подключенный к первому и второму сумматорам, а выходами - к промежуточным регистрам первого и второго сумматоров; третий и четвертый выходы первого регистра множителя соединены соответственно со вторым сумматором и со вторым

регистром множителя, выходы которого связаны с буферным регистром и со вторым сумматором, выходом подключенным к первому регистру множимого.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Цифровой интегратор | 1975 |

|

SU637833A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1972 |

|

SU357561A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для умножения | 1975 |

|

SU1206773A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU313828A1 |

| Цифровой интегратор | 1980 |

|

SU879586A1 |

Авторы

Даты

1973-01-01—Публикация