1

Изобретение относится к цифровым частотным дискриминаторам, используемым в радиоизмерительной технике, в частности, для измерения частоты рассогласования в цифровых следящих измерителях.

Известны цифровые частотные дискриминаторы, содержащие формирователь мерных интервалов, два вентиля, счетчик, регистр опорного числа, коммутатор и буферный каскад.

Такие цифровые частотные дискриминаторы сочетают высокую точность измерений частоты рассогласования с большим быстродействием и технически просто сопрягаются с цифровыми сглаживающими цепями цифровых динамических следящих систем.

Однако иекоторым недостатком известных дискриминаторов при использовании их в следящих системах является запаздывание на время выдачи выходной величины частоты рассогласования, измеряемой дискриминатором на мерном интервале А, поскольку выходная величина рассогласования в силу физической реализуемости выдается в конце мерного ийтервала At, тогда как истинное значение величины рассогласования при линейном законе его изменения соответствует середине мерного интервала. Это запаздывание, эквивалентное включению в цепь обратной связи цифровой

д/ следящей системы лин1П1 задержки иа

приводит к ухудшению точности оцеики выделяемой частоты и уменьшению запаса устойчивости цифровой следящей системы, что не позволяет в ряде случаев реализовать минимальную шумовую полосу следящей системы, а следовательно, и обеспечить минимальную дисперсию оцеики измеряемой частоты.

Цель изобретения - повышение точности оценки частоты рассогласования цифровым частотным дискримииатором. Для этого в предлагаемый цифровой частотный дискриминатор введены ключевые каскады и сумматор, причем входы ключевых каскадов подключены к выходу счетчика и к выходу буферного каскада, выход ключевых каскадов - к первому входу сумматора, второй вход которого соединеи с выходом реверсивного счетчика, а выход подключен ко входу коммутатора. С помощью такого включения производится коррекция выходиой величины дискриминатора, эквивалентиая «прпвязке ее к середине мерного интервала, что практически страияет запаздывание.

Коррекция выходной величины дискриминатора осуществляется за счет знания информации о предыдущем значении величины рассогласования. Принципиальная возможность такой коррекции основана на том, что в цифровых дискриминаторах величина мерного интервала Д/ всегда выбирается гораздо меньшей величины интервала заметного изменения измеряемого параметра, в частности частоты измеряемого сигнала.

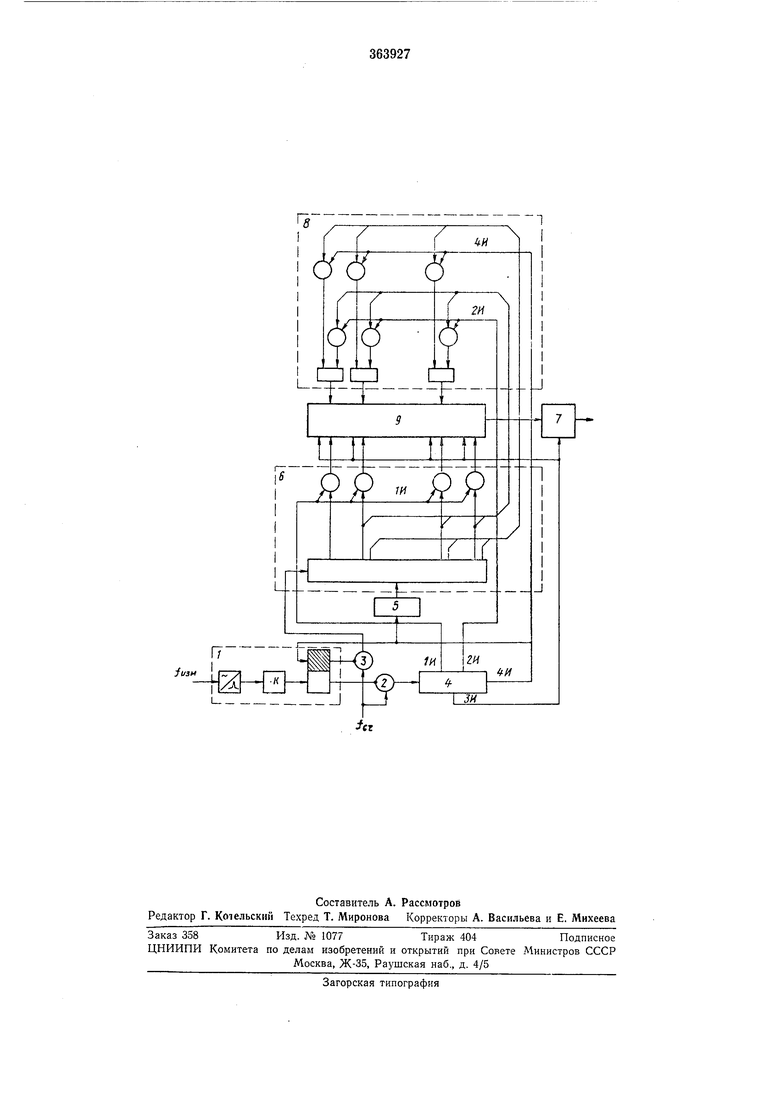

На чертеже дана схема предлагаемого цифрового частотного дискриминатора, на когорой обозначено:

/ - формирователь мерных иитервалов; 2, 3 - вентили; 4 - буферный каскад; 5-регистр опорного числа; 6 - счетчик; 7 - коммутатор; 8 - ключевые каскады; 9 - сумматор.

При алгебраическом суммировании выходной величины дискриминатора равной разности между числом счетных импульсов в мерном интервале измеряемой частоты и числом счетных импульсов в мерном интервале эталонной частоты, с полуразностью текущей величины рассогласования и предыдущего значения этой величины образуется величина рассогласования, равная

A,yV/ д/V, + -- (ДУУ,-Д,1)

Д/V,-Ь Д/У;- уАЛ/,-, .

Эта величина рассогласования, абсолютно строго соответствующая величине рассогласования в момент окончания мерного интервала

//+1

Д/; измна ннтервале- / --

i.

линейном законе изменения величины рассогласоваиия, гораздо точнее, чем величина ДЛ/, , характеризует величину рассогласования в момент времеии Д/ и для общего случая изменения закоиа измеряемой частоты.

Работа предлагаемого цифрового дискриминатора протекает следующим образом.

При открывании вентиля 2 импульсы с частотой fj;,, поступают на буферный каскад 4, который выдает управляющие импульсы И-4// для реализации выщеописаиного алгоритма вычисления Д/У/ . Импульс 1Я вводит со счетчика 6 в сумматор 9, где производится вычитание ДЛ/,-ДЛ/j-i . С очередным импульсом 2Я через ключевые каскады I в сумматор 9 вводится величина Н-ДЛ/;.

После сложения в сумматоре 9 формируется Д/У;, которая следующим импульсом 3// через коммутатор 7 выдается на выход дискриминатора. Кроме того, импульс ЗЯ устанавливает в исходное (нулевое) состояние все разряды сумматора 9. Импульсом 4Я в сумматор

9 вводится число - -AN в качестве априорной информации для следующего цикла измерений. Этот управляющий импульс подготавливает счетчик 6 к измерению, вводя в него через регистр 5 опорного числа поправку Ло, которая позволяет получить число +ДЛ/;

/V; - yVo, после очередного интервала измерения. Кроме того, импульс 4Я устанавливает триггер формирователя / мернЕлх интервалов в единичное состояние, открывай счетчик 6 для очередиого измерения.

Таким образом, цикл измерений непрерывно повторяется, а сумматор в каждом цикле измерения xpaiHiT величину предыдущего замера в виде- ДЛ/г-1ДЛЯ получения несмещениой оценки величины рессогласования.

П р е д м ет и з о б р е т е и и я

Цифровой частотный дискриминатор по авт. св. jY° 313278, отличающийся тем, что, с целью иовыщения точиости оценки частоты рассогласования, в него дополнительно введеиы ключевые каскады и сумматор, иричем входы ключевых каскадов подсоединены к выходу счетчика и к выходу буферного каскада, выход ключевых каскадов - к первому входу сумматора, второй вход которого соединен с выходом счетчика, а выход подключен ко входу коммутатора.

iu3H

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1971 |

|

SU313278A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1971 |

|

SU319938A1 |

| ЦИФРОВОЙ ОБНАРУЖИТЕЛЬ СИГНАЛА С НЕИЗВЕСТНОЙ ЧАСТОТОЙ | 1973 |

|

SU385387A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| ЦИФРОВОЙ ФАЗОВЫЙ ДИСКРИМИНАТОР | 1972 |

|

SU349007A1 |

| Дискриминатор временного положения периодических электрических сигналов | 1983 |

|

SU1099379A2 |

| ЦИФРОВАЯ ДИНАМИЧЕСКАЯ СЛЕДЯЩАЯ СИСТЕМА | 1969 |

|

SU244464A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU924667A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1977 |

|

SU1840975A1 |

| Дискриминатор временного положения периодических электрических сигналов | 1975 |

|

SU600693A1 |

Авторы

Даты

1973-01-01—Публикация