Изобретение относится к радиотехнике и может быть использовано для вьщеления сигнала с изменяющейся во времени частотой.

Цель изобретения - повьшение чув- ствительности.

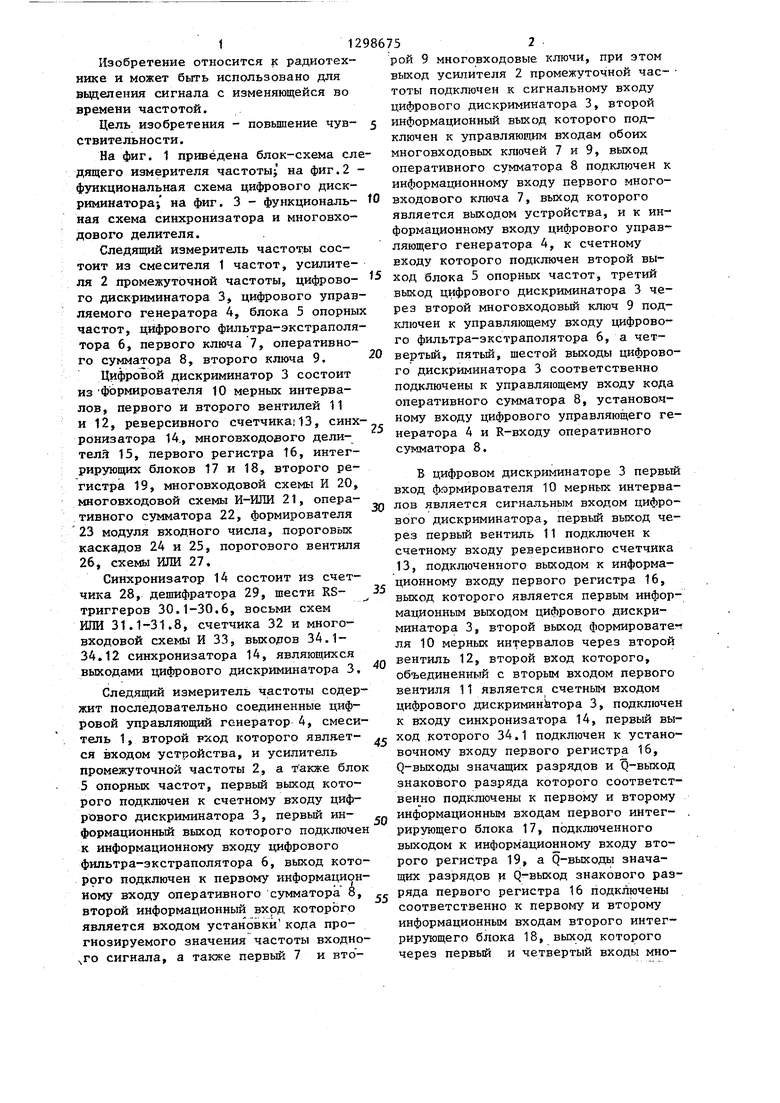

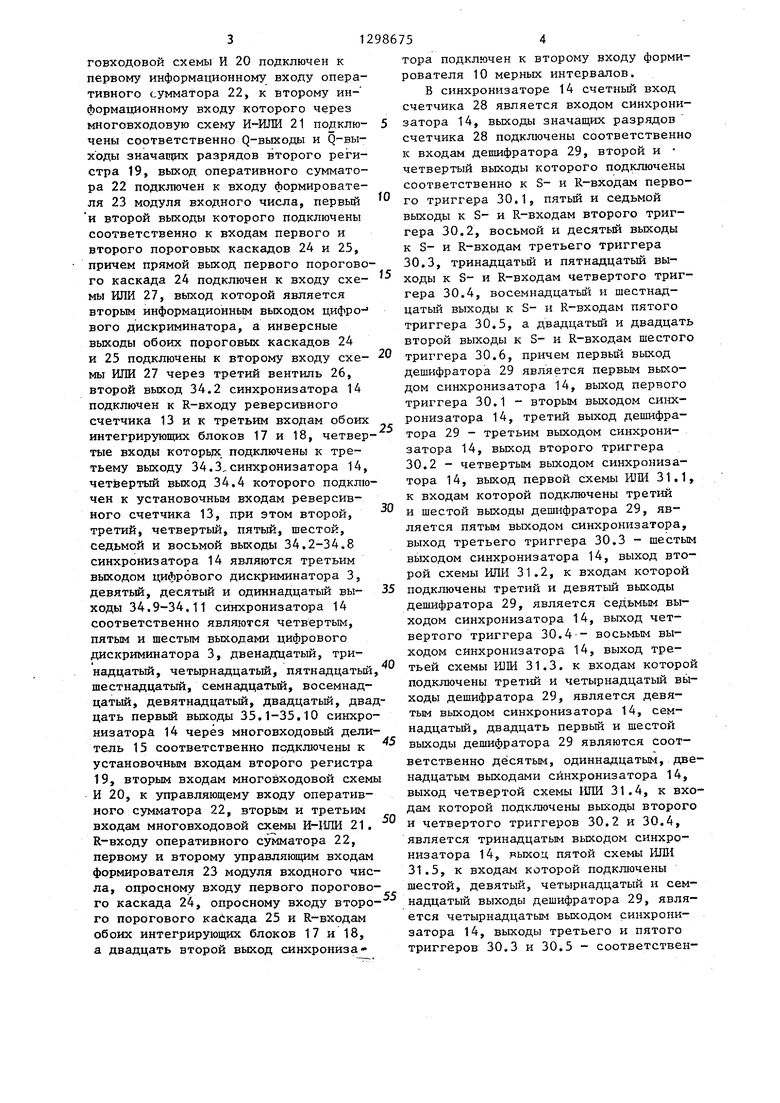

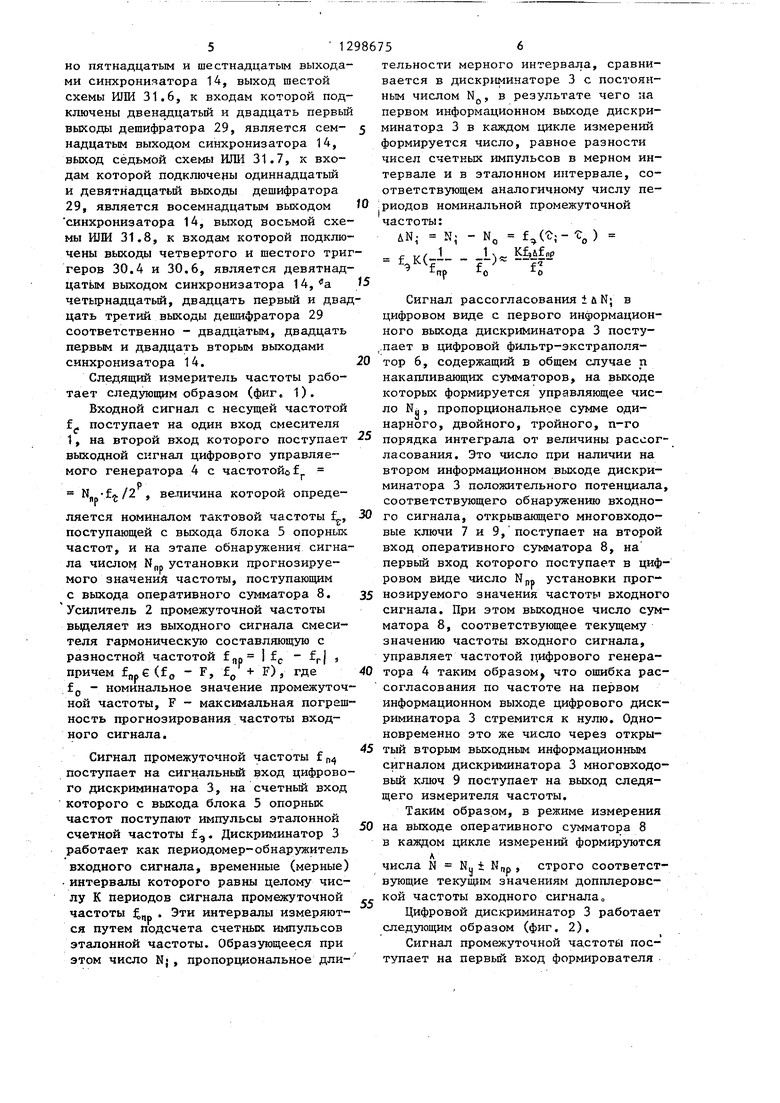

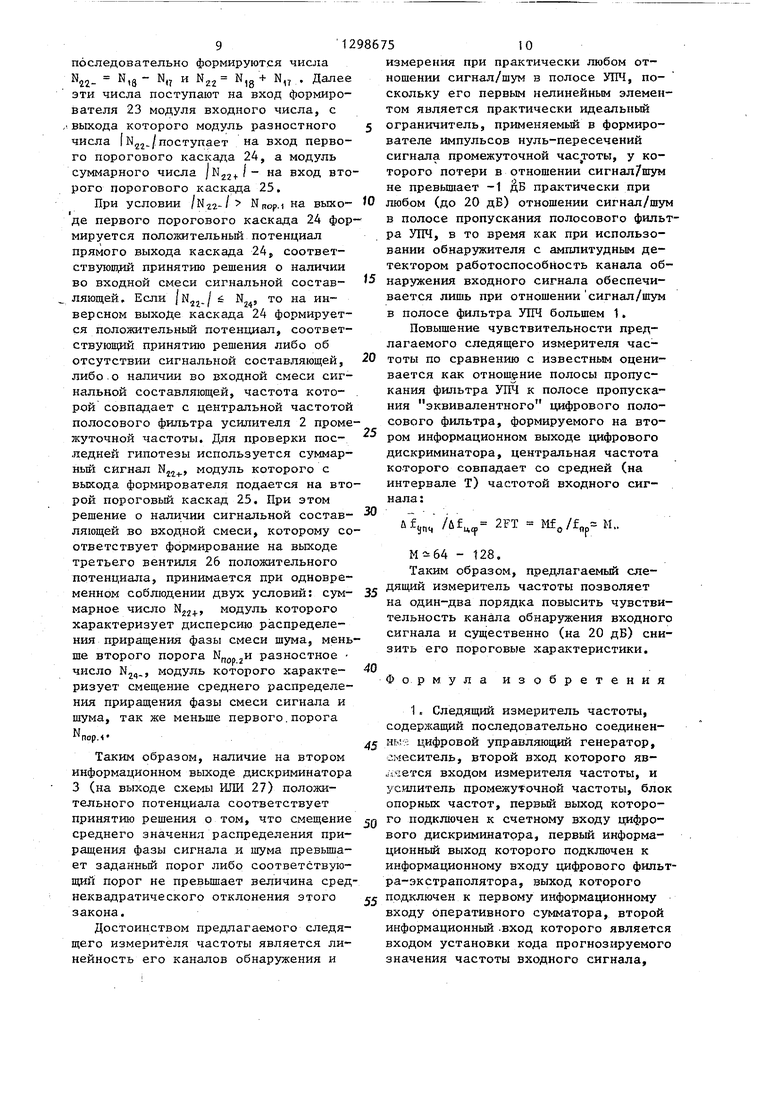

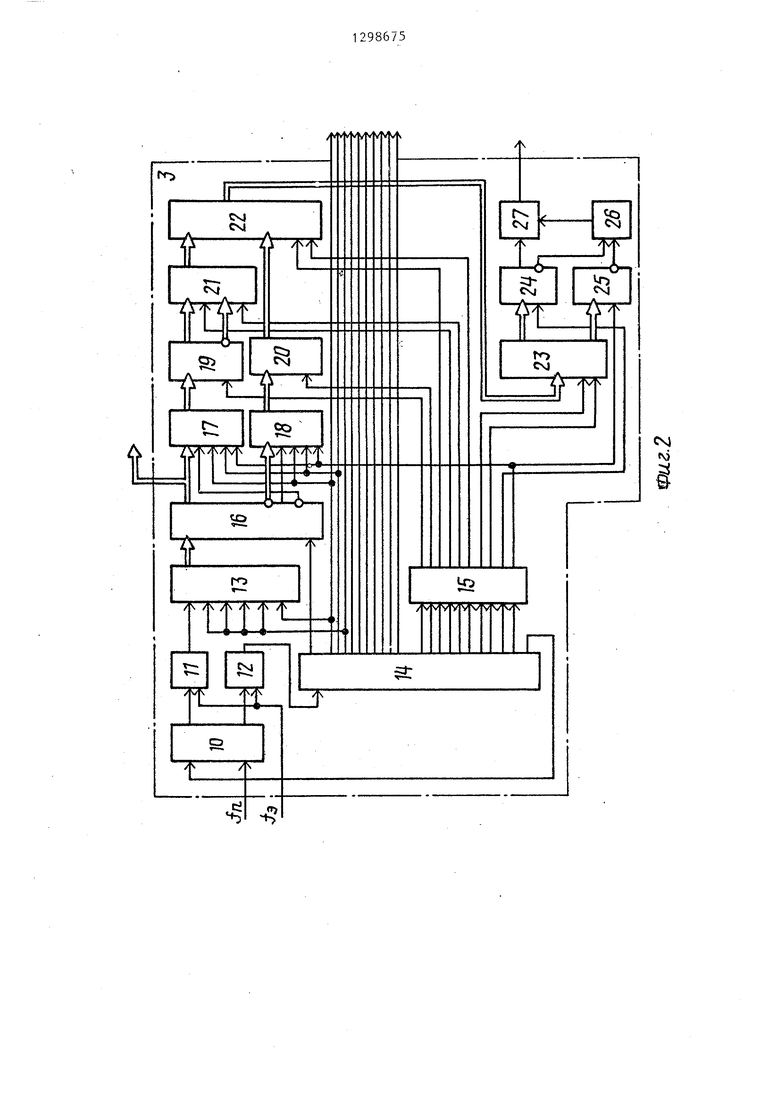

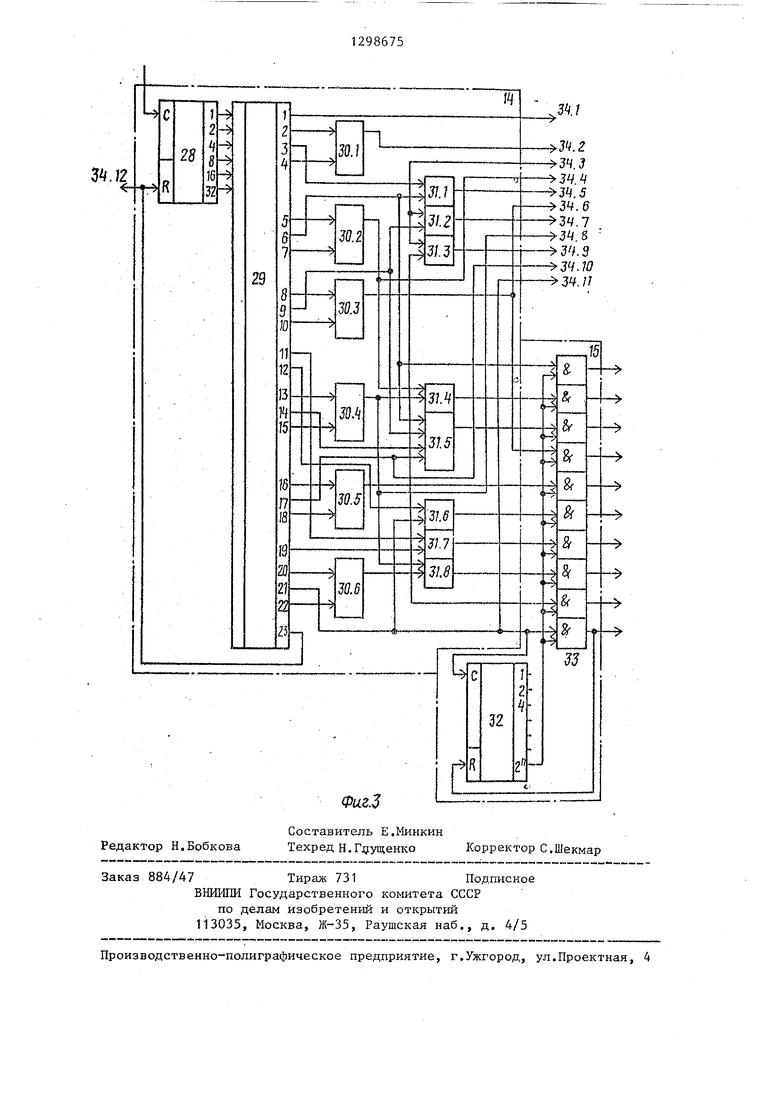

На фиг. 1 приведена блок-схема слдящего измерителя частоты; на фиг.2 функциональная схема цифрового дискриминатора; на. фиг. 3 - функциональ- ная схема синхронизатора и многовхо- дового делителя.

Следящий измеритель частоты состоит из смесителя 1 частот, усилителя 2 промежуточной частоты, цифрово- го дискриминатора 3, цифрового управляемого генератора 4, блока 5 опорны частот, цифрового фильтра-экстраполя тора 6, первого ключа 7, оперативного сумматора 8, второго ключа 9.

Цифровой дискриминатор 3 состоит из формирователя 10 мерных интервалов, первого и второго вентилей 11 и 12, реверсивного счетчика; 13, синхронизатора 14., многовходогого делители 15, первого регистра 16, интегрирующих блоков 17 и 18, второго ре-- гистра 19, многовходовой схемы И 20, многовходовой схемы И-ИЛИ 21, оперативного сзтф1атора 22, формирователя 23 модуля входного числа, пороговых каскадов 24 и 25, порогового вентиля 26, схемы ИЛИ 27.

Синхронизатор 14 состоит из счетчика 28, дешифратора 29, шести RS- триггеров 30.1-30.6, восьми схем ИЛИ 31.1-31.8, счетчика 32 и многовходовой схемы И 33, выходов 34.1- 34.12 синхронизатора 14, являющихся выходами цифрового дискриминатора 3.

Следящий измеритель частоты содержит последовательно соединенные цифровой управляющий генератор 4, смеситель 1, второй вход которого явля.ет- ся входом устройства, и усилитель промежуточной частоты 2, а т акже блок 5 опорных частот, первый выход которого подключен к счетному входу цифрового дискриминатора 3, первый ин- формационный выход которого подключен к информационному входу цифрового фильтра-экстраполятора 6, выход кото- Р9ГО подключен к первому информационному входу оперативного сумматора 8, второй информационньй вход которого является входом установки кода прогнозируемого значения частоты входно- го сигнала, а также первый 7 и вто

0

5

,.

0

рой 9 многовходовые ключи, при этом выход усилителя 2 промежуточной час- тоты подключен к сигнальному входу цифрового дискриминатора 3, второй информационный выход которого подключен к управляющим входам обоих многовходовых кшочей 7 и 9, выход оперативного сумматора 8 подключен к информационному входу первого много- входового ключа 7, выход которого является выходом устройства, и к информационному входу цифрового управляющего генератора 4, к счетному входу которого подключен второй выход блока 5 опорных частот, третий выход цифрового дискриминатора 3 через второй многовходовый ключ 9 подключен к управляющему входу цифрового фильтра-экстраполятора 6, а чет- вертьй, пятый, шестой выходы цифрового дискриминатора 3 соответственно подключены к управляющему входу кода оперативного сумматора 8, установочному входу цифрового управляющего генератора 4 и R-входу оперативного сумматора 8.

Б цифровом дискриминаторе 3 первый вход формирователя 10 мерных интервалов является сигнальным входом цифрового дискриминатора, первый выход через первый вентиль 11 подключен к счетному входу реверсивного счетчика 13, подключенного выходом к информационному входу первого регистра 16, выход которого является первым информационным выходом цифрового дискриминатора 3, второй выход формировате ля 10 мерных интервалов через второй вентиль 12, второй вход которого, объединенный с вторым входом первого вентиля 11 является счетным входом цифрового дискриминатора 3, подключен к входу синхронизатора 14, первый выход которого 34.1 подключен к установочному входу первого регистра 16, Q-выходы значащих разрядов и Q-выход знакового разряда которого соответст- подключены к первому и второму информационным входам первого интег- . рирующего блока 17, подключенного выходом к информационному входу второго регистра 19, а р-вькодь1 значащих разрядов и Q-выход знакового разряда первого регистра 16 подключены соответственно к первому и второму информационным входам второго интег- рирзтощего блока 18, выход которого через первый и четвертый входы многовходовой схемы И 20 подключен к первому информационному входу оперативного сумматора 22, к второму информационному входу которого через многовходовую схему И-ИЛИ 21 подключены соответственно Q-выходы и Q-вы- хЪды значащих разрядов второго регистра 19, выход оперативного сумматора 22 подключен к входу формирователя 23 модуля входного числа, первый и второй выходы которого подключены соответственно к входам первого и второго пороговьк каскадов 24 и 25, причем прямой выход первого порогового каскада 24 подключен к входу схемы ИЛИ 27, выход которой является вторым информационным выходом цифро- вого дискриминатора, а инверсные выходы обоих пороговых каскадов 24 и 25 подключены к второму входу схемы ИЛИ 27 через третий вентиль 26, второй выход 34.2 синхронизатора 14 подключен к R-входу реверсивного счетчика 13 и к третьим входам обоих интегрирующих блоков 17 и 18, четвертые входы которых подключены к третьему выходу 34.3,синхронизатора 14, четвертый выход 34,4 которого подключен к установочным входам реверсивного счетчика 13, при этом второй, третий, четвертый, пятый, шестой, седьмой и восьмой вькоды 34.2-34.8 синхронизатора 14 являются третьим выходом цифрового дискриминатора 3, девятьй, десятый и одиннадцатый выходы 34.9-34,11 синхронизатора 14 соответственно являются четвертым, пятым и шестым выходами цифрового дискриминатора 3, двенадцатый, тринадцатый, четьфнадцатый, пятнадцатый шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый, двадцатый, двадцать первый выходы 35.1-35,10 синхронизатора 14 через многовходовьй делитель 15 соответственно подключены к установочным входам второго регистра 19, вторым входам многовходовой схемы И 20, к управляющему входу оперативного сумматора 22, вторым и третьим входам многовходовой схемы И-1ШИ 21. R-входу оперативного сумматора 22, первому и второму управляющим входам формирователя 23 модуля входного числа, опросному входу первого порогового каскада 24, опросному входу второ го порогового каскада 25 и R-входам обоих интегрирующих блоков 17 и 18, а двадцать второй выход синхрониза

86754

тора подключен к второму входу форми10

15

20

25

30

35

40

45

50

-55

рователя 10 мерных интервалов.

В синхронизаторе 14 счетный вход счетчика 28 является входом синхронизатора 14, выходы значащих разрядов счетчика 28 подключены соответственно к входам дешифратора 29, второй и четвертый выходы которого подключены соответственно к S- и 11-входам первого триггера 30,1, пятьй и седьмой выходы к S- и R-входам второго триггера 30.2, восьмой и десятый выходы к S- и R-входам третьего триггера 30.3, тринадцатый и пятнадцатый выходы к S- и R-входам четвертого триггера 30.4, восемнадцатью и шестнадцатый выходы к S- и R-входам пятого триггера 30.5, а двадцатый и двадцать второй выходы к S- и R-входам шестого триггера 30.6, причем первый выход дешифратора 29 является первым выходом синхронизатора 14, выход первого триггера 30.1 - вторым выходом синхронизатора 14, третий выход дешифратора 29 - третьим выходом синхронизатора 14, выход второго триггера 30.2 - четвертым выходом синхронизатора 14, выход первой схемы И11И 31.1, к входам которой подключены третий и шестой выходы дешифратора 29, является пятым выходом синхронизатора, выход третьего триггера 30.3 - шестым выходом синхронизатора 14, выход второй схемы ИЛИ 31.2, к входам которой подключены третий и девятый выходы дешифратора 29, является седьмым выходом синхронизатора 14, выход четвертого триггера 30.4- восьмым выходом синхронизатора 14, выход третьей схемы И1Ш 31.3. к входам которой подключены третий и четырнадцатый выходы дешифратора 29, является девятым выходом синхронизатора 14, сем- надцатьй, двадцать первый и шестой выходы дешифратора 29 являются соответственно десятым, одиннадцатым, двенадцатым выходами синхронизатора 14, выход четвертой схемы 1ШИ 31.4, к входам которой подключены выходы второго и четвертого триггеров 30,2 и 30.4, является тринадцатым выходом синхронизатора 14, выход пятой схемы ИЛИ 31,5, к входам которой подключены шестой, девятый, четырнадцатый и семнадцатый выходы дешифратора 29, является четырнадцатым выходом синхронизатора 14, выходы третьего и пятого триггеров 30.3 и 30.5 - соответственно пятнадцатым и шестнадцатым выходами синхронизатора 14, выход шестой схемы ИЛИ 31.6, к входам которой подключены двенадцатьш и двадцать первый

вькоды дешифратора 29, является сем- 5 минаторз 3 в каждом цикле измерений надцатым выходом синхронизатора 14, выход седьмой схемы ИЛИ 31.7, к входам которой подключены одиннадцатый и девятнадцатый выходы дешифратора 29, является восемнадцатым выходом синхронизатора 14, выход восьмой схемы ИЛИ 31.8, к входам которой подключены выходы четвертого и шестого триггеров 30.4 и 30.6, является девятнад- цатьм выходом синхронизатора 14,а 5 четьфнадцатый, двадцать первый и двадцать третий выходы дешифратора 29 соответственно - двадцатым, двадцать первым и двадцать вторым выходами синхронизатора 14.

Следящий измеритель частоты работает следующим образом (фиг, 1).

Входной сигнал с несущей частотой f поступает на один вход смесителя

формируется число, равное разности чисел счетных импульсов в мерном интервале и в этсшонном интервале, соответствующем аналогичному числу пе- 10 триодов номинальной промежуточной частоты:

&N. N- - N, f(;- t)

- f Vf 1 Kfjufnp

- s f f

0

Сигнал рассогласования 1 u Nj в цифровом виде с первого информационного выхода дискриминатора 3 посту- ,.пает в цифровой фильтр-экстраполя- 20 тор 6, содержащий в общем случае п накапливающих сумматоров, на выходе которых формируется управляющее число Nq, пропорциональное сумме одинарного, двойного, тройного, п-го

1, на второй вход которого поступает 5 порядка интеграла от величины рассог- выходной сигнал цифрового управляе- ласования. Это число при наличии на мого генератора 4 с частотойй втором информационном выходе дискри-

„ ,. ,„Р„минатора 3 положительного потенциала,

- , величина которой опреде-.- .

Р соответствующего обнаружению входно-

ляется номиналом тактовой частоты f, 30 го сигнала, открьшающего многовходо- поступающей с выхода блока 5 опорных вые ключи 7 и 9, поступает на второй частот, и на этапе обнаружения сигна- вход оперативного сумматора 8, на

первый вход которого поступает в цифровом виде число Npp установки прог- 35 нозируемого значения частоты входного сигнала. При этом выходное число сумматора 8, соответствующее текущему значению частоты входного сигнала, управляет частотой ттифрового генера- 40 тора 4 таким образом, что ошибка рассогласования по частоте на первом ной частоты, F - максимальная погреш- информационном выходе цифрового диск- ность прогнозирования частоты вход- риминатора 3 стремится к нулю. Одноного сигнала.новременно это же число через откры-

45 тый вторым выходным информационным сигналом дискриминатора 3 многовходо- вый ключ 9 поступает на выход следящего измерителя частоты.

Таким образом, в режиме измерения 50 на выходе оперативного сумматора 8 в каждом цикле измерений формируются

л

числа N NU i , строго соответствующие текущим значениям допплеровс- кой частоты входного сигнала

Цифровой дискриминатор 3 работает следующим образом (фиг. 2).

Сигнал пром гжуточной частоты пос- тупает на первьй вход формирователя

ла числом N„0 установки прогнозируемого значения частоты, поступающим с выхода оперативного сумматора 8. Усилитель 2 промежуточной частоты вьщеляет из выходного сигнаша смесителя гармоническую составляющую с разностной частотой fnp i fс причем fnpe(fo - F, fj, + F), где fP - номинальное значение промежуточСигнал промежуточной частоты f„ поступает на сигнальный вход цифрового дискриминатора 3, на счетный вход которого с выхода блока 5 опорных частот поступают импульсы эталонной счетной частоты f. Дискриминатор 3 работает как периодомер-обнаружитель входного сигнала, временные (мерные) интервалы которого равны целому числу К периодов сигнала промежуточной частоты „ . Эти интервалы измеряют55

ся путем подсчета счетных импульсов эталонной частоты. Образующееся при этом число NJ, пропорциональное длительности мерного интервала, сравнивается в дискриминаторе 3 с постоянным числом Ng, в результате чего на первом информационном выходе дискриминаторз 3 в каждом цикле измерений

формируется число, равное разности чисел счетных импульсов в мерном интервале и в этсшонном интервале, соответствующем аналогичному числу пе- триодов номинальной промежуточной частоты:

&N. N- - N, f(;- t)

- f Vf 1 Kfjufnp

- s f f

0

10 мерных интервалов, первый выход которого в начале мерного интервала цикла закрьшает первый вентиль 11, а второй выход открывает второй вентиль 12, через который счетные им- пульсы блока 5 опорных частот поступают на вход синхронизатора 14, на выходе которого форм1фуются 22 сигнала, управляющих работой устройства в целом. Первый управляющий сигнал переписывает оставшиеся в реверсивном счетчике 13 от предыдущего цикла измерений числа±uN; в регистр 16, второй сигнал обнуляет реверсивный счетчик 13, а четвертый, поступающий на соответствующие разряды этого счетчика, записывает в него в обрат- ном коде число

-N - - Р

о „

где Е - число эталонных импульсов

счетной частоты, используемых в синхронизаторе 14 для формирования последнего (22-го) управляющего сигнала который поступает на второй вход формирователя 10 и переключает его выходы таким образом, что первый выход от- крьшает вентиль 11, а второй выход закрьшает вентиль 12.

При этом счетные импульсы поступают на счетйый вход реверсивного счетчика 13, на выходе которого в i-M цикле измерений формируется число

.Kf

Kf;

luN; (ф- - О -.(-Р - 0

Kf а А f up

-пр

которое в начале следующего (i+1)-ro цикла измерений первым управляющим сигналом импульсом переписьшается в регистр 16, откуда это число в режиме 45 слежения с помощью управляющих сигналов переписывается в цифровой фильтр- экстраполятор 6.

Одновременно с процессом измерения частоты рассогласования цифровой диск-50 риминатор 3 обеспечивает периодическое (с периодом Т Ж 1/fnp) обнаружение входного сигнала, принимаемого на фоне шумов, обуславливающих нормальное (гаусовское) или лапласовс- кое распределение фазовых флуктуации смеси сигнала и шума, либо только шума. С этой целью производится раздельное накопление на интервале обнаружения Т положительных и отрицательных чисел с выхода регистра 16, соответствующих отрицательным или положительным выборкам рассогласования частоты входного сигнала относительно опорной на i-M интервале измерений. При этом в зависимости от вида закона распределения фазовых флуктуации сигнала и шума используются соответствующие интегрирующие блоки 17 и 18.

В случае воздействия нормальных фазовых флуктуации сигнала и шума интегрирующий блок 17 (18) реализует линейньм алгоритм накопления выборок

т

ZuN;-; N.

l

m

- Л N;);

20

т.

+ т ,

, т.- соответственно числа положительных N и отрицательных -AN; отсчетов выборок разности приращений фазы входного сигнала на интервале Т, М - суммарное число положительных и отрицательных выборок ±N;.

случае воздействия смеси сигнашума с Лапласовским распределефазовых флуктуации интегрирующий 17 (18) реализует знаковый алгонакопления выборок

rr.

m,

r

21 и Г-UK,- m

и u N;

1, при N О

о, при . Накопление за интервал Т числа

(3)

N

, из интегрирующего блока 17 с помощью управляющих сигналов 34.1, формируемых на выходе многовходового делителя 15, переписываются во второй регистр 19, на выходе которого образуются положительное и отрицательное значения этих чисел, которые в соответствующих циклах обработки поступают через многовходовую схему И-ИЛИ 21 на первый вход оперативного сумматора 22, на другой вход которого соответственно через многовходовую схему И 20 из накапливающего сумматора 18 поступают числа N,g.

В результате на выходе оперативного сумматора 22 каждые Т секунд

последовательно формируются числа 8 п и 22 N,g+ N,7 , Далее эти числа поступают на вход формирователя 23 модуля входного числа, с , выхода которого модуль разностного числа NgjJ поступает на вход первого порогового каскада 24, а модуль суммарного числа |N,j2t/- на вход второго порогового каскада 25,

При условии .) на выходе первого порогового каска,а;а 24 формируется положительньй потенциал прямого выхода каскада 24, соответствующий принятию решения о наличии во входной смеси сигнальной состав- ляющей. Если /N./ N, то на ин20

, 25

версном выходе каскада 24 формируется положительный потенциал, соответствующий принятию решения либо об отсутствии сигнальной составляющей, либо.о наличии во входной смеси сигнальной составляющей, частота которой совпадает с центральной частотой полосового фильтра усилителя 2 промежуточной частоты. Для проверки пос ледней гипотезы используется суммарный сигнал Njj, модуль которого с выхода формирователя подается на второй пороговьй каскад 25. При этом решение о наличии сигнальной состав- ляющей во входной смеси, которому соответствует формирование на выходе третьего вентиля 26 положительного

потенциала, принимается при одновре,-- -зе дящии измеритель частоты позволяет

менном соблюдении двух условии: сум- 35

измерения при практически любом отношении сигнал/шум в полосе УПЧ, по скольку его первым нелинейным элеме том является практически идеальньш

5 ограничитель, применяемый в формиро вателе импульсов нуль-пересечений сигнала промежуточной , у к торого потери в отношении сигнал/шу не превьш ает -1 дБ практически при

О любом (до 20 дБ) отношении сигнал/ш в полосе пропускания полосового фил ра УПЧ, в то время как при использо вании обнаружителя с амплитудным д тектором работоспособность канала

5 наружения входного сигнала обеспечи вается лишь при отношении сигнал/шу в полосе фильтра УПЧ большем 1.

Повышение чувствительности пред лагаемого следящего измерителя час тоты по сравнению с известным оцен вается как отношение полосы пропус кания фильтра УПЧ к полосе пропуск ния эквивалентного цифрового пол сового фильтра, формируемого на вт ром информационном выходе цифровог дискриминатора, центральная частот которого совпадает со средней (на интервале Т) частотой входного сиг нала:

й,пч /ufucp

2FT ..

- 128.

Таким образом, предлагаемый слена один-два порядка повысить чувств тельность канала обнаружения входн сигнала и существенно (на 20 дБ) с зить его пороговые характеристики.

марное число N224., модуль которого характеризует дисперсию распределения приращения фазы смеси шума, меньше второго порога Nf,., и разностное число NJ,., модуль которого характеризует смещение среднего распределения приращения фазы смеси сигнала и шума, так же меньше первого.порога

пормТаким образом, наличие на втором информационном выходе дискриминатора 3 (на выходе схемы ИЛИ 27) положительного потенциала соответствует принятию решения о том, что смещение среднего значения распределения приращения фазы сигнала и шума превьш1а- ет заданный порог либо соответствующий порог не превьш1ает величина сред- неквадратического отклонения этого закона.

Достоинством предлагаемого следящего измерителя частоты является линейность его каналов обнаружения и

измерения при практически любом отношении сигнал/шум в полосе УПЧ, поскольку его первым нелинейным элементом является практически идеальньш

ограничитель, применяемый в формирователе импульсов нуль-пересечений сигнала промежуточной , у которого потери в отношении сигнал/шум не превьш ает -1 дБ практически при

любом (до 20 дБ) отношении сигнал/шум в полосе пропускания полосового фильтра УПЧ, в то время как при использовании обнаружителя с амплитудным детектором работоспособность канала обнаружения входного сигнала обеспечивается лишь при отношении сигнал/шум в полосе фильтра УПЧ большем 1.

Повышение чувствительности предлагаемого следящего измерителя частоты по сравнению с известным оценивается как отношение полосы пропускания фильтра УПЧ к полосе пропускания эквивалентного цифрового полосового фильтра, формируемого на втором информационном выходе цифрового дискриминатора, центральная частота которого совпадает со средней (на интервале Т) частотой входного сигнала:

й,пч /ufucp

2FT ..

- 128.

Таким образом, предлагаемый сле35

40

на один-два порядка повысить чувствительность канала обнаружения входного сигнала и существенно (на 20 дБ) снизить его пороговые характеристики.

Формула изобретения

45

50

1. Следящий измеритель частоты, содержащий последовательно соединенны:; цифровой управляющий генератор, смеситель, второй вход которого яв- ...-.яется входом измерителя частоты, и усилитель промежуючной частоты, блок опорных частот, первый выход которого подключен к счетному входу цифрового дискриминатора, первый информационный выход которого подключен к информационному входу цифрового фнльт- ра-экстраполятора, выход которого j подключен к первому информационному входу оперативного сумматора, второй информационный .вход которого является входом установки кода прогнозируемого значения частоты входного сигнала.

а также первый и второй многовходовые ключи, о- тличающийся тем, что, с целью повышения чувствительности, выход усилителя промежуточной частоты подключен к сигнальному входу цифрового дискриминатора, второй информационный выход которого подключен к управляющим входам многовходовых ключей, выход оперативного сумматора

первому и второму информационным входам первого интегрирующего блока,подключенного выходом к информационному входу второго регистра, а Q-выходы значащих разрядов и Q-выход знакового разряда первого регистра подключены соответственно к первому и втором информационным входам второго интегрирующего блока, выход которого чеподключен к информационному входу пер- О рез первый и четвертый многовходовые

вого многовходового ключа, выход которого является выходом измерителя частоты, и к информационному входу цифрового управляющего генератора, к счетному входу которого подключен второй выход блока опорньк частот, третий выход цифрового дискриминатора через второй многовходовый ключ подключен к управляющему входу цифрового фильтра-зкстраполятора, а чет- вертьщ, пятый и шестой выходы цифрового дискриминатора соответственно подключены к управляющему входу оперативного сумматора, установочному входу цифрового управляющего генерат тора и к R-входу оперативного сумматора .

2, Измеритель по п. 1, о т л и- чающийся тем, что цифровой дискриминатор содержит формирователь мерных интервалов, три вентиля, реверсивный счетчик, два регистра, два интегрирующих блока, многовходовую схему И, многовходовую схему И-ИЛИ, оперативный сумматор, блок формиро- вания модуля входного числа, два пороговых каскада, схему ИЛИ, синхронизатор, и многовходовый делитель, причем первый вход формирователя мерных интер лов является сигнальным входом цифрового дискриминатора, первьй выход через первый вентиль подключен к счетному входу реверсивного счетчика, подключенного вьтходом к инфорна- ционному входу первого регистра, выход которого является первым информационным выходом цифрового дискриминатора, второй выход формирователя

мерных интервалов через второй вен

тиль, второй вход которого объединен- ньй с вторым входом первого вентиля является счетным входом цифрового дискриминатора, подключен к входу синхронизатора, первый выход которого подключен к установочному входу пер- .вого регистра, Q- выходы значащих разрядов и Q-выход знакового разряда которого соответственно подключены к

первому и второму информационным входам первого интегрирующего блока,подключенного выходом к информационному входу второго регистра, а Q-выходы значащих разрядов и Q-выход знакового разряда первого регистра подключены соответственно к первому и второму информационным входам второго интегрирующего блока, выход которого через первый и четвертый многовходовые

5

5

0

Q j

0

5

0

гс

схемы И подключен к первому информационному входу оперативного сумматора, к второму информационному входу которого через многовходовую схему И-ИЛИ подключены соответственно Q- выходы и Q-выходы значащих разрядов второго регистра, выход оперативного сумматора подключен к входу формирователя модуля входного числа, первый и второй выходы которого подключены соответственно к входам первого и второго пороговых каскадов причем прямой выход первого порогового каскада подключен к входу схемы ШШ, выход которой является вторым информационным выходом цифрового дискриминатора, а инверсные выходы обоих пороговых каскадов подключены к второму входу схемы ИЛИ через третий вентиль, второй выход синхр онизатора подключен к R-вХоду реверсивного счетчика, и к третьим входам обоих интегрир тоцщх блоков, четвертые входы которых подключены к третьему выходу синхронизатора, четвертый выход которого подключен к установочным входам реверсивного счетчика, при этом второй, третий, четвер тый, пятый, шестой, седьмой, восьмой выходы синхронизатора являются третьим выходом цифрового дискриминатора, девятый, десятый и одиннадцатый выходы синхронизатора соответственно являются четвертьм, пятым и шестым выходами цифрового дискриминатора, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый, двадцатый и двадцать первый выходы синхронизатора через многовходовый делитель соответственно подключены к установочным входам второго регистра , вторым входам многовходовой схемы И, к установочному входу оперативного сумматора, вторым и третьим входам многовходовой схемы И-ИЛИ, R-входу оперативного сумматора, первому и второму управляющим входам формирователя модуля входного

числа, опросному входу первого порогового каскада и опросному входу второго порогового каскада и R-входам обоих интегрирующих блоков, а двадцать второй выход синхронизатора подключен 5 к второму входу формирователя мерных интервалов«

3. Измеритель по п. 2, отличающийся тем, что синхрониза тор содержит счетчик, дешифратор, шесть RS -триггеров и восемь схем ИЛИ, причем счетный вход счетчика является входом синхронизатора, выходы значащих разрядов счетчика подключены со- ответственно к входам дешифратора, второй и четвертый выходы которого подключены соответственно к S- и R- входам первого триггера, пятый и седьмой выходы к S- и R-входам второ10

}5

торой подключены третий и девятьм выходы дешифратора, является седьмым выходом синхронизатора, выход четвертого триггера - восьмым выходом синхронизатора, выход третьей схемы ИЛИ, к входам которой подключены третий и четырнадцатью выходы дешифратора,/ является девятым выходом синхронизатора семнадцатый, дваДцать первый и шестой выходы дешифратора являются соответственно десятым, одиннадцатым и двенадцатым выходами синхронизатора, выход четвертой схемы ШШ, к входам которой подключены выходы второго и чет вертого триггеров, является тринадцатым выходом синхронизатора, выход пятой схемы ИЛИ, к входам которой подг-.к ключены шестой, девятый, четырнадцатый и семнадцатьй выходы дешифратора.

го триггера, восьмой и десятый выходы20 является четырнадцатым выходом синх25

к S-.й R-выходам третьего триггера, тринадцатый и пятнадцатый выходы к S- и R-входам четвертого триггера, шестнадцатый и восемнадцатый выходы - к S- и R-входам пятого триггера, а двадцатый и двадцать второй выходы - к S- и R-входам шестого триггера, причем первый выход дешифратора является первым выходом синхронизатора, выход первого триггера - вторым вы- -30 ходом синхронизатора, третей выход дешифратора - третьим выходом синхронизатора, выход второго триггера - четвертым выходом синхронизатора, выход первой схемы ИЛИ, к входам которой 35 подключены третий и шестой выходы дешифратора, является пятым выходом синхронизатора, выход третьего триггера - шестым выходом синхронизатора.

ронизатора, выходы третье триггеров соответственно и шестнадцатым выходами с ра, выход шестой схемы Ш которой подключены двенад двадцать первый выходы де является семнадцатым выхо низатора, выход седьмой с к входам которой подключе цатьш и девятнадцатый вых тора, является восемнадца синхронизатора, выход вос ИЛИ, к входам которой под ходы четвертого и шестого является девятнадцатым вь ронизатора, а четырнадцат первый и двадцать третий шифратора соответственно двадцать первым и двадцат

выход второй схемы ШШ, к входам ко- выходами синхронизатора.

торой подключены третий и девятьм выходы дешифратора, является седьмым выходом синхронизатора, выход четвертого триггера - восьмым выходом синхронизатора, выход третьей схемы ИЛИ, к входам которой подключены третий и четырнадцатью выходы дешифратора,/ является девятым выходом синхронизатора, семнадцатый, дваДцать первый и шестой выходы дешифратора являются соответственно десятым, одиннадцатым и двенадцатым выходами синхронизатора, выход четвертой схемы ШШ, к входам которой подключены выходы второго и четвертого триггеров, является тринадцатым выходом синхронизатора, выход пятой схемы ИЛИ, к входам которой подг-.к ключены шестой, девятый, четырнадцатый и семнадцатьй выходы дешифратора.

ронизатора, выходы третьего и пятого триггеров соответственно пятнадцатым и шестнадцатым выходами синхронизатора, выход шестой схемы ШШ, к входам которой подключены двенадцатый и двадцать первый выходы дешифратора, является семнадцатым выходом синхронизатора, выход седьмой схемы ИЛИ, к входам которой подключены одиннад- цатьш и девятнадцатый вых.оды дешифратора, является восемнадцатым выходом синхронизатора, выход восьмой схемы ИЛИ, к входам которой подключены выходы четвертого и шестого триггеров, является девятнадцатым вькодом синхронизатора, а четырнадцатый, двадцать первый и двадцать третий выходы дешифратора соответственно - двадцатым, двадцать первым и двадцать вторым

C4J f4)

Редактор Н.Бобкова

Фиг.З

Составитель Е.Минкин Техред Н.Г ущенко

Заказ 884/47Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая динамическая следящая система | 1986 |

|

SU1368857A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| Цифровой фазовый дискриминатор | 1986 |

|

SU1354387A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Цифровой фазовый дискриминатор | 1986 |

|

SU1343542A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368856A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

Изобретение относится к радиотехнике и может быть использовано для вьщеления сигнала с изменяющейся во времени частотой. Цель изобретения - повышение чувствительности. Устройство содержит цифровой управляемый генератор 4, смеситель 1 частот, усилитель 2 промежуточной частоты. блок 5 опорных частот, цифровой дискриминатор 3, цифровой фильтр-экстра- полятор 6,. оперативный сумматор 8, многовходовые ключи-7 и 9. Для достижения поставленной цели образованы новые функциональные связи. Достон- ством предлагаемого следящего измерителя частоты является линейность его каналов обнаружения и измерения при практически любом отношении сигнал/шум в полосе УПЧ. Устройство позволяет на один-два порядка повысить чувствительность канала обнаружения входного сигнала и существенно (на 20 дБ) снизить его пороговые характеристики. 2 3.п. ф-лы, 3 ил. fPus.1 (Л сг ю со оо CJ5 -J СП

| Следящий измеритель частоты | 1978 |

|

SU766024A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-08-26—Подача