Цифровая динамическая следящай система относится к следящим системам управления и фильтрации, в частности, к следящим фильтрам автоматической подстройки частоты, применяемым для выделения и измерения параметров сигнала, принимаемого на фоне помех.

Известные цифровые следящие системы, содержащие смеситель, дискриминатор и преобразователь код/частота, имеют невысокую точность слежения.

Предлагаемое устройство отличается от известных тем, что в нем параллельно с выходом цифрового дискриминатора дополнительно включено т последовательно соединенных между собой реверсивных счетчиков, выход которых подключен «о входу -преобразователя код/частота.

Это дает возможность повысить точность слежения и измерения параметра отслеживаемого сигнала.

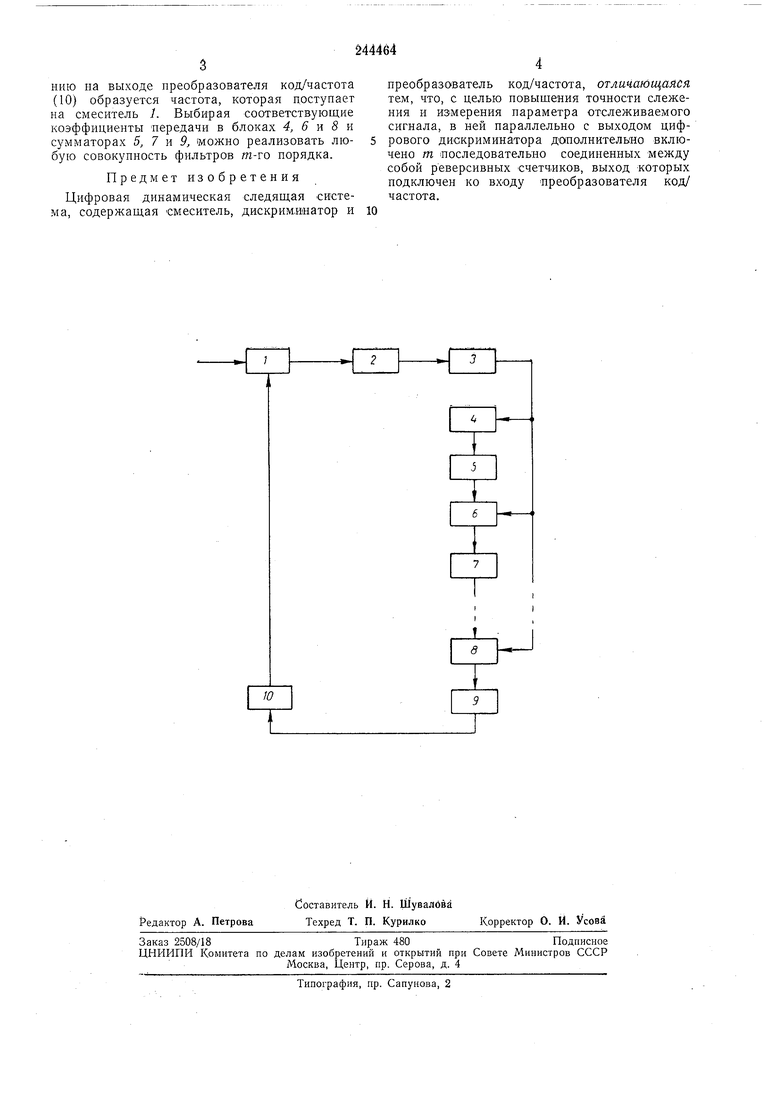

Блок-схема цифровой динамической следящей системы -приведена на чертеже, где обозначено: 1 - смеситель, 2 - усилитель про.мел уточной частоты, 3 - цифровой дискриминатор, 4 - блок коэффициента передачи rn-YQ порядка (т - порядок астатизма следящей системы), 5 - сумматор «т (2) (реверсивный счетчик), 6 - бл-ок коэффициента передачи (т-1)-го порядка, 7 - сумматор «т-1 (Sm-i) (реверсивный счегчик),

В - блок коэффициента передачи первого порядка, 9 - сумматор «1 (Si) (реверсивный счетчик), 10 - преобразователь код/частота. Напряжение промежуточной частоты с выхода узкополосного усилителя 2 промел уточной частоты, обеспечивающего необходимое отношение сигнал/шум, поступает на вход цифрового (частотного или фазового) дискриминатора, где выделяется величина рассогласования ДЛ в цифровой форме. Все время обработки элементарной величины рассогласования АЛ/г занимает В системе с астатизмом ш-го порядка т временных циклов. Во время первого цикла величина записывается с соответствующими .коэффициентами передачи в сумматоры 2, Еа, ... , 2„, которые используются в качестве интеграторов. Во время второго цикла число из сумматора 2 (5) со свои1М знаком записы-вается в

(7), где суммируется с имеющимся там числом. Во щремя третьего цикла получившееся по окончании предыдущего цикла в сумматоре Em-i число записывается в сумматор 2от-2, где суммируется с имеющимся там числом и т. д.

Таким образом, после око-нчания /п-го цикла в сумматоре Si (9) образуется результирующее число, пропорциональное сумме одинарного, двойного, тройного и т. д. в-плоть до

нию на выходе преобразователя код/частота (10) образуется частота, которая поступает на смеситель 1. Выбирая соответствующие коэффициенты передачи в блоках 4, 6 }i 8 vi сумматорах 5, 7 и 9, 1можно реализовать любую совокупность фильтров т-го порядка.

Предмет изобретения

Цифровая динамическая следящая система, содержащая смеситель, дискриминатор и

преобразователь код/частота, отличающаяся тем, что, с целью повыщеяия точности слежения и измерения параметра отслеживаемого сигнала, в ней параллельно с выходом цифрового дискриминатора доиолнительно включено т последовательно соединенных между собой реверсивных счетчиков, выход которых подключен ко входу преобразователя код/ частота.

| название | год | авторы | номер документа |

|---|---|---|---|

| А. Д. ПОДЛИННОЕ и Е. С. Заводий, ^^-о:з^;/пя !->& плтгип'з-^; ГН;^;:;;!^---"- 1 Б:;5л;а;:- | 1972 |

|

SU328430A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU924667A2 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU720452A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1248068A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU734774A1 |

| Следящий измеритель частоты | 1978 |

|

SU766024A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368856A1 |

| Цифровая динамическая следящая система | 1986 |

|

SU1368857A1 |

| СПОСОБ ФОРМИРОВАНИЯ УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ | 1973 |

|

SU392459A1 |

| ЦИФРОВОЙ ВРЕМЕННОЙ ДИСКРИМИНАТОР | 2011 |

|

RU2445728C1 |

Даты

1969-01-01—Публикация