1

Изобретение относится к области запоминающих устройств и предназначено для исправления ошибок при итеративном кодировании.

Известно устройство для исправления ошибок при итеративном кодировании, содержащее блок хранения информации, блок исправления ошибок для кода, записанного по строкам, который подключен к входам сумматора но модулю два всех строк кода и перемножителя, к другому входу которого подсоединен выход сигнала вектора ошибок блока исправления ошибок. Выход перемножителя связан через блок сравнения с блоком номеров, разрешающих запись номера строки из блока управления. Выход импульсов каждой комбинации блока исправления ошибок соединен с входом полусумматора, другой вход которого через ключ, подключенный к выходу блока номеров, связан с выходом сумматора.

Однако такие устройства имеют сложную схему.

Известны также устройства обнаружения ошибок в блоке памяти по строкам, выполненные в виде сумматоров по модулю два и устройства обнаружения ошибок по столбцам, представляющие собой регистр, счетные входы которого подключены к выходам блока памяти. Эти устройства просты, но не позволяют исправлять ошибки в блоке памяти.

Цель изобретення - упрощение устройства для исправления ошибок ири итеративном кодировании.

Это достигается тем, что выходы блока хранения информации соединены с соответствующими входами сумматора по модулю два, регистра со счетными входами и с первыми входами схем «отрицание равнозначности. Выходы регистра со счетными входами связаны с первыми входами ключей переписи информации этого регистра, вторые входы которых соединены с выходом дешифратора блока хранения информации. Выходы этих ключей подключены к регистру запоминания ошибок, выходы которого соединены с первыми входами ключей переписи информации регистра запоминания ошибок. Вторые входы ключей связаны с выходом сумматора по модулю два, а их выходы - с вторыми входами схем «отрицание равнозначности.

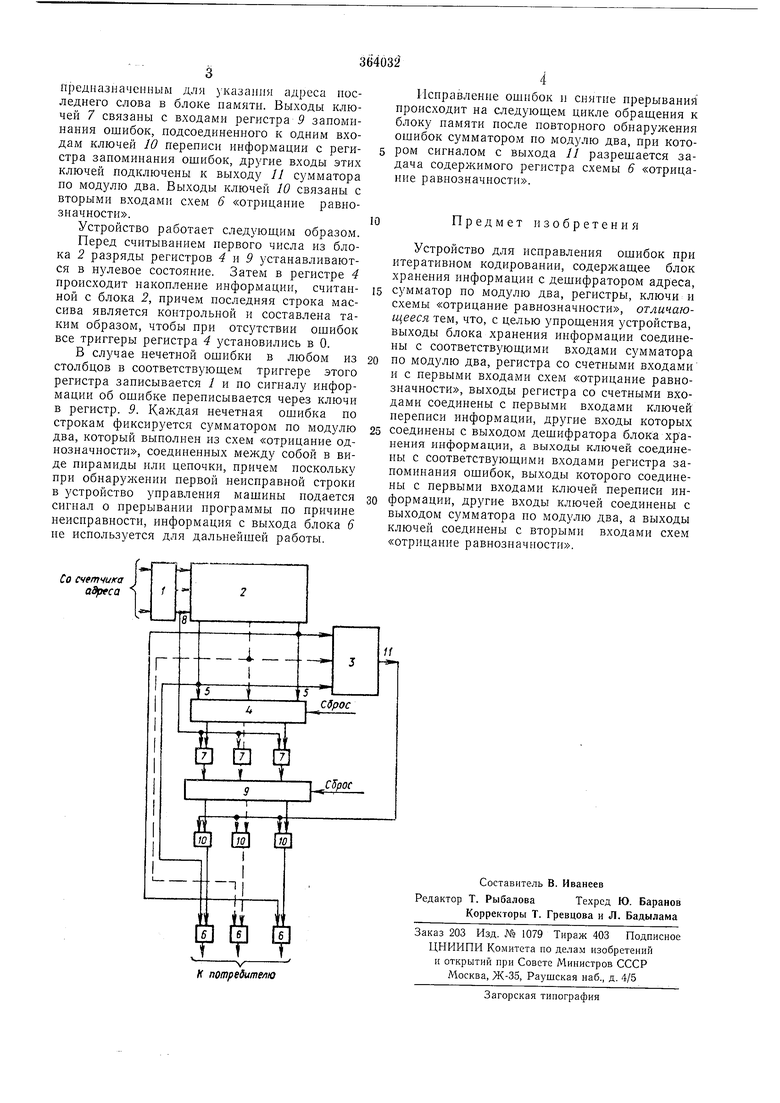

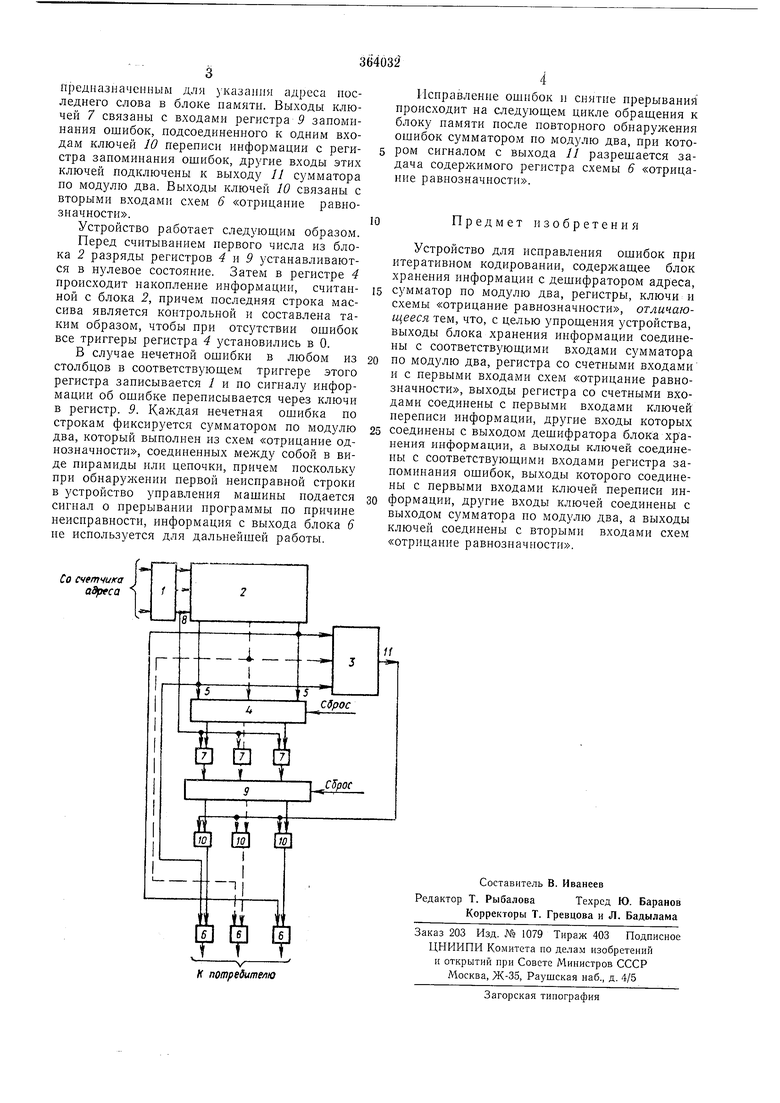

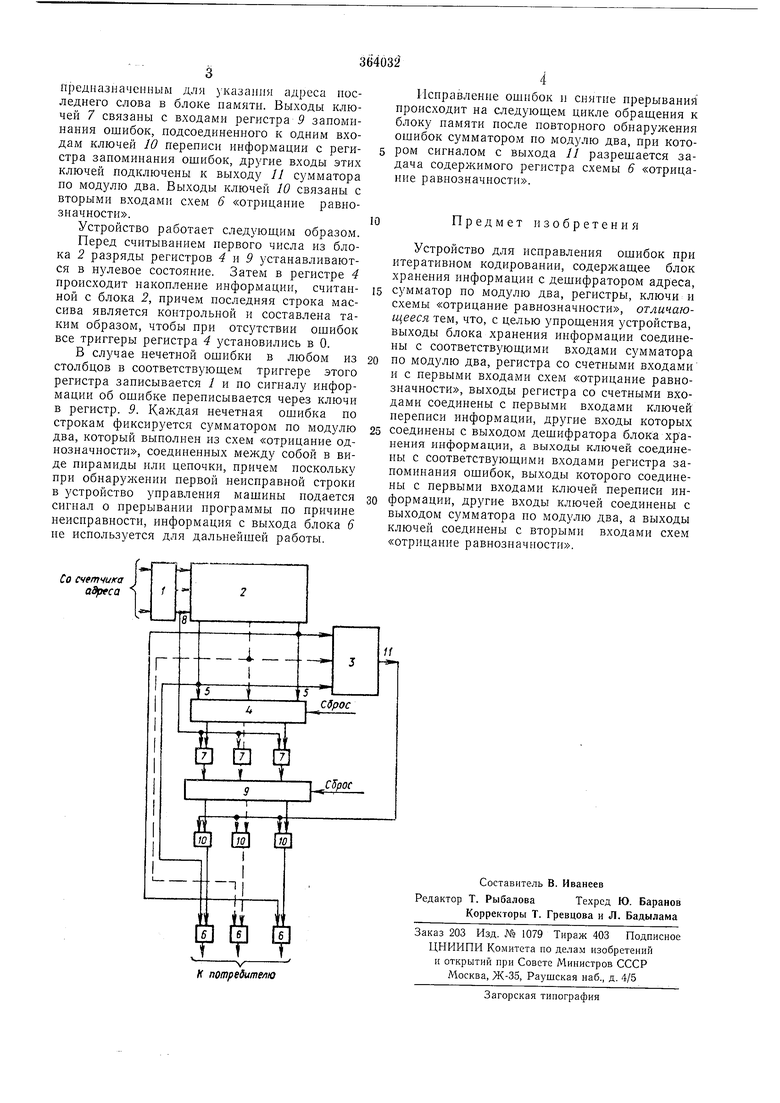

На чертелсе показана блок-схема предлагаемого устройства.

Устройство содержит дешифратор / адреса, блок 2 хранения информации, подключенный к сумматору 3 по модулю два, к регистру 4 со счетными входами 5 и к первым входам схем 6 «отрицание равнозначности и ключи 7 переписи информации регистра 4. Одни входы ключей соединены с выходами регистра, а другие - с выходом 8 дешифратора,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок при итеративном кодировании | 1977 |

|

SU680061A2 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ | 1969 |

|

SU251253A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| УСТРОЙСТВО для КОРРЕКЦИИ ДВУМЕРНОГО ИТЕРАТИВНОГО КОДА | 1972 |

|

SU332462A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Устройство для декодирования итеративного кода | 1988 |

|

SU1547080A1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297034C2 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

Авторы

Даты

1973-01-01—Публикация