преднщущих элементов И второй и третьей групп, выходы первых элементов НЕРАВНОЗНАЧНОСТЬ первой и второй групп и выходы элементов И второй и третьей групп соединены.с входами элементов И четвертой группы, выходы одних из которых соединены со

входами соответствующих элементов ИЛИ второй группы, выходы которых, выходы других элементов И четвертой группы, а также выходы элементов НЕРАВНОЗНАЧНОСТЬ первой и второй групп подключены к входам элементов И первой группы..

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1978 |

|

SU763975A1 |

| Запоминающее устройство | 1976 |

|

SU639023A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1984 |

|

SU1215139A1 |

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| Многоканальное устройство исправления ошибок для магнитных накопителей | 1986 |

|

SU1383440A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

, ЗАПОМИНА1ШЩЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее накопитель, регистр числа, две группы сумматоров по модулю два, элемент задержки и; первую группу элементов ИЛИ, выходы которых соединены с информационными входами регистра числа, выходы которого подключены к входам сумматоров по модулю два групп и являются информационными выходами устройства, инфор мационными, входами которого 5вл5Й6тся первые входы одних из элементов ИЛИ первой группы, первые входы других из которых соединены с выходами сумматоров по модулю два групп, вторые входы элементов ИЛИ первой группы подключены к выходам накопителя, информационные входы которого соединены с выходами регистра числа, а один из управляющих входов накопителя подключен к первому выходу элемента задержки, второй выход которого соединен с управляющим входом регистра числа, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства за счет обеспечения возможности исправления ошибок, в него введены три группы элементов НЕРАВНОЗНАЧНОСТЬ, сумматор по модулю два, две группы Элементов НБ, два элемента ИЛИ-НЕ,, четыре группы элементов И, вторая группа элементов ИЛИ, элемент И-НЕ и элемент ИЛИ, причем первые входы элементов НЕРАВНОЗНАЧНОСТЬ пер1 вой группы соединены с выходами сумматорвв по модулю два первой группы, вторые входы - с одними из контрольных выходов регистра числа и первыми входами сумматора по модулю два, вторые входы которого соединены с другими контрольными выходами регистру числа и с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ второй , вторые входа которых соединены с выходами сумматоров по модулю два второй группы, выходы элементов НЕРАВНОЗНАЧНОСТЬ первой и второй групп соедине ны соответственно с входами элементов НЕ первой и второй групп и вхо- . дами первого и второго элементов ИЛИ. i НЕ, выходы элементов И первой группы соединены с первыми входами элементов (П НЕРАВНОЗНАЧНОСТЬ третьей группы,вто1рые входы которых соединены с выходами регистра числа, а выхода - с вторыми входами элементов «ли первой группы, jBHXoiftJ первого и второго элементов ИЛИ-НЕ соединены соответственно с первьши входами последних элементов И второй и третьей групп и с первым и вторым входами элемента d И-НЕ, выход КОТОРОГО соединён с первь1м входом элемента ИЛИ, второй вход ;которого является Одним из управляющих входов устройства, а выход со- sl ;единен с входом элемента задержки, третий выход которого подключен к о управляющим входам элементов НЕРАВНОЗНАЧНОСТЬ третьей группы, выход сумматора по модулю два соединен с вторьзми входами последних элементов .И второй и третьей группы, выходы элементов НЕ первой и второй групп соединены соответственно с одноименными входами Соответствующих, элементов И второй и третьей групп, кроме последних элементов И, выходы элементов НЕРАВНОЗНАЧНОСТЬ первой и второй групп, кроме первых, подключены соответственно к одноименным входам

Изобретение относится к цифровой вычислительной технике и может быть использовано для построения высоконадежных запоминающих устройств. Известно запоминающее устройство о исправлением ошибок при итеративном кодировании, содержащее блок хра нения информации с дешифратором адрв са, сумматор по модулю два, регистры ключи, элементы НЕРАВНОЗНАЧНОСТЬ, элементы И, ИЛИ и счетчик, причем выходы блока хранения информации соединены с соответствующими .входами сумматора по модулю два, регистра со счетными входами и с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ, выходы регистра 9 счетныйи входами соедине ны с первыми входами ключей, другие входы которых соединены с выходом де шифратора блока хранения информации, ,а выходы ключей, соединены с соответствующими вxoдa m регистра запоминания ошибок, выходы которого соединены с входами первого элемента ИЛИ и с первыми- входами ключей регистра запоминания оши.бок, другие входы которых соединены с входом счетчика и с выходом первого элемента и, а выходы - с вторыми входагли элементов НЕРАВНОЗНАЧНОСТЬ, первый выход счет,чика подключен к одному и.э входов . первого элемента И, другой вход кото 1рого подключен к выходу сумматора, по .модулю два, второй выход счетчика подключен к одному из входов второго элемента ИЛИ, другой вход которого соединен с выходом второго элемента И, входы второго элемента И соединены соответственно с первым и третьим выходами счетчика и выходом первого э;аемента ИЛИ. Исправление ошибок в этом устройстве происходит с ИСПОЛ зованиём двухмерного итеративного . кода, синдром ошибки которого вычисляется путем сложения по модулю два разрядов, находящихся в строках и столбцах считанного массива данных. Отказавший бит фиксируется на пересеченинг строки и столбца, сумма разрядов в-которых равна единице {1 , Недостатками этого устройства являются невысокая надежность и быстродействие, Так как оно способно исправить в массиве данных только однобитовую ошибку и лишь по завершении считывания последней ячейки. Наиболее близким к изобретению является запоминающее устройство с самоконтролем, .содержащее накопителе, блок адресных, цепей, блок местного управления, элементы ИЛИ, регистр слова., две группы сумматоров по модулю два и блок сравнения контрольных разрядов, причем адресные входы накопителя соединены с выходами блока адресных цепей, адресные входы KqToporo соединены с адресными шинами устройства, а.управляющие с первьтми выходами блока местного управления, входные управляк)щие шины устройства соединены с управляющими входами блока местного управ-.. ления, вторые выходы которого соединены с управляющими входами . накопи-теля и регистра слОва, а выход koH-ца операции - с выходной .управляющей шиной устройства, выходы элементов ИЛИ соедине.ны с входами регистра слова, выходы информационных разрядов которого соединены с входами сум-, маторов по модулю два и с выходными информационны.ми шинами устройства, а выходы контрольных разрядов - с первыми входами блока сравнения контрольных разрядов, вторые входы которого соединены с выходами сумматоров по модулю два, первые входы элемен- тов ИЛИ соединены с выходными инфор- мационными шинами устройства и выходами сумматоров по модулю два, а вторые входы - с выходом накопителя. В данном устройстве информация.в накопитель записывается в виде двухмерного итеративного кода, контрольные, разряды которого (групповой и вет очной четности) вычисляются сумматорами по модулю два первой и второй групп. При считывании кодового слова эти же сумматоры снова вычисляют контрольные разряды, которые срязниваются со считанными в блоке сраврения контрольных разрядов При отсутствии равенства на выход, устройства поступает сигнал ошибки 2j .

Недостатком этого устройства является невысокая надежность из-за отсутствия возможности исправления ошибок.

Цель изобретения - повышение надежности работы устройства путем . обеспечения возможности исправления ошибок.

Указанная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель-, регистр числа, две группы, сумматоров по модулю два, элемент задержки и первую группу элементов ИЛИ, выходы которых соединены с информационными входами регистра числа, выходы которого подключены к входам сумматоров по модулю два групп и являются информационными выходами устройства, ийформационными входами которого являюeg первые входы одни-х из элементов ИЛИ пер1вой группы, ,первые входы других из которых соединены с выходами сумматоров по модулю два групп, вторые входы элементов ИЛИпервой группы подключены к выходам накопителя, информационные входы которого соединены с выходами регистра числа,, а один из управляющих входов накопителя подключён к первому выходу элемеи та задержки, второй выход которого соединен с управляющим входом регистра числа, введены три группы элементов НЕРАВНОЗНАЧНОСТЬ, сумматор по модулю два, две группы элементов НЕ, два элемента ИЛИ-НЕ, четыре группы элементов Ht вторая группа элементов ИЛИ, элемент И-НЕ и элемент ИЛИ, причем первые входы элементов НЕРАВНО- / ЗНАЧНОСТЬ первой группы соединены с выходами сумматоров по модулю два первой группы, вторые входы - с одними из контрольных выходов регистра числа.и nepBbiMH входами сумматора по модулю два, вторые входы которого соединены с другими контрольными выходами регистра числа и с первыми , входами элементов НЕРАВНОЗНАЧНОСТЬ, второй группы, вторые входы которых соединены с выходами сумматоров по модулю два второй группы, выходыэлементов НЕРАВНОЗНАЧНОСТЬ первой и второй группсоединены соответственно, с входами элементов НЕ и второй групп и входами первого и второго элементов ИЛИ-НЕ, выходы элементов И перврй группы соединены с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ

тре.тьей группы, вторые входы которых соединены-с выходами регистра числа, а выходы - с вторыми входами элементов ИЛИ первой группы, выходы первого и второго элементов ИЛИ-НЕ соединены соответственно с первыми входами по9ледних элементов И второй и третьей

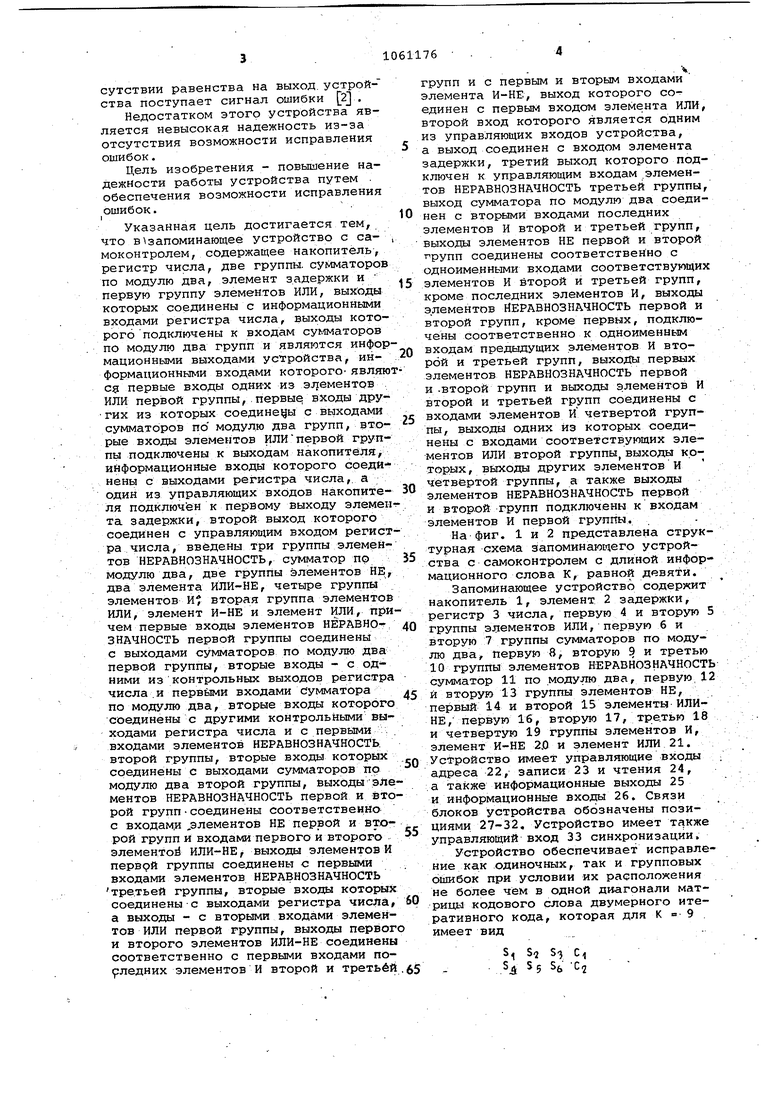

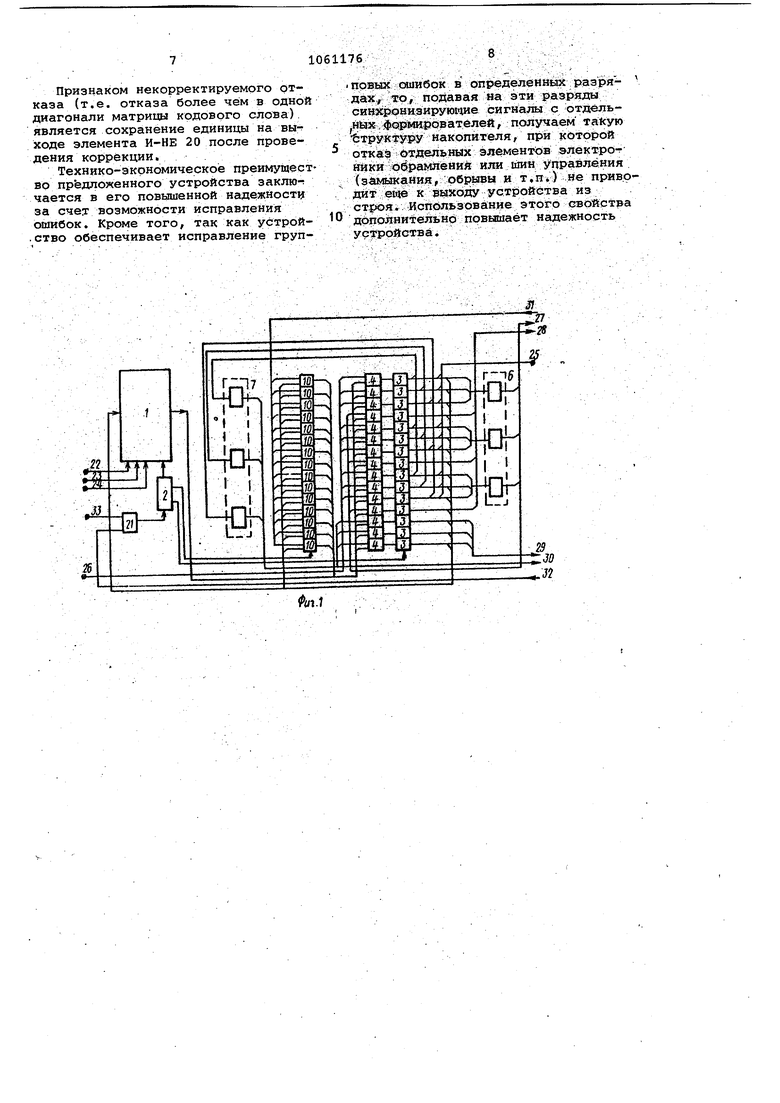

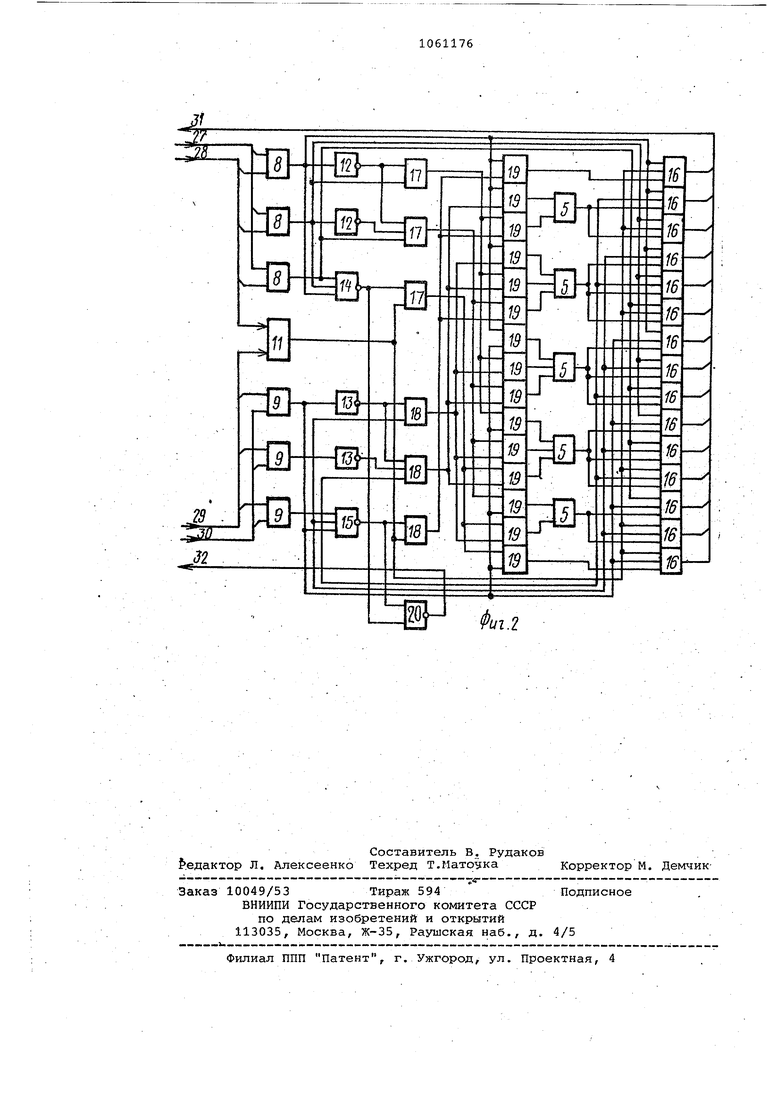

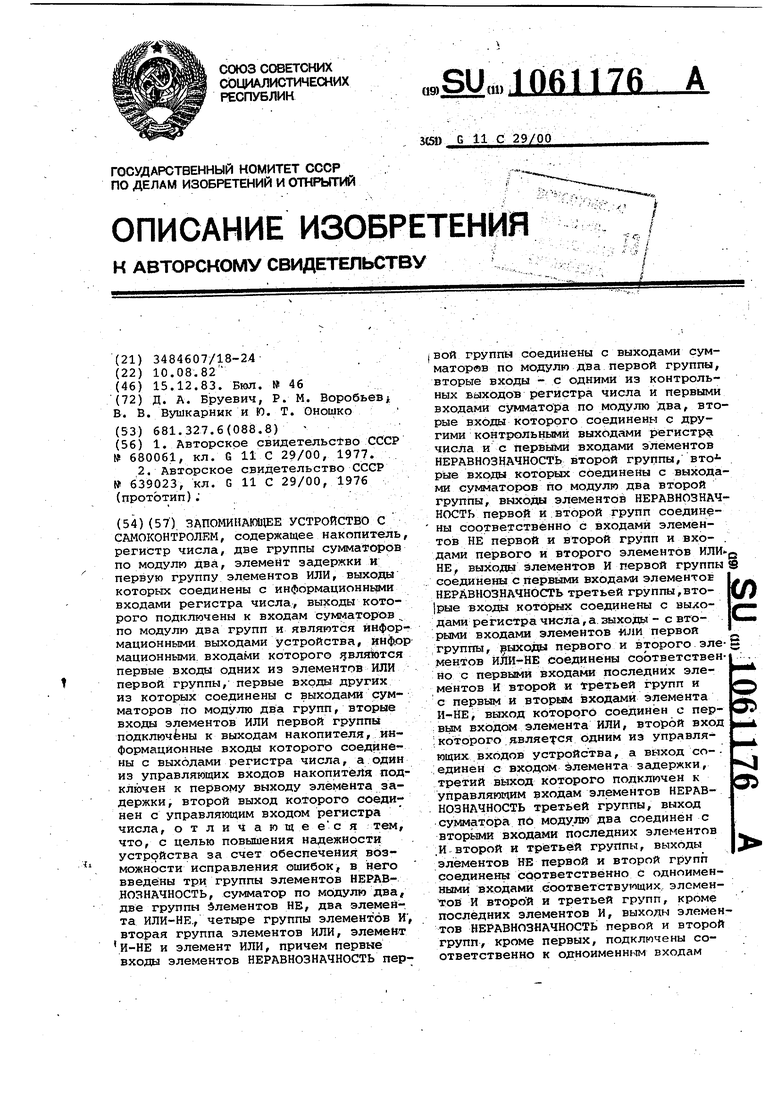

групп и с первым и вторым входами элемента И-НЕ, выход которого соединен с первым входом элемента ИЛИ второй вход которого является одним из управляющих входов устройства, а выход соединен с входом элемента задержки, третий выход которого подключен к управляющим входам элементов НЕРАВНОЗНАЧНОСТЬ третьей группы выход сумматора по модулю два соединен с вторыми входами последних элементов И второй и третьей групп, выходы элементов НЕ первой и второй трупп соединены соответственно с одноиме.нными входами соответствующи элементов И второй и третьей групп, кроме последних элементов И, выходы элементов НЕРАВНОЗНАЧНОСТЬ первой и второй групп, кроме первых, подключены соответственно к одноименным входам предыдущих элементов И второй и третьей групп, выхода первых элементов НЕРАВНОЗНАЧНОСТЬ первой и .второй групп и выходы э.лементов И второй и третьей групп соединены с входами элементов И четвертой группы, выходы одних йэ которых соединены с входами соответствующих элементов ИЛИ второй группы выходы которых, выходы других элементов и четвертой группы, а также выходы элементов НЕРАВНОЗНАЧНОСТЬ первой и второй групп подключены к входам элементов И первой группы. На фиг. 1 и 2 представлена структурная схема запоминающего устройства с сгииоконтролем с длиной информационного слова К, равной девяти.

Запоминающее устройство содержит накопитель 1, элемент 2 задержки, регистр 3 числа, первую 4 и вторую Группы элементов ИЛИ, первую 6 и вторую 7 группы сумматоров по модулю два. Первую 8, вторую 9 и третью 10 группы элементов НЕРАВНОЗНАЧНОСТ сумматор 11 по .модулю два, первую,1 и вторую 13 группы элементов НЕ, первый 14 и второй 15 элементы ИЛИНЕ, первую 16, вторую 17, тре.тью 18 и четвертую 19 группы элементов И, элемент И-НЕ 2.0 и элемент ИЛИ 21. Устройство имеет управляющие входы адреса 22, записи 23 и чтения 24, а также информационные выходы 25 и информационные входы 26. Связи блоков устройства обозначены позициями; 27-32. Устройство имеет управляющий вход 33 синхронизации.

Устройство обеспечивает исправление как одиночных, так и групповых ошибок при условии их расположения не более чем в одной диагонали матрицы кодового слова двумерного итеративного кода, которая для К 9 . имеет вид

S-2 5э С,

М 5 $5 Sf, С,

r 8 9 - p4 Cj Cj,

Работу устр9йс.тва рассмотрим в режимах записи и С51йтывания.

В режиме записи на вход 33 поступает сигнал Запуск, на вход 23 признак записи, на вход 22 - адрес выбранной ячейки накопителя, а на входа 26 - слово данных,. Последнее, через элементы ИЛИ 4 поступает на входы регистра 3. .Сигнал Запуск проходит элементИЛИ 21 и поступает на вход элемента 2 задержки, с второго/выхода которого через заданное время выдается синхронизирующий сиг нал, заносящий слово данных в регистр 3. Контрольные разряды двумерного итеративного кода групповой четности формируются сумматорами 6 по модулю два, а контрольные разряды веточной четности сумматорами 7 -по модулю два. С вы|ходов сумматрров контрольные разряды, проходят элементы ИЛИ 4 и также записываются в регистр 3, образуя полное кодовое слово. Затем происходит запись содержимого регис ра в накопитель 1 по адресу, .поданному на вход 22. С этой целью в накопитель подается синхронизирующий сигнал с первого выхода элемента 2 задержки и признак записи с входа 23

В режиМесчитывания на вход 24 поступает признак чтения, на вход 33 сигнал Запуск, а на вход 22 - адрее выбранной ячейки. После выдачи в йакопитель 1 синхронизирующего сигнала с первого выхода элемента 2 задержки, содержимое выбранной ячейки поступает на выход накопителя и через элементы ИЛИ 4 записывается в регистр 3, Суммматоры 6 и 7 по модулю два формируют контрольные . раз.ряды групповой и веточной четное ти., которые поступают соответственно на одни из входов элементов НЕРАВНОЗНАЧНОСТЬ 8 и 9. Одновременно на другие входы элементов НЕРАВНОЗНАЧНОСТЬ 8 и 9 с регистра 3 подаются контрольные разряды групповой С|-С9 и веточнЬй четности, которые непосредственно считываются иэ накопителя 1. Результат сравнения сформированных.и считанных контрольных разрядрв, проведенного на элементах НЕРАВНОЗНАЧНОСТЬ 8 и 9, представляет собой синдром ошибки ,. Если хотя бы один из его разрядов не )авен нулю, то на выходе 32 элемента И-НЕ 20 появляется сигнал ошибки, т.е., . Е ErVEft (e,vejVe,)v

(e vejveu),

где Ер. и Е - признак ошибки при сравнении контрольных разрядов соответственно групповой и веточйой

четности. Логическое сложение осуществляется элементами ИЛЙ-НЕ 14 и 15 и И-НЕ 20.. Признаком неисправности в однрм из контрольных разрядов , является наличие логической единицы На выходе сумматора 11 пр модулю два .

Е С«®С2®Сз®С,(©С5®Сб .

С помощью элементов НЕ 12 и 13 и элементов И 17 и 18 опре челяются первые по порядку, не равные .нулю, разряды синдрома ошибки групповой и веточной четности. Либо признак ошибки-в соответствующих контрольны

ел е4

. es. 64 е е У 64 еу eg «;

Так как при совпадении логических единиц на каком-либо элементе И второй 17 или третьей 18 групп обеспечивается блокировка последующих элементов И той же группы, то только по одному элементу .из каждой группы может находиться в активном состоянии.

Затем с помощью элементов И 19 и элементов ИЛИ 5 определяется одна из семи возможных диагоналей матрицы кодового слова, включающая отказавшие разряды .

gr«и; . .

g., ve{e;veUkve;e; e e;e;vee;ve e ,e ve eveBeg

ei e g.

B 4

Для разрядов позиция ошибки фиксируется с помощью элементов И 16 при совпадении д; с соответсфвующими значениями е, -е и е , для разрядов - с соответствующими значениями, е, - е и ЕК, а для разрядов - с соответствующими значениями и ЕК . Например Ss+ 8с2

С5 С выходов элементов И 16 позиции

ошибок поступают на одни из входов элементрв;НЕРАВНОЗНАЧНОСТЬ 10, на другие входы которых с регистра 3 подается считанное крдрвое слрво. Разряды, позиции ошибок которых равны единице, инвертируются, после чего исправленное кодовое слово через элементы ИЛИ 4 вновь записывается в регистр 3, откуда его инфорК1ационные разряды поступают на выходы 25..

Признаком некорректируемого отказа (т.е. отказа более чём в одной диагонали матрицы кодового слова). является сохранение единицы на выходе элемента И-НЕ 20 после проведения коррекции.

Технико-экономическое преимущество предложенного устройства заключается в его повышенной надежности за счет возможности исправления ошибок. Кроме того, так как устрой.ство обеспечивает исправление груп-повых ошибок в определенных раэрядах,, то, подавая на эти разряды синхронизируклцие сигналы с отдельjHtjx,формирователей, получаем та1сую 6трукт5 ру накопителя, при которой отказ отдельных элементов электроники обрамлений или шин управления (замыкания, обрывы и т.п.) не приводит etue к эыходу устройства из строя. Использование этого свойства дополнительно повышает надежность устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для исправления ошибок при итеративном кодировании | 1977 |

|

SU680061A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство | 1976 |

|

SU639023A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-12-15—Публикация

1982-08-10—Подача