Изобретение относится к области цифровой вычислительной техники и может быть использовано в цифровых вычислительных машинах.

Известно постоянное запоминающее устройство с объединенными рядами запоминающих элементов и с записью информации в восьмеричном коде, содержащее запоминающие трансформаторы, кодовые нровода, входные и выходные триоды, диодные шифраторы, нреобразующие восьмеричный код в двоичный. По этому же припцину могут быть построены постоянные запоминающие устройства с записью информации в любом л-ричном или блочном коде.

К недостаткам таких запоминающих устройств следует бтнести следующее:

-большое количество диодов в шифраторе, что влечет уменьшение надежности ПЗУ;

-нагрузка на запоминающий трансформатор меняется в зависимости от цифры л-ричного кода, соответствующей данному заноминающему трансформатору (число нагрузок может -меняться от 1 до т logaw, где т - ближайшее целое число к Iog2n), что вызывает разброс амплитуд выходных сигналов, и следовательно, уменьшает зону устойчивой работы ИЗУ;

-сигнал с выходной обмотки запоминающего трансформатора должен пройти в худ2

шем случае через два пасснвных элемента шифратора (два диода), нри этом его амплитуда значительно уменьшается, что предполагает работу шифратора на активный усиливающий элемент;

-слаботочные цепи, куда входят обмотки воспроизведення н шифраторы, достигают значительной длины, нх трудно вынолнить, соблюдая правила высокочастотного монтажа, и защитить от наводок, характер которых трудно заранее нредусмотреть;

-низкое быстродействие ЗУ, связанное с нримепением шифратора на нассивпых элементах вместе с носледующей усилительной схемой;

-из-за недостаточной нагрузки во вторичных обмотках, запоминающих трансформаторов возмолсно возникновение колебательного переходного процесса, что также снижает быстродействие.

Целью нредлагаемого изобретения является улучшение конструкции постоянного запоминающего устройства, что влечет за собой удобство в экснлуатации, возможность интегрального исполнения, уменьшение габаритов, веса, улучшение помехозащищенности за счет уменьшения длины слаботочных связей, увеличение наделчности, а также увеличение быстродействня.

Цель изобретения достигается тем, что шифратор на многообмоточных трансформаторах, входные обмотки которого связаны с запоминающими трансформаторами через входные транзисторы, базы и эмиттеры которых подключены к выходным обмоткам запоминающих трансформаторов, причем эмиттеры, подключенные к запоминающим трансформаторам одного ряда опроса, объединены и подключены к одному из выходов дешифратора, управляющего выбором этого ряда запоминающих трансформаторов, а коллекторы входных транзисторов, подключенные к одноименным запоминающим трансформаторам каждого ряда опроса, объединены и подключены к одной из входных обмоток щифратора, подключенных через токозадающее сопротивление к источнику питания. Выходные обмотки многообмоточных трансформаторов шифратора подключены к базам и эмиттерам выходных транзисторов. Эмиттеры последних объединены и подключены к одному из выходов дешифратора, управляющего выбором постоянного запоминающего устройства. В трансформаторы щифратора и в запомипающие трансформаторы введены донолнительпые обмотки, выполненные в виде дешифрирующих колец из резистивного материала.

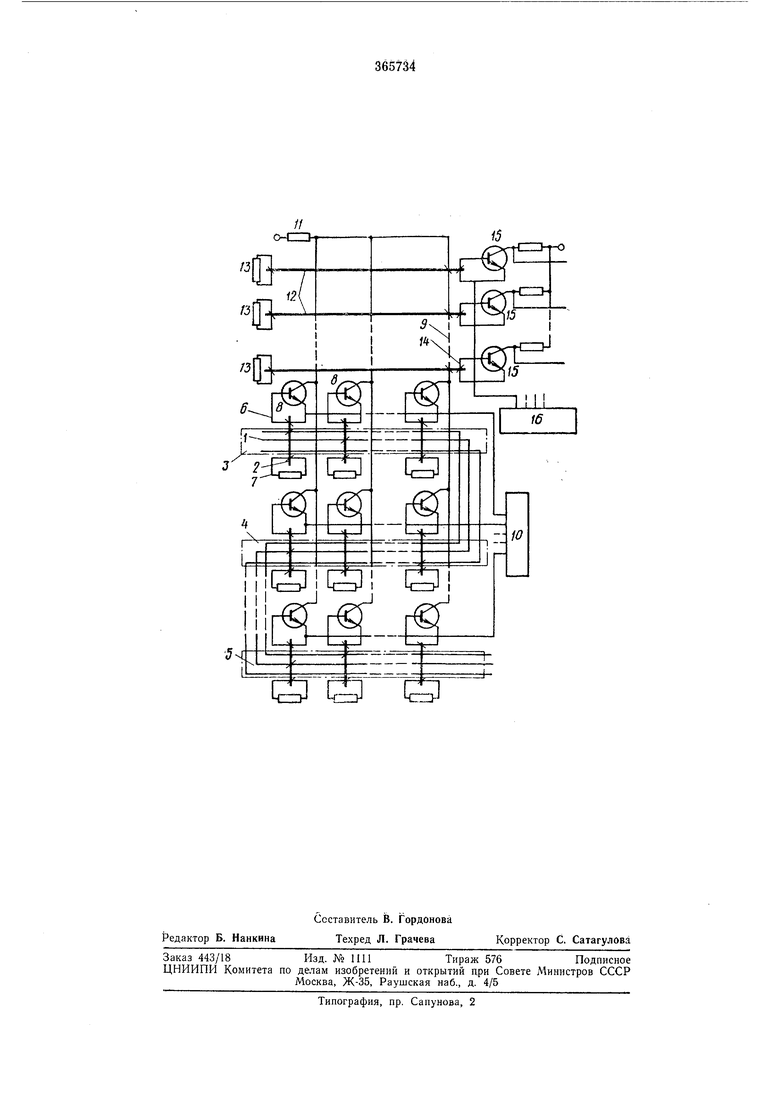

На чертеже изображен один из разрядов постоянного запоминающего устройства для хранения информации в л-ричном коде.

Устройство состоит из кодовых проводов 1, прошивающих сердечники 2 запоминающих трансформаторов, каждый ряд 3, 4 или 5 которых образует группу по п сердечников 2, причем каждый сердечник соответствует цифре rt-ричного кода, а кодовый провод 1 проходит через один из л сердечников в зависимости От кода; вторичных обмоток 6 запоминающих трансформаторов, демпфирующих колец 7 запоминающих трансфорд-гаторов, которые служат для подавления колебательного переходного процесса в цепях трансформаторов, входных полупроводниковых транзисторов 8 (активных элементов), объединенных по коллекторам и подключенных к соответствующим входным обмоткам 9 щифратора, а также соединенных с трансформаторами одного ряда опроса 3, 4 или 5 и объединенных по эмиттерам, подключенных к дешифратору 10 выбора ряда опроса запоминающих трансформаторов 3, 4 или 5, причем входные обмотки Щифратора 9 подключены через токозадающее сопротивление // к источнику питания; сердечников 12 трансформаторов шифратора, демпфирующих колец 13 трансформаторов щифратора, выходных обмоток 14 трансформаторов щифратора, соединенных с выходными активными элементами (транзисторами) 15 шифратора; кроме того, в состав постоянного запоминающего устройства входит схема 16 для управления выходными элементами. Запоминающие трансформаторы

всех рядов опроса 3, 4 или 5, соответствующие одноименны.м цифрам п-ричного кода, образуют ряды записи-воспроизведения (столбцы). Устройство работает следующим образом. При выборе дешифратором 10 одного ряда

онроса 3, 4 или 5 запоминающих трансформаторов входные полупроводниковые транзисторы 8 будут открыты по эмиттерам, а при протекании импульса тока опроса в кодовом проводе / один из этих транзисторов 8 откроется

и по базе, в результате чего во входной обмотке 9 щифратора возникнет ток, который наведет в выходных об.мотках 14 шифратора сигналы, которые затем будут усилены выходными транзисторами У5.

Предмет изобретения

Постоянное запоминающее устройство с записью информации п-ричными блочными кодами, содержащее запоминающие трансформаторы, объединенные в ряды опроса и ряды записи-воспроизведения, дешифратор, шифратор, входные и выходные транзисторные ключи и блок управления, отличающееся тем,

что, с целью повышения быстродействия устройства и его надежности, база и эмиттер каждого входного транзисторного ключа одного ряда опроса объединены через выходную обмотку соответствующего заноминающего

трансформатора и подключены к соответствующему выходу дещифратора, коллекторы входных транзисторов каждого ряда записивоспроизведения объединены и подключены ко входным обмоткам шифратора, выполненного па многообмоточных трансформаторах, выходные обмотки которых подключены к базам и эмиттерам соответствующих выходных транзисторных ключей, эмиттеры которых объединены и подключены к соответствующему выходу блока управления, причем в трансформаторы шифраторов и в запоминающие трансформаторы введены дополнительные обмотки, выполненные в виде дешифрирующих колец из резистивного материала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трансформаторное постоянное запо-МиНАющЕЕ уСТРОйСТВО | 1979 |

|

SU841048A1 |

| Шифратор для трансформаторного постоянного запоминающего устройства | 1976 |

|

SU613399A1 |

| Реверсивный дешифратор | 1976 |

|

SU604151A1 |

| МАГНИТНО-ТИРИСТОРНЫЙ ФОРМИРОВАТЕЛЬ ТАКТОВЫХ ИМПУЛЬСОВ | 1972 |

|

SU353338A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU347797A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| Устройство для вывода данных из управляющей цифровой вычислительной машины на обьекты | 1974 |

|

SU507865A1 |

| ПАРАФАЗНЫЙ ГЕНЕРАТОР ЛИНЕЙНО-ИЗМЕНЯЮЩИХСЯНАПРЯЖЕНИЙ | 1972 |

|

SU423235A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР КОДОВ И НАПРЯЖЕНИЙ | 1970 |

|

SU287419A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

Авторы

Даты

1973-01-01—Публикация