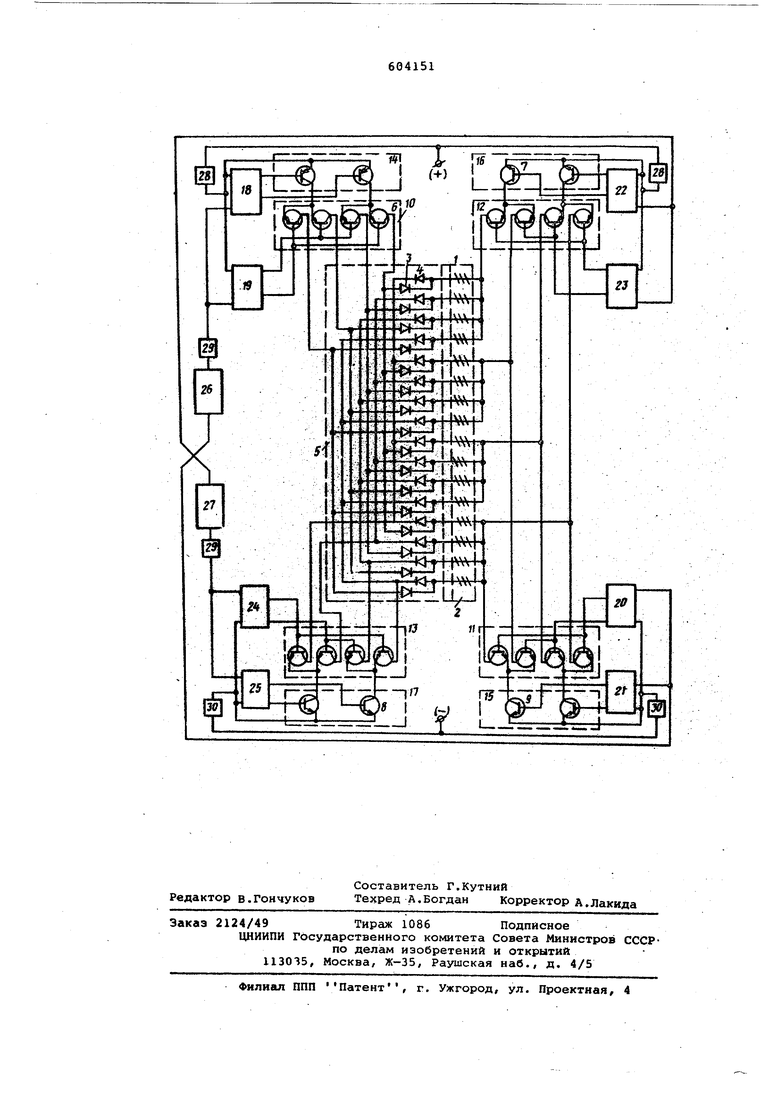

(54) РЕВЕРСИВНЫЙ ДЕШИФРАТОР ключи соединены с выходами одного дешифратора первой ступени/ а объединен ные группы базовых выводов транзисторов каждого транзисторного матричного дешифратора второй ступени - с ВЕЛхода ми другого дешифратора первой ступени На чертеже изображена схема описыв емого устройства. Реверсивный дешифратор содержит ма рицу 1 магнитного оперативного запоми нающего устройства (МОЗУ), на шинах 2 которой находятся сердечники, диоды 3,4 конечной (третьей) ступени 5 деши ратора, транзисторы 6,7 типа р-п-р и транзисторы 8,9 типа п-р-п первого 10 второго 11 и 12 третьего четвертого 1 транзисторных матричных дешифраторов второй ступени дешифратора транзистор ные ключи 14-17, дешифраторы 18-25 пер вой ступени дешифратора, формирователи 26,27 импульсов тока, ограничители тока 28-30. На чертеже изображена схема реверсивного дешифратора на п 16 выходов. Для коммутации импульсов тока считы вания съема содержит первую ступень дешифратора считывания, в которой используется четыре дешифратора 18-21, выполненные, например, на МПТ, транзисторные ключи 14, 15 для выбора эмит геров транзисторов 6,9 транзисторных матричных дешифраторов 10, 11 второй ступени, диоды 3 третьей ступени 5 дешифратора. Четыре дешифратора 22-25 на МПТ ступени, транзисторные ключи 16, 17, транзисторные матричные дешифраторы 12,13 второй ступени, диоды 4 третьей ступени 5 дешифратора обеспечивают ком г-1утацию импульсов тока записи ( с таким же числом элементов в каждой ступени, что и для дешифратора считывания) . Выходы дешифратора 18 на МПТ соединены с базовыми цепями транзисторов транзисторных ключей 14, а выходы дешифратора 19 на МПТ - с базовыми цепями транзисторов 6 транзисторного мат ричного дешифратора 10, .эмиттеры транзисторов объединенных групп которого соединены с коллекторами соответствующих транзисторов транзисторных ключей 14. Выходы транзисторного матричного дешифратора 10 подключены к анодам диодов 3, а к катодам диодов 3 подключены шины 2 матрицы 1 МОЗУ, к этим же точкам подключены аноды диодов 4. Катоды диодов 4 соединены с выходами транзисторного матричного дешифратора 13, входы которого подключены к выходам дешифратора 24 на МПТ и через тран зисторные ключи 17 - к выходам дешифратора 25 на МПТ. Вторые -концы шин 2 матрицы 1 МОЗУ объединены в группы и подсоединены к выходам транзисторных матричных дешифраторов 11, 12, входы которых подсоеди нены к выходам дешифраторов 20, 21 и 22,23 соответственно (выходы дешифраторов 22 и 21 подключены к матричным дешифраторам на транзисторах через транзисторные ключи 16 и 15 соответственно) . Для ввода информации в описываемый реверсивный дешифратор используются обмотки записи сердечников дешифраторов 18-25 на МПТ, обмотки считывания которых одним концом через резистор (на чертеже не показан) и ограничители тока 29 соединены, с формирователями 26 и 27 импульсов тока, а другим концом через диоды и резисторы ( на чертеже не показаны) и ограничители тока 28,30 - с источником питания. Работа устройства происходит следующим образом. При обращении к запоминающему устройству (ЗУ) вначале поступает код выбираемой шины матрицы на обмотки записи сердечников дешифраторов 18-25 на МПТ, причем одинаково готовят ся сердечники дешифраторов 18 и 22, 23,20 и 24, 21 и 25 на МПТ. После записи кода в каждом из них будет только одна проводящая ветвь с малым импедансом для распределяемого импульса формирователей 26, 27. В режиме считывания запускается формирователь 26, в выходную цепь которого включены обмотки считывания сердечников дешифраторов 18-21 на МПТ. Импульс тока формирователя 26,пройдя по проводящим ветвям дешифраторов 18-21 (в каждом дешифраторе только одна проводящая ветвь), создает напря жения, полярности и величины необходимой для открывания соответствующего транзистора. При этом, благодаря описанной последовательности связей, срабатывают по одному транзистору в транзисторных ключах 14, 15 и матричных дешифраторах 10, 11, что обеспечит выбор только одной шины 2 матрицы 1 МОЗУ Импульс тока считывания идет от полюса источника питания последовательно через ограничитель 28, выбранные транзисторы транзисторных ключей 14 и транзисторного матричного дешифратора 10, диод 3, выбранную шину 2, выбранные транзисторы транзисторного матричного дешифратора 11 и транзисторных ключей 15, ограничитель 30 на минус источника питания. Амплитуда импульса тока считывания и ее независимость от импеданса шины матрицы 1 определяются ограничителями 28, 30, которые целесообразно выполнять в виде нелинейного элемента, например, на магнитных сердечниках с ППГ. В виде таких же нелинейных элементов целесообразно выполнять и ограничители 29. Кроме того, использование для ограничения амплитуды импулье сов тока одинаковых ограничителей 28 и 30 уменьшает перепад потенциала на шинах 2 матрицы 1, делает его примерно pasHbjM потенциалу общей точки, что уменьшает помехи, возникающие в разрядных шинах матрицы из-за паразитных связей. В режиме записи запускается формирователь 27 и дальнейшая работа дешиф рирующих ступеней выбира шины 2 при записи происходит аналогично описанно для режима считывания. Таким ооразом,предлагаемый реверсивный дешифратор обеспечивает прохож жение импульсов тока считывания и тока записи по выбранной шине матрицы сердечников. Формула изобретения Реверсивный дешифратор для запомина ющих устройств на матрицах магнитных сердечников, шины которых соединены с диодами, образующими конечную ступень дешифрации, содержащий источник питания, транзисторные ключи, формирователи импульсов тока и ограничители тока, отличающийся тем,что с целью повышения быстродействия и упрощения, он содержит три ступени дешифрации с каскадным включением матрич ных дешифраторов, при этом вторая ступень выполнена на транзисторах, выводы конечного диодного матричного дешифратора, связанные с анодами диодов,подключены к коллекторам транзисторов типа р-п-р первого транзисторного матричного дешифратора второй ступени, выводы диодного матричного дешифратора, связанные с катодами диодов, подключены к коллекторам транзисторов типа п-р-п второго транзисторного матричного дешифратора второй ступени, объединенные аноды и катоды диодов конечного матричного дешифратора соединенк с шинами матриц магнитных сердечникоз, а другие концы указанных шин подключены к коллекторам транзисторов типа р-п-р и п-р-п соответственно третьего и четвертого транзисторных матричных дешифраторов второй ступени, объединенные группы эмиттеров транзисторов каждого транзисторного матричного дешифратора второй ступени через транзисторные ключи соединены с выходами одного дешифратора первой ступени, а объединенные группы базовых выводов транзисторов каждого транзисторного матричного дешифратора второй ступенис выходами другого дешифратора первой ступени. Источники информации, принятые во внимание при экспертизе: 1.Патент Англии 964487,кл.6 4 С, 1971. 2.Авторское свидетельство СССР 247351,кл. Н 03 К 13/247, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ДЕШИФРАТОР | 1969 |

|

SU247351A1 |

| Дешифратор для запоминающего устройства матричного типа | 1972 |

|

SU497728A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU277852A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Запоминающее устройство | 1974 |

|

SU491153A1 |

Авторы

Даты

1978-04-25—Публикация

1976-05-03—Подача