Изобретение относится к области вычислительной техники.

Известны устройства для интегрирования переменных, представленных в аналоговой форме с плавающей запятой, содержащие схему выбора максимального порядка, операционный усилитель-инвертор, компараторы, подключенные одними из входов к входным клеммам значений порядков, а выходами через дешифраторы к включенным во входную цепь усилителя-интегратора мантиссы ключам, вторые входы которых соединены со входными клеммами значений мантисс.

Предложенное устройство отличается от известных тем, что в него введена схема для запоминания наибольшего напряжения, выход которой через операционный усилитель-инвертор подключен ко входам компараторов, а вход присоединен к выходу схемы выбора максимального порядка и к дополнительному компаратору, подключенному через дополнительный дешифратор к ключам, установленным в цепи обратной связи операционного усилителя-интегратора мантиссы последовательно с основным и двумя дополнительными конденсаторами, причем каждый из них и вся цепь обратной связи зашунтированы дополнительными ключами.

Это позволило расширить диапазон изменения переменных, повысить быстродействие и

обеспечило возможность автоматического изменения масштаба.

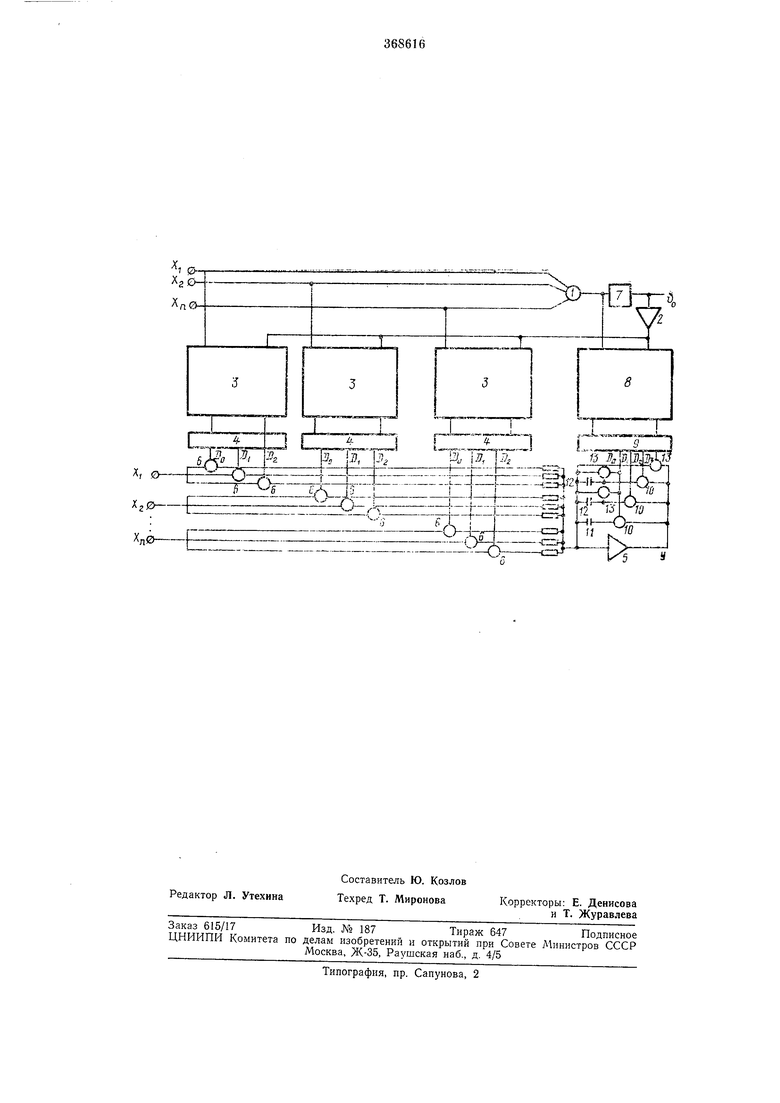

Блок-схема устройства приведена на чертеже.

Устройство содержит схему выбора максимального порядка /, операционный усилитель-инвертор 2, компараторы 3, подключенные одними из входов к выходным клеммам значений порядков, а выходами через дешифраторы 4 к включенным во входную цепь усилителя-интегратора мантиссы 5 ключам 6, вторые входы которых соединены с выходными клеммами значений мантисс.

Кроме того, устройство содержит схему для

запоминания наибольшего напряжения 7, выход которой через операционный усилительинвертор 2 подключен ко входам компараторов 3, а вход - к выходу схемы выбора максимального порядка / и к дополнительному

компаратору 8, подключенному через дополнительный дешифратор 9 к ключам JO, включенным в цепь обратной связи усилителяинтегратора мантиссы 5 последовательно с основным // и двумя дополнительными }2

конденсаторами, причем каждый из них и вся цепь обратной связи зашунтированы дополнительными ключами 13.

Схема выполняет функции интегрирования п входных величии, представленных в аналоговой форме с плавающей запятой:

Xi, xz,...,Xn - мантиссы входных переменных;

Xi, Х2,...,Хп - порядки входных переменных;

у - мантисса интеграла; vo - порядок интеграла; V - наибольшее значение порядка входных переменных.

На вход компаратора 8 поступает разность порядков - Vo,

где ло - значение порядка, хранящееся в схеме для запоминания наибольшего напряжения 7;

V - выходная Величина схемы выбора максимума 1.

Выходы дешифратора 9, присоединенного к компаратору 8, До, Ц, Дг, Дз соответствуют следующим значениям:

До 1 при .;

Д, 1 при Av 1;

U2 1 при Av 2;

при .

Выходы дешифратора 9 должны обеспечивать такую коммутацию в цепи обратной связи операционного усилителя-интегратора мантиссы 5, чтобы напряжение на основном конденсаторе 11 изменилось следующим образом:

при До-1 - осталось без изменения,

при Д -уменьшилось в 10 раз,

при уменьшилось в 100 раз,

при уменьшилось до 0.

Уменьшение напряжения на основном конденсаторе 11 достигается кратковременным подключением дополнительных конденсаторов 12 (соответственно при Д1 1 и ) и закорачиванием основного конденсатора 11 при . Эти переключения обеспечиваются ключами 10, управляемыми соответственно сигналами До, Д1, Д2, ДзПредлагаемая структура блока интегрирования обеспечивает изменение порядка значения интеграла в зависимости от изменения порядка значения подынтегральной функции в процессе интегрирования.

Схема работает следующим образом.

Значение наибольшей величины порядка интеграла, запомненное в схеме для запоминания наибольшего напряжения 7 с помощью компаратора 3 сравнивается со значением порядка подинтегральной функции. Если порядок выходной величины устройства меньше значения, запомненного в схеме для запоминания наибольшего напряжения 7, или равен этому значению, напряжение на конденсаторе // операционного усилителя-интегратора мантиссы 5 не изменяется, так как на выходе дешифратора 4, подключенного к компаратору 3, , Дl-fД2 Дз 0, и, следовательно, открыты дополнительные ключи 13, шунтирующие дополнительные конденсаторы 12 и подключающие основной конденсатор )/ к выходу операционного усилителя-интегратора

мантиссы 5. Если же порядок входной величины больше значения, запомненного схемой для запоминания наибольшего напряжения 7 (т. е. больше порядка интеграла), то компараторная схема 3 обеспечивает на выходе дешифратора 4 и равенство 1 одного из выходов дешифратора Дь Да или Дз (в зависимости от величины разности порядков интеграла и подинтегральной функции). При

Д1 1 или (открыт ключ 10) основной конденсатор 11 шунтируется одним из дополнительных конденсаторов 12, при основной конденсатор 11 шунтируется дополнительным ключом 13.

Таким образом, при порядке входной величины, большем порядка интеграла, основной конденсатор 11 операционного усилителя-интегратора мантиссы 5 разряжается (частично нли полностью), обеспечивая соответствующее уменьшение мантиссы интеграла.

Шунтирование дополнительного конденсатора 12 происходит за время, пока схема для запоминания наибольшего напряжения 7 не запомнила новое значение порядка. После

этого порядок интеграла будет равен порядку подынтегральной величины v, следовательно, на выходе дешифратора будет: , 0; ключи 10 закроются, ключи 13 - откроются. Таким образом, в предлагаеMOM устройстве осуществляется изменение масштаба при интегрировании.

Предмет изобретения

Устройство для интегрирования переменных, представленных в аналоговой форме с плавающей запятой, содержащее схему выбора максимального порядка, операционный усилитель-инвертор, компараторы, подключенные одними из входов к входным клеммам значений порядков, а выходами через дешифраторы к включенным во входную цепь усилителя-интегратора мантиссы ключам, вторые входы которых соединены со входными

клеммами значений мантисс, отличающееся тем, что, с целью расширения диапазона изменения переменных, повышения быстродействия и обеспечения возможности автоматического изменения масштаба, в него введена

схема для запоминания наибольшего напряжения, выход которой через операционный усилитель-инвертор подключен ко входам компараторов, а вход присоединен к выходу схемы выбора максимального.порядка и к дополнительному компаратору, подключенному через дополнительный дешифратор к ключам, установленным в цепи обратной связи операционного усилителя-интегратора мантиссы последовательно с основным и двумя дополнительными конденсаторами, причем каждый из них и цепь обратной связи зашунтированы дополнительными ключами.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ПЕРЕМЕННЫХ, ПРЕДСТАВЛЕННЫХ В АНАЛОГОВОЙ ФОРМЕ С ПЛАВАЮЩЕЙЗАПЯТОЙ | 1972 |

|

SU353258A1 |

| Ш БИБЛИОТЕКАЮ. Я. Любарский | 1972 |

|

SU328472A1 |

| Устройство для формирования напряжения,пропорционального логарифму интервала времени | 1981 |

|

SU1013869A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ МНОГОЭЛЕМЕНТНЫХ ДВУХПОЛЮСНЫХ ЦЕПЕЙ | 2001 |

|

RU2212677C2 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 2014 |

|

RU2571618C1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1644370A1 |

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

Даты

1973-01-01—Публикация