.1

Предлагаемое устройство для выделения крайней единицы может найти применение в различных устройствах вычислительной техники, например при построении узлов прерывания.

Известны регистры, в которых выделение крайнего (приоритетного) триггера, находящегося в состоянии «1, осуществляется соединением нулевых входов триггеров каждого разряда через схемы «ИЛИ с единичными выходами всех предществующих IB порядке убывания приоритета триггеров с помощью отдельных вентилей (схем «И).

Недостатком указанной схемы является то, что для управления каждым триггером и.спользуется (га-1) вентиль, где п - номер данного триггера в порядке убывания приоритета, что при большой разрядности схемы ведет к значительной затрате оборудования (вентилей).

Цель изобретения заключается в уменьщении количества схем «И до т-1, где т - число разрядов регистра схемы.

В предлагаемом устройстве эта цель достигается путем соединения единичного выхода каждого триггера, кроме последнего с соответствующей схемой «И, выход которой подключен дополнительно введенные схемы «ИЛИ к .нулевым входам последующих в порядке убывания приоритета триггеров.

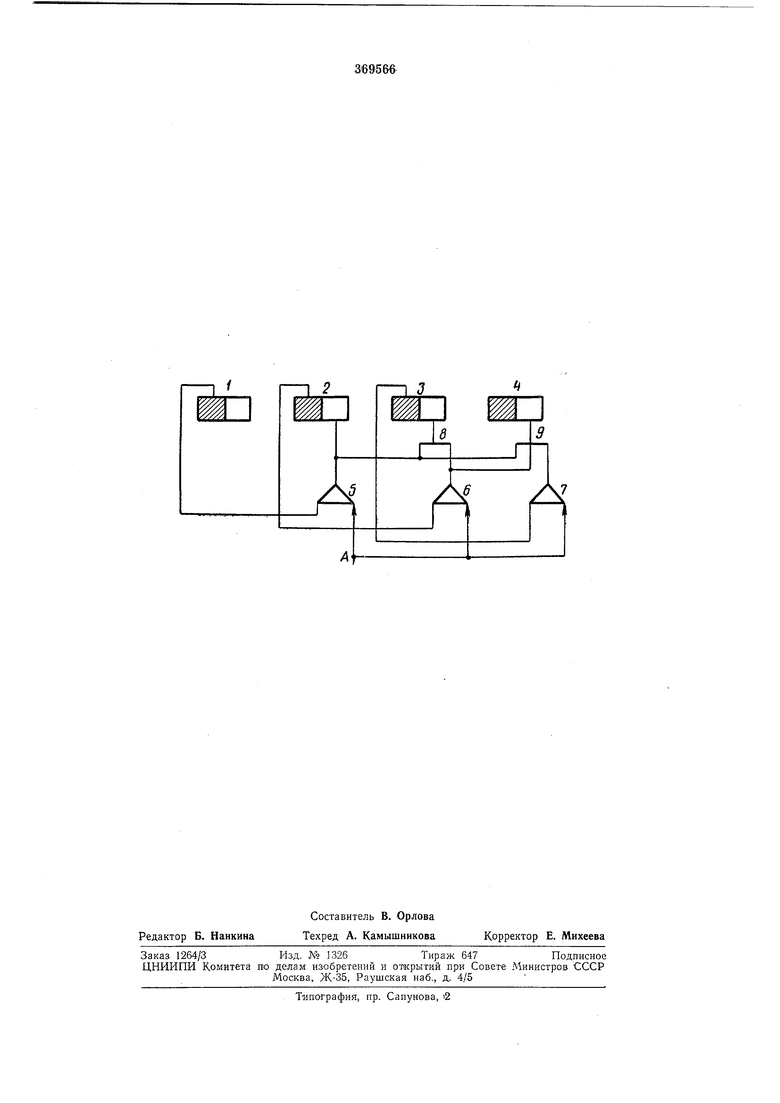

На чертеже представлено устройство для выделения крайней единицы на четыре разряда.

В состав устройства входят триггеры /-4, схемы «И 5, 6, 7 и схемы «ИЛИ 8, 9. Единичные плечи триггеров заштрихованы.

Пусть в исходном состоянии в триггерах записан код OiOl. Схемы «И 5 и 7 при этом будут закрыты, а схема «И 6 - открыта.

После подачи управляюшего импульса на входную шину (точка /4) сработает схема «И 6 и сигнал с ее выхода через схему «ИЛИ 8 подтвердит нулевое состояние триггера 3, а через схему «ИЛИ 9 установит в «О триггер 4.

Таким образом, в единичном состоянии останется только триггер 2.

Предмет изобретения

Устройство для выделения крайней единицы, содерл ащее триггеры, схемы «И, отличающееся тем, что, с целью сокращения количества оборудования при большой разрядности схемы, единичный выход калсдого триггера, кроме последнего, соединен с соответствующей схемой «И, выход которой подключен через дополнительно введенные схемы «ИЛИ к нулевым входам последующих в порядке убывания приоритета триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь разновесных кодов | 1985 |

|

SU1297031A1 |

| Устройство для формирования синхроимпульсов | 1979 |

|

SU777652A1 |

| Устройство переменного приоритета | 1983 |

|

SU1151964A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1310803A1 |

| Асинхронное приоритетное устройство | 1980 |

|

SU911529A1 |

| Устройство для формирования контрольного кода по модулю два | 1989 |

|

SU1683017A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 1973 |

|

SU389519A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1982 |

|

SU1070555A1 |

| Устройство для классификации двоичных чисел | 1975 |

|

SU545982A1 |

А

/V

ZV

Авторы

Даты

1973-01-01—Публикация