(54) АСИНХРОННОЕ ПРИОРИТЕТНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Асинхронное приоритетное устройство | 1980 |

|

SU960818A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Многоканальное устройство приоритета | 1984 |

|

SU1180895A1 |

| Многоканальное устройство приоритета | 1986 |

|

SU1352487A2 |

| Контроллер с переменным приоритетом | 1980 |

|

SU907550A1 |

| Приоритетное устройство для динамической памяти | 1982 |

|

SU1083191A1 |

| Многоканальное приоритетное устройство для динамической памяти | 1981 |

|

SU1003087A1 |

| Устройство приоритетного подключенияпРОцЕССОРОВ K ОбщЕй МАгиСТРАли | 1978 |

|

SU805312A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках управления устройствами общего пользования, например, в блоках управления общей памятью вычислительной системы. Конфликтные ситуации, возникающие в результате одновременного об ращения двух или более активных уст ройств к устройству общего пользования, разрешаются специальными аппаратными средствами, называемыми приоритетными устройствами. Подключение активных устройств осуществляется либо в соответствии с задан ными приоритетами, либо путем их последовательной коммутации. При первом способе подключения существует возможность монопольного использования устройства общего пользования теми активными устройствами, которые обладают высшим приоритетом, т.е. существует вероятность потери запросов. Второй способ став нее активные устройства в равные условия и время прохождения срочных запросов возрастает. Преодоление указанных недостатков привело к созданию устройств, способных распределять запросы по приоритетам без их потери. Известно многоканальное приоритетное устройство, выполненное в виде идентичных блоков (по одному в каждом канале), каждый из которых сот держит блок формирования и маскирования запросов и блок хранения кодов приоритетов, соединенный с блоком сравнения и с интерфейсным блоком. В процессе работы устройства логические блоки формируют на общей шине код, соответствукщий старшему по приоритету запросу или другую информацию, однозначно определяющую источник запросов, который подлежит, первоочередному обслуживанию. Устройство характеризует39ся широкими функциональными возможностями р . Недостатком данного устройства является сложность схемы и недостаточно высокое быстродействие. Поэтому применение этого устройства, несмотря на его широкие функциональ ные возможности, в простьпс системах оказывается неоправданным. Например, приоритетное устройство, предназначенное для подключения нескольких каналов к сверхоперативной памяти ЭВМ, должно иметь максимальное быстродействие, возможно даже в ущерб функциональной гибкости. Известно также достаточно простое приоритетное устройство с асинх ронным принципом работы, состоящее из схемы, определяющей приоритет по ступающих на нее запросов и схемы у равления, обеспечивающей взаимодей ствие выделенного запроса с устройством общего пользования 2J. Достоинство устройства в его аси ронности, что определяет достаточно высокое быстродействие и при котором отпадает необходимость в до полнительном оборудовании для созда ния синхроимпульсов управления. Недостаток устройства - обработка запросов в порядке прихода, что ставит их в равные условия и не дает преимущества срочным запросам. В результате время прохождения срочных запросов возрастает. J Прототипом предлагаемого изобретения является устройство приоритет содержащее регистр индикации запросов и вспомогательный регистр, выпо ненные на триггерах, схемы 2 И по две в каждом канале и схемы 2 ИЛИ по одной в каждом канале, причем ед ничный вход триггера каждого канал регистра индикации запросов соединен с соответствующим входом устрой ства, единичный выход триггера каждого канала регистра индикации.запросов через первый элемент 2 И дан ного канала соединен с единичным входом триггера вспомогательного регистра, единичный выход которого соединен с первым входом элемента 2 ИЛИ, и через второй элемент 2 И данного канала - с соответствующим выходом устройства, второй вход эле мента 2 ШМ соединен с выходом элемента 2 iilM предыдущего канала, а 4 выход - с нулевым входом триггера вспомогательно-го регистра последунидего канала и со вторым входом элемента 2 ИЛИ последующего канала, Поступающие на устройство приоритета запросы записываются в регистр индикации запросов, а затем по стробирукнцему синхроимпульсу через первые элементы 2 И переписываются во вспомогательный регистр, . Так как единичные выходы триггеров вспомогательного регистра более старших по приоритету каналов соединень: через элементы 2 ШЖ с нулевыми входами триггеров младших по приоритету каналов, то по истечении некоторого времени во вспомогательном регистре останется в единице только один триггер старшего по приоритету канала. После этого на вторые элементы 2 И подается второй синхроимпульс, по которому на выход устройства выдается состояние вспомогательного регистра, и старший по приоритету .запрос поступает в устройство общего пользования . Недостатком устройства приоритета является необходимость в дополнительном оборудовании для создания двух серий синхроимпульсов и сигнала установки в ноль регистра индикации и вспомогательного регистра, а также низкое быстродействие из-за потерь на выжидание окончания переходного процесса во вспомогательном регистре и на выжидание синхроимпульсов. Цель изобретения - повышение быстродействия устройства. Указанная, цель достигается тем, асинхронное приоритетное устройство, содержащее для К) каналов Vl-разрядный регистр индикации запросов и вспомогательный h-раэрядный регистр, группы элементов (п+1) И-НЕ, ВЫХОДЫ которых соединены с установочными входами соответствующих разрядов вспомогательного регистра, прямые выходы регистра индикации запросов подключены к первым входам . соответствующих элементов (п+1)И-НЕ. группы, введены элемент НЕ, эле-. мент 2 И, 2 элемента {п+1)И, а также И элементов 2 И-НЕ, выходы которых подключены к установочным входам разрядов регистра индикации запросов,первый вход каждого элемента 2 И-НЕ соединен со входом запроса устройства, инверсные вы5

ходы разрядов вспомогательного регистра подключены к первым VI входам первого элемента (п+1) И, ()-й вход которого подключен ко входу запрета устройства, выход первого элемента (п+1) И соединен с первым входом элемента 2 И и первым одом второго элемента (п+1) И, остальные 1П входы которого соединены с инверсными выходами разрядов регистра индикации запросов, входы сброса которого подключены ко входам запросов устройства, выход второго элемента (п+1) И соединен со вторыми входами элементов 2 И-НЕ группы и со входом элемента НЕ, выход которого подключен ко второму входу элемента 2 И, выход которого подключен к (i+1) входу каждого элемента (п+1) И-НЕ группы, инверсный выход каждого -го разряда регистра индикации запросов, кроме И-го, подключен к (+2)-му входу (i+)-ro элемента (п+1) И-НЕ группы, прямые выходы вспомогательного регистра являются выходами устройства.

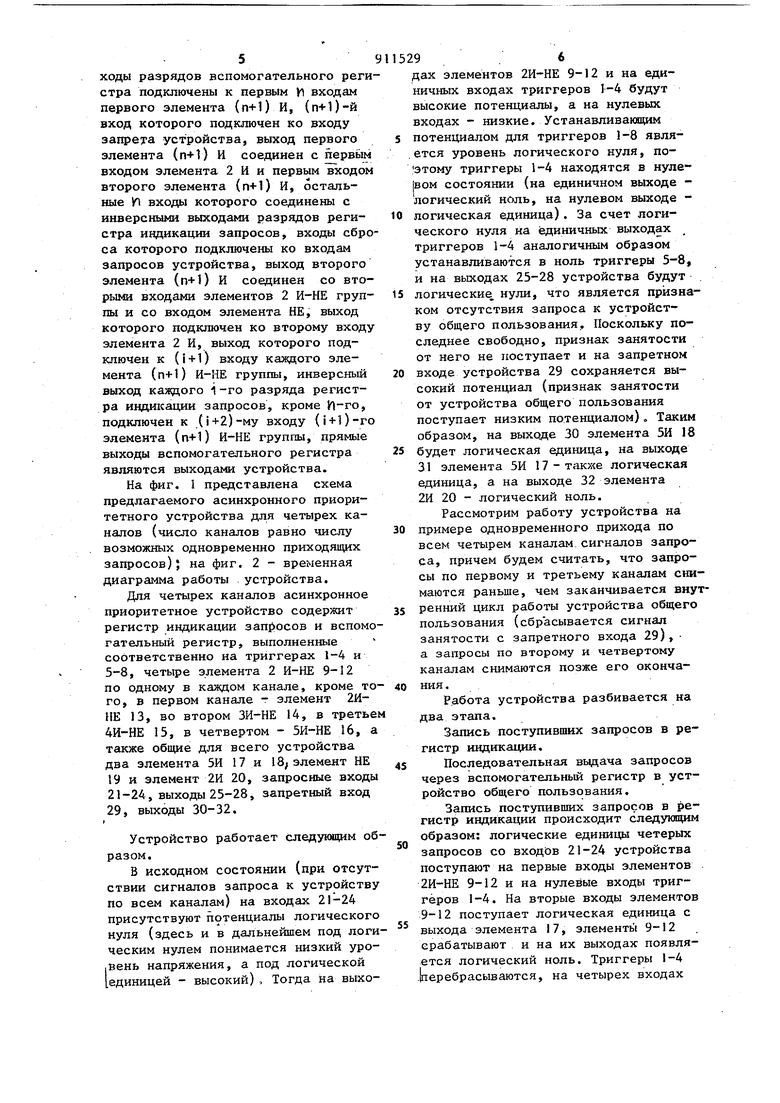

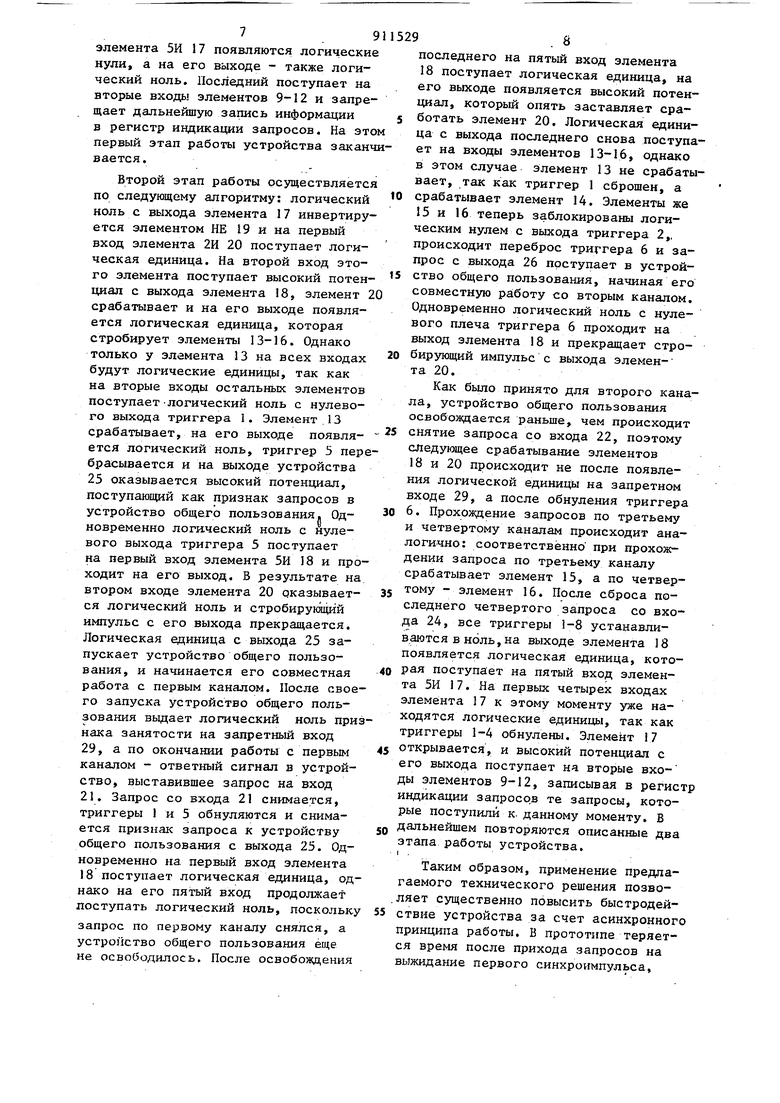

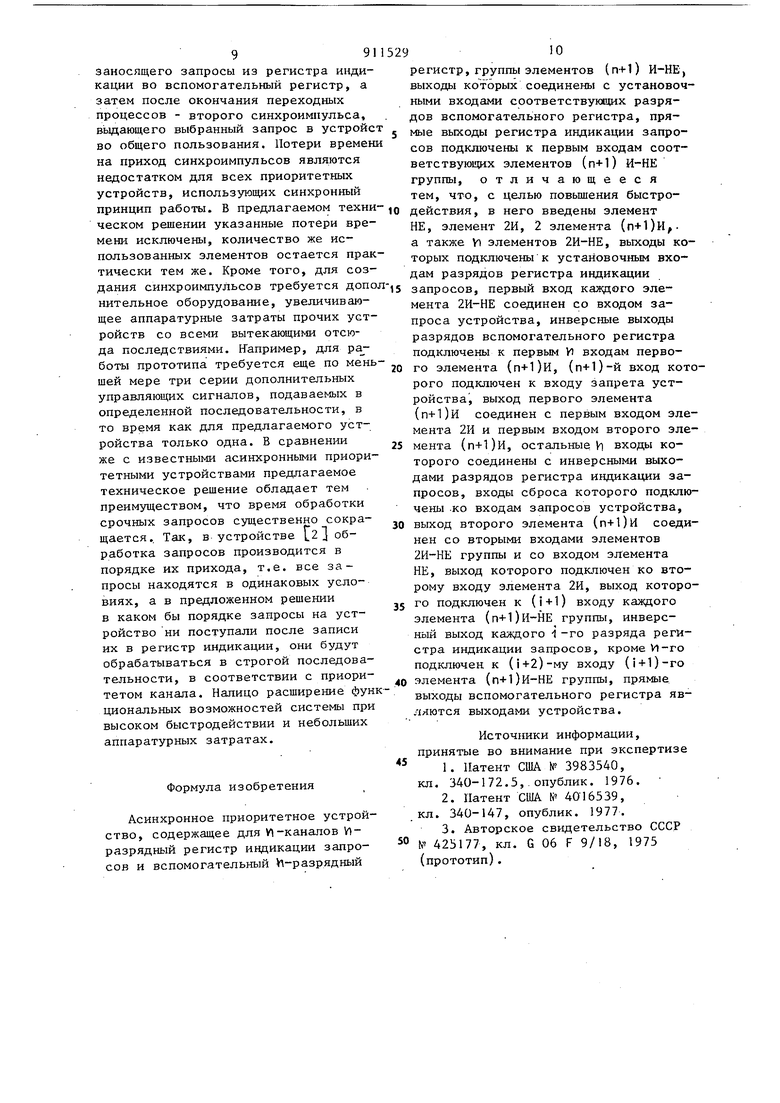

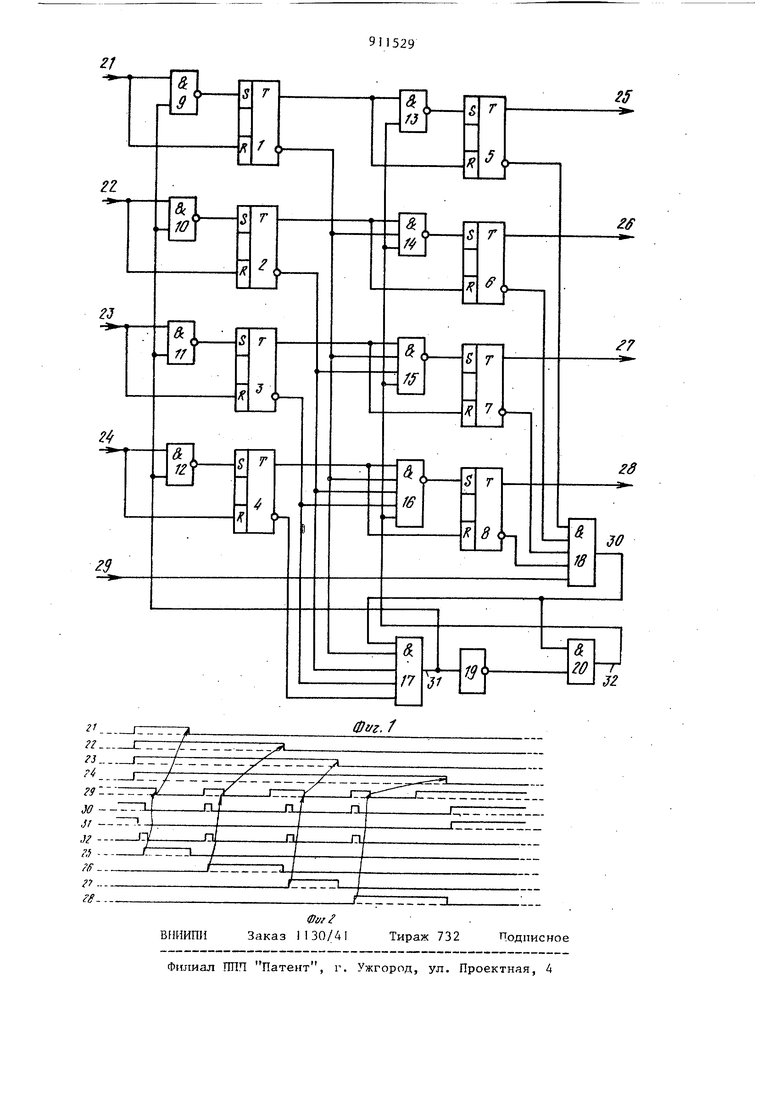

На фиг. 1 представлена схема предлагаемого асинхронного приоритетного устройства для четырех каналов (число каналов равно числу возможных одновременно приходящих запросов); на фиг. 2 - временная диаграмма работы устройства.

Для четырех каналов асинхронное приоритетное устройство содержит регистр индикации запросов и вспомогательный регистр, выполненные соответственно на триггерах 1-4 и 5-8, четыре элемента 2 И-НЕ 9-12 по одному в каждом канале, кроме того, в первом канале - элемент 2ИНЕ 13, во втором ЗИ-НЕ 14, в третье 4И-НЕ 15, в четвертом - 5И-НЕ 16, а также общие для всего устройства два элемента 5И 17 и l8 элемент НЕ 19 и элемент 2И 20, запросные входы 21-24, выходы 25-28, запретный вход 29, выходы 30-32.

t

Устройство работает следующим образом.

В исходном состоянии (при отсутствии сигналов запроса к устройству по всем каналам) на входах 21-24 присутствуют потенциаль логического нуля (здесь и в дальнейшем под логическим нулем понимается низкий уро|Вень напряжения, а под логической единицей - высокий), Тогда на выхо1529 . 6

дах элементов 2И-НЕ 9-12 и на единичных входах триггеров 1-4 будут высокие потенциалы, а на нулевых входах - низкие. Устанавливающим 5 потенциалом для триггеров 1-8 явля.ется уровень логического нуля, поэтому триггеры 1-4 находятся в нулевом состоянии (на единичном выходе логический ноль, на нулевом выходе 0 логическая единица). За счет логического нуля на единичных выходах триггеров 1-4 аналогичным образом устанавливаются в ноль триггеры 5-8, и на выходах 25-28 устройства будут

5 логические, нули, что является признаком отсутствия запроса к устройству общего пользования. Поскольку последнее свободно, признак занятости от него не поступает и на запретном

0 входе устройства 29 сохраняется высокий потенциал (признак занятости от устройства общего пользования поступает низким потенциалом), Таким образом, на выходе 30 элемента 5И 18

5 будет логическая единица, на выходе 31 элемента 5И 17-такх е логическая единица, а на выходе 32 элемента 2И 20 - логический ноль.

Рассмотрим работу устройства на

0 примере одновременного прихода по всем четырем каналам.сигналов запроса, причем будем считать, что запросы по первому и третьему каналам снимаются раньше, чем заканчивается внутренний цикл работы устройства общего пользования (сбрасывается сигнал занятости с запретного входа 29), а запросы по второму и четвертому каналам снимаются позже его оконча0 НИЯ,

Работа устройства разбивается на два этапа.

Запись поступивших запросов в регистр индикации.

5 Последовательная выдача запросов через вспомогательный регистр в устройство общего пользования.

Запись поступивших запросов в jpeгистр индикации происходит следующим

образом: логические единицы четерых

0 запросов со входов 21-24 устройства поступают на первые входы элементов 2И-НЕ 9-12 и на нулевые входы триггеров 1-4. На вторые входы элементов 9-12 поступает логическая единица с

5 выхода элемента 17, элементы 9-12 срабатывают и на их выходах появляется логический ноль. Триггеры 1-4 .перебрасываются, на четырех входах

79

элемента 5И 17 появляются логические нули, а на его выходе - также логический ноль. Последний поступает на вторые входы элементов 9-12 и запрещает дальнейшую запись информации в регистр индикации запросов. На это первый этап работы устройства заканчвается.

Второй этап работы осуществляется по следующему алгоритму: логический ноль с выхода элемента 17 инвертируется элементом НЕ 19 и на первый вход элемента 2И 20 поступает логическая единица. На второй вход этого элемента поступает высокий потенциал с выхода элемента 18, элемент 2 срабатывает и на его выходе появляется логическая единица, которая стробирует элементы 13-16. Однако только у элемента 13 на всех входах будут логические единицы, так как на вторые входы остальных элементов поступает-логический ноль с нулевого выхода триггера 1. Элемент. 13 Срабатывает, на его выходе появляется логический ноль, триггер 5 перебрасывается и на выходе устройства 25 оказывается высокий потенциал, поступающий как признак запросов в устройство общего пользования. Одновременно логический ноль с нулевого выхода триггера 5 поступает на первый вход элемента 5И 18 и проходит на его выход. В результате на втором входе элемента 20 оказывается логический ноль и стробирукщий импульс с его выхода прекращается. Логическая единица с выхода 25 запускает устройство общего пользования, и начинается его совместная работа с первым каналом. После своего запуска устройство общего пользования вьщает логический ноль признака занятости на запретный вход 29, а по окончании работы с первым каналом - ответный сигнал в устройство, выставившее запрос на вход 21. Запрос со входа 21 снимается, триггеры 1 и 5 обнуляются и снимается признак запроса к устройству общего пользования с выхода 25. Одновременно на первый вход элемента 18 поступает логическая единица, однако на его пятый вход продолжает поступать логический ноль, поскольку запрос по первому каналу снялся, а устройство общего пользования еще не освободилось. После освобоящения

последнего на пятый вход элемента 18 поступает логическая единица, на его выходе появляется высокий потенциал, который опять заставляет сработать элемент 20. Логическая единица с выхода последнего снова поступает на входы элементов 13-16, однако в этом случае элемент 13 не срабатывает, так как триггер 1 сброшен, а 0 срабатывает элемент 14. Элементы же 15 и 16 теперь заблокированы логическим нулем с выхода триггера 2,, происходит переброс триггера 6 и запрос с выхода 26 поступает в устройство общего пользования, начиная его совместную со вторым каналом. Одновременно логический ноль с нулевого плеча триггера 6 проходит на выход элемента 18 и прекращает стро0 бирующий импульс с выхода элемента 20.

Как было принято для второго канала, устройство общего пользования освобождается раньше, чем происходит 5 снятие запроса со входа 22, поэтому следующее срабатывание элементов 18 и 20 происходит не после появления логической единиць на запретном входе 29, а после обнуления триггера 0 6. Прохождение запросов по третьему и четвертому каналам происходит аналогично: соответственно при прохождении запроса по третьему каналу срабатывает элемент 15, а по четвертому - элемент 16. После сброса последнего четвертого запроса со входа 24, все триггеры 1-8 устанавливаются в ноль, на выходе элемента 18 появляется логическая единица, которая поступает на пятый вход элемента 5И 17. На первых четырех входах элемента 17 к этому моменту уже находятся логические единицы, так как триггеры 1-4 обнулены. Элемент 17 5 открывается, и высокий потенциал с его выхода поступает на вторые входы элементов 9-12, записывая в регистр индикации запросов те запросы, которые поступили к. данному моменту. В P дальнейшем повторяются описанные два

этапа работы устройства.

I .

Таким образом, применение предлагаемого технического решения позво.ляет существенно повысить быстродействие устройства за счет асинхронного принципа работы. В прототипе теряется время после прихода запросов на выжидание первого синхроимпульса. 99 заносящего запросы из регистра инди кации во вспомогательный регистр, а затем после окончания переходных процессов - второго синхроимпульса, ведающего выбранный запрос в устрой во общего пользования. Потери време на приход синхроимпульсов являются недостатком для всех приоритетных устройств, использующих синхронный принцип работы. В предлагаемом техн ческом решении указанные потери вре мени исключены, количество же использованных злементов остается пра тически тем же. Кроме того, для соз дания синхроимпульсов требуется доп нительное оборудование, увеличивающее аппаратурные затраты прочих уст ройств со всеми вытекающими отсюда последствиями. Например, для ра боты прототипа требуется еще по мен шей мере три серии дополнительных управляющих сигналов, подаваемых в определенной последовательности, в то время как для предлагаемого устройства только одна. В сравнении же с известными асинхронными приори тетными устройствами предлагаемое техническое решение обладает тем преимуществом, что время обработки срочных запросов существенно сокращается.. Так, в устройстве L2j обработка запросов производится в порядке их прихода, т.е. все запросы находятся в одинаковых условиях, а в предложенном решении в каком бы порядке запросы на устройство ни поступали после записи их в регистр индикации, они будут обрабатываться в строгой последовательности, в соответствии с приоритетом канала. Налицо расширение фун циональных возможностей системы при высоком быстродействии и небольших аппаратурных затратах. Формула изобретения Асинхронное приоритетное устройство, содержащее для VI-каналов Иразрядный регистр индикации запросов и вспомогательный Vl-разрядный 10 регистр, группы элементов (п+1) И-НЕ, выходы которых соединены с установочными входами срответствукщих разрядов вспомогательного регистра, прямые выходы регистра индикации запросов подключены к первым входам соответствующих элементов (п+1) И-НЕ группы, отличающееся тем, что, с целью повьшения быстродействия, в него введены элемент НЕ, элемент 2И, 2 элемента (п+1)И,а также У элементов 2И-НЕ, выходы которых подключены к установочным входам разрядов регистра индикации запросов, первый вход каждого элемента 2И-НЕ соединен со входом запроса устройства, инверсные выходы разрядов вспомогательного регистра подключены к первым VI входам первого элемента (п+1)И, (п+1)-и вход которого подключен к входу запрета устройства, выход первого элемента (п+1)И соединен с первым входом элемента 2И и первым входом второго элемента (п+1)И, остальные И входы которого соединены с инверсными выходами разрядов регистра индикации запросов, входы сброса которого подключены .ко входам запросов устройства, выход второго элемента (п+1)И соединен со вторыми входами элементов 2И-НЕ группы и со входом элемента НЕ, выход которого подключен ко второму входу элемента 2И, выход которого подключен к (i+l) входу каждого элемента (п+1)И-НЕ группы, инверсный выход каждого 1 -го разряда регистра индикации запросов, кроме VI-го подключен к (1+2)-му входу (i+1)-ro элемента (п+1)И-НЕ группы, прямые выходы вспомогательного регистра являются выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3983540, кл. 340-172.5,-опублик. 1976. 2.Патент США № 4046539, кл. 340-147, опублик. 1977. 3.Авторское св1щетельство СССР № 425177, кл. G 06 F 9/18, 1975 (прототип).

Авторы

Даты

1982-03-07—Публикация

1980-05-23—Подача