Изобретение относится к области вычислительной техники и может быть использовано при ироектировании цифровых вычислительных устройств с изменяемым быстродействием.

В настоящее время при проектировании цифровых вычислительных устройств стремятся обеспечить максимальную скорость переработки информации, которая определяется быстродействием элементов, условиями эксплуатации и алгоритмами преобразования. Исходи из быстродействия, выбирают временные параметры синхронизирующих (тактирующих) сигналов, которые и задают номинальное быстродействие вычислительного устройства. Так как время переработки зависит от алгоритма преобразования, то целесообразно при переходе от одного алгоритма обработки к другому иметь возможнр сть изменять параметры сипхроимпульсов.

Известны вычислительные устройства, в которых используется двойная синхронизация устройств, обеспечивающая переработку данных с различным быстродействием 1. Производится выбор одной из двух тактовых сеток в зависимости от типа выполняемой инструкции. Для этого имеется два генератора тактовых импульсов, подключаемых через коммутатор. При выполнении быстрой инструкции подключается более высокочастотный генератор, при выполнении медленной - низкочастотный.

Недостатком таких устройств является 5 ограниченный диапазон регулировки, так как можно использовать только два тактовых набора импульсов.

Более широкий набор тактирующих сигналов позволяет реализовать устройство

10 для формирования последовательности внешних сигналов р2. Устройство содержит в каждом канале счетчик времени с дешифратором, схемы И, ИЛИ и формирователь синхроимпульсов.

Недостатком данного устройства яв15ляется то, что оно не позволяет изменить параметры импульсов в процессе работы.

Наиболее полно задача перестройки параметров синхроимпульсов в процессе ра20боты решена в устройстве для формирования синхроимпульсов 3. Устройство содержит задающий генератор, блок счетчиковдешифраторов, блок фюрмирования импульсов. К входам блока счетчиков под25ключен задающий генератор, а к выходам - блок формирования импульсов.

Это устройство позволяет изменять параметры синхроимпульсов в процессе работы, однако оно не позволяет изменять 30 фазовые соотнощения, а также длительность каждого синхроимпульса одновременно независимо друг от друга.

Целью изобретения является расширение функциональных возможностей, заключающееся в возможности изменения длительности и фазовых соотношений каждого синхроимпульса независимо друг от друга, и сокраш,ение количества оборудования.

Поставленная цель достигается , что в состав устройства, содержащего задающий генератор, регистр управления и блок формирования, введены регистр сдвига, блок коммутаторов, блок выделения последнего спада и буферный регистр. Вход регистра сдвига соединен с выходом задающего генератора, а выходы - со входами блока коммутаторов, управляющие входы которого подключены к регистру управления, а выходы соединены с входам; формирователя имнульсов. Входы блока выделения последнего спада соединены с выходами устройства, а выход подключен к входу синхронизации записи регистра управления и к входу обнуления регистра сдвига. Входы буферного регнстра соединены с соответствующими входами устройства, а выходы подключены к входам регистра управления.

/Введение регистра сдвига нозволяет получить временную развертку.

Введение блока коммутаторов позволяет подключать любые пары разрядов сдвигового регистра ко входам запуска и сброса соответствующих формирователей синхроимпульсов. Это дает возможность использовать один регнстр сдвига для формирования всех синхроимпульсов, что значительно позволяет сократить количество оборудования устройства.

Раздельное управление работой каждого коммутатора в блоке коммутаторов дает возможность одновременно и независимо изменять нараметры всех синхроимпульсов.

Окончание последнего синхроимпульса является окончанием такта работы устройства, а введение блока выделения последнего спада позволяет автоматически отслеживать этот момент.

Введение буферного регистра позволяет осуществлять прием управляющей информации от ЭВМ на входы устройства в произвольный момент работы устройства.

Регистр сдвига состоит из двух регистров половинной разрядности и двух элементов ИЛИ-НЕ. Вход первого регистра половинной разрядности соединен с выходом задающего генератора, вход второго регистра половинной разрядности - с выходом носледнего разряда первого регистра половинной разрядности. Входы первого и второго регистров ноловинной разрядности подключены к входам первого и второго элементов ИЛИ-НЕ соответственно,

выходы которых подключены к входам записи единицы в первом разряде каждого из регистров половинной разрядности. Общее количество импульсов (коэффициент пересчета), которое может быть сосчитано двумя регистрамн половинной разрядности, равно (т+1)-т при условии, что количество разрядов в каждом из регистров одинпхово и равно т.

1акая организация регистра сдвига позволяет сократить общее количество разрядов, а следовательно, и количество обору/-) +1 дования по сравнению с одноре гистровой схемой, у которой коэффициент пересчета равен количеству разрядов. Наличие регистра сдвига элементов ИЛИ- НЕ связано с необходимостью восстановления еднницы в первом разряде при отсутствии ее на выходах регистра.

Блок выделения последнего спада состоит из п триггеров и я-входового элемента И-НЕ (п - число выходов устройства). Единичные входы триггеров нодключены к соответствующим выходам блока. Каждый триггер устанавливается в единичное состояние по спаду входного импульса, следовательно, в момент окончания последнего нмпульса окажется, что все триггеры установлены в единичное состояние. Этот момент фиксируется элементом И- НЕ, ко входам которого подключены выходы всех триггеров, выход элемента И-

НЕ является выходом блока и подключен к нулевым входам триггеров.

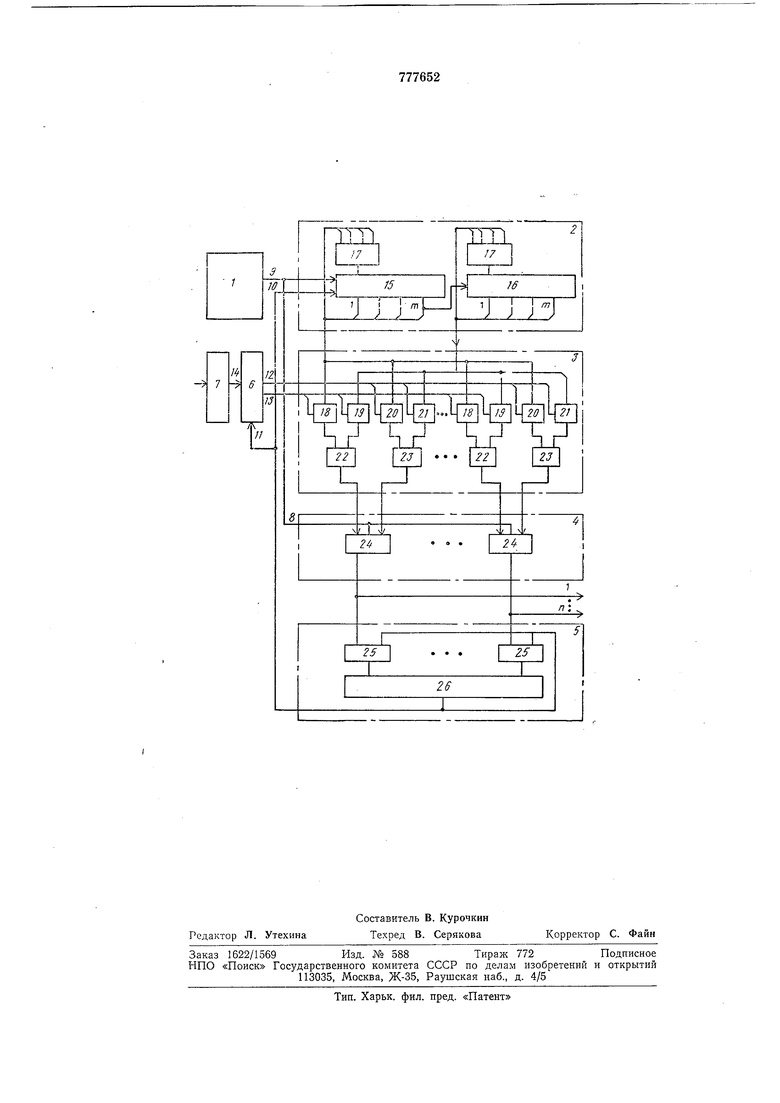

Структурная схема устройства представлена на чертеже.

Устройство состоит из задающего генератора }, регистра сдвига 2j блока коммутаторов 3, блока формирования импульсов -4, блока выделения последнего спада 5, регистра управления 6 и буферного регистра 7. Выход генератора i/ соединен с

входом синхронизации 8 блока формирова ния импульсов 4 и входом синхронизаци сдвига 9 регистра сдвига 2. Выходы последнего подключены к входам блока коммутаторов 3, выходы которого соединены с входами блока формирования 4. Вы ходы блока 4 являются выходами устройства и соединены с входами блока выделения последнего спада 5, выход которого подключен к входу обнуления (10 регнстра

сдвига 2 и входу синхронизации записи jj регистра управления 6, выходные шины 12, 13 которого нодключены к управляющим входам блока коммутаторов 3, а входная щи на }4 через регистр 7 подключена

ко входам устройства.

Регистр сдвига 2 состоит из двух т-разрядных регистров 15 и .16 и двух т-входовых элементов ИЛИ-НЕ 17. Вход регистра 15 соединен с выходом генератора /. Вход

регистра J6 соединен с выходом последнего

разряда регистра 15. Выходы всех разрядов регистров 15 и 16 подключены к входам соответствующих элементов ИЛИ-НЕ 17, выходы которых подключены к входам записи единицы в первый разряд соответствующих регистров. Выходы разрядов регистров 15 и /5 являются выходами регистра сдвига 2.

Блок коммутаторов 3 состоит из т-входовых коммутаторов dS-21 и двухвходовых элементов И 22, 23. Информационные входы коммутаторов 18, 20 соединены с выходами регистра 15, информационные входы коммутаторов 19, 21 - с выходами регистра 16, управляющие входы коммутаторов 18, ,19 и коммутаторов 20, 2J - с регистром управления 6 и шинами 12, 13 соответственно. Выходы коммутаторов 18, 19 подключены к входам элемента И 22, выходы коммутаторов 20, 21 - к входам элемента И 23, а выходы схем 22, 23 являются выходами блока 3.

Блок формирования импульсов 4 состоит из п трпггеров 24, единичные и нулевые входы которых соединены с выходами схем 22 и 23 соответственно.

Входы синхронизации записи всех триггеров 24 объединены между собой и подключены к выходу генератора 1. Выходы триггеров 24 являются выходами устройства.

Блок выделения последнего спада состоит из п триггеров i25 и я-входового элемента И 26. Единичные входы триггеров 25 соединены с выходами триггеров 24 блока 4, нулевые входы триггеров объединены между собой и подключены к выходу элемента И 36, входы которого соединены с выходами триггеров 25.

Работает устройство следующим образом.

Задающий генератор / вырабатывает прямоугольные импульсы (период следования импульсов определяет дискрет изменения временных параметров синхроимпульсов), которые поступают на вход регистра сдвига 2, на выходах которого в исходном состоянии - нули, а на выходе элемента 17 - единица. При поступлении первого импульса (по переднему фронту) единица переписывается в первый разряд регистра 15, последующие импульсы передвигают единицу по разрядам регистра 15. При постзплении (т -г 1) импульса единица записываемся в первый разряд регистра 16, 2(т + 1)-й импульс передвигает единицу во второй разряд регистра 16, 3(т + -f Г) -и - в третий разряд и т. д. Информация с разрядов регистра сдвига 2 поступает па входы блока коммутаторов 3. При этом информация с выводов регистра 15 поступает на коммутаторы 18, 20 (коммутаторы младших разрядов), а информация с регистра .16 - на коммутаторы 19, 21 (коммутаторы старших разрядов).

В соответствии с кодом, установленным па шине 13, коммутаторы J8, 19 подключают соответствующие разряды регистров 15, 16 ко входам элемента И 22. Когда поло-. жение еу1,иииц в регистрах ,/5 и 16 совпадет с установленным кодом, на выходе элемента И 22 появится положительный перепад, по которому триггер -24 переключится в единичное состояние. Сброс триггера произойдет в момент, когда положение единиц в регистрах J5, J6 совпадет с кодом, установленным на управляющих входах коммутаторов 20, 21, поскольку при этом на нулевой вход триггера 24 поступит сигнал с элемента И 23. Аналогично формируются все синхроимпульсы. Поскольку время прохождения импульсов через коммутатор п схему И в разных каналах из-за разброса временных характеристик может оказаться различным,

запись информации в триггеры 24 тактпрустся импульсами генератора 1. Это исключает случайные фазовые рассогласования между синхроимпульсами на выходе устройства и обеспечивает соответствие их

временных параметров коду, з становленному на регистре управления 6.

Концом такта работы устройства является момент окончания формирования последнего импульса илп момент сброса последнего триггера 24 в нулевое состояние. Этот момент определяется с помощью блока выделения последнего спада 5, который работает следующим образом. На входы триггеров 25 поступают импульсы с соответствующих выходов устройства. По заднему фронту (спаду) каждого из этих импульсов триггеры 25 переходят в единичное состояние.

Таким образом, по окончании последнего синхроимпульса все триггера 25 окажутся в едпиичном состоянии, а элемент PI 26 переключится из нулевого состояния в единичное. Поскольку нулевые входы триггеров 25 соедииены с выходами элемента

И 26, через время, равное сумме времени задержки выключения триггера 25 Л времени задержки выключения элемента И 26, элемент ;И 26 снова переключится в нулевое состояние. Полученный импульс (длительность которого при необходи: тост:1 может быть увеличена последовательным включением линии задержки между выходами элемента И 26 и входом трпггеров 25) поступает на вход спихронизации записи -// регистра управлеиия 6 и на вход обнуления 10 регистра сдвига 2. При этом по переднему фронту данного импульса перепишется новая кодовая информация из буферного регистра 7 в регистр управлеппя 6, а по

заднему фронту регистр сдвига 2 установится в исходное состояние, после чего пачнется формирование следующего такта работы устройства в соответствии с новым кодом, установленным в регистре управления 6,

7

Таким образом, изобретение позволяет экономично с точки зрения затрат оборудования решить задачу одновременной и исзавиеимой нерестройки параметров всех си нхрои м пул ьсов.

Формула изобретения

1. Устройство для формирования сиихроимпульсов, содержащее задающий генератор, регистр 5правления и блок формирования импульсов, отличающееся тем, что, с целью расширения функциональных возможностей, заключающегося в возможности изменения длительности и фазовых соотнощений каждого синхроимпульса независимо друг от друга, и сокращения количества оборудования, в него введены регистр сдвига, блок коммутаторов, блок выделения последнего снада и буферный регистр, нри этом выход задающего генератора подключен к входу синхронизации блока формирования импзльсов и к входу сдвигового регистра, выходы которого соединены со входами блока коммутаторов, выходы последнего подключены к входам блока формирования синхроимпульсов, выходы блока формирования синхроимпульсов являются выходами устройства и подключены к входам блока выделения последнего спада, выход которого соединен с входом обнуления регистра сдвига и с входом синхронизации записи регистра управления, выход которого подключен к управляющим входам блока коммутаторов, а входы через

8

буферный регистр соединены со входами устройства.

2.Устройство поп. 1, отличающеес я тем, что регистр сдвига состоит из

половинной разрядности регистров и двух эле.мептов Р1ЛИ-НЕ, причем вход первого регистра половинной разрядности соединен с выходом задающего генератора, вход второго регистра половинной разрядности соединен с выходом последнего разряда первого регистра половинной разрядности, выходы первого н второго регистра половинной разрядности подключены к входам соответствующих элементов Р1ЛИ-НЕ, выходы которых соединены с входами 3aniiCH единицы в первый разряд соответствующих регистров половинной разрядности.

3.Устройство по п. 1, отличающееся тем, что блок выделения поеледнего спада содержит п триггеров (где п - число выходов устройства) ил - входовые элементы И-НЕ, причем едииичные входы триггеров соединены соответствующими входами блока выделения последнего спада, а выходы - со входами элемента И-НЕ, выход которого подключен к нулевым входам триггеров и является выходом блока.

Источники информации, принятые во внимание при экспертизе:

1. Натент США № 3623017, кл. G 06 F 9/0-0, 1971.

2. Авторское свидетельство СССР № 525075, кл. G 06 Е 1/04, 1975.

,3. Авторское свидетельство СССР

№ 653614, кл. G06 Е 9/00, 1976 (нрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1981 |

|

SU964616A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840556A2 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для обмена информацией | 1989 |

|

SU1695316A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

Авторы

Даты

1980-11-07—Публикация

1979-01-10—Подача