Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах передачи и переработки информации и контроля цифровой аппаратуры.

Цель изобретения - повьппение удобства эксплуатации формирователя.

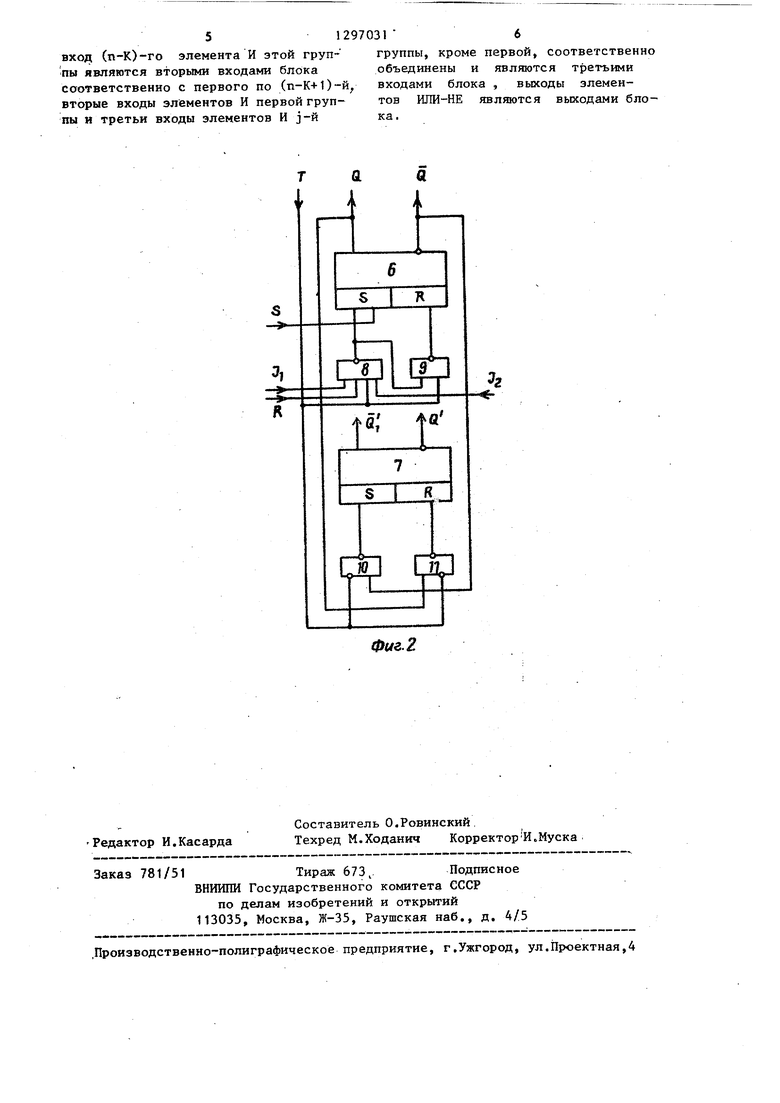

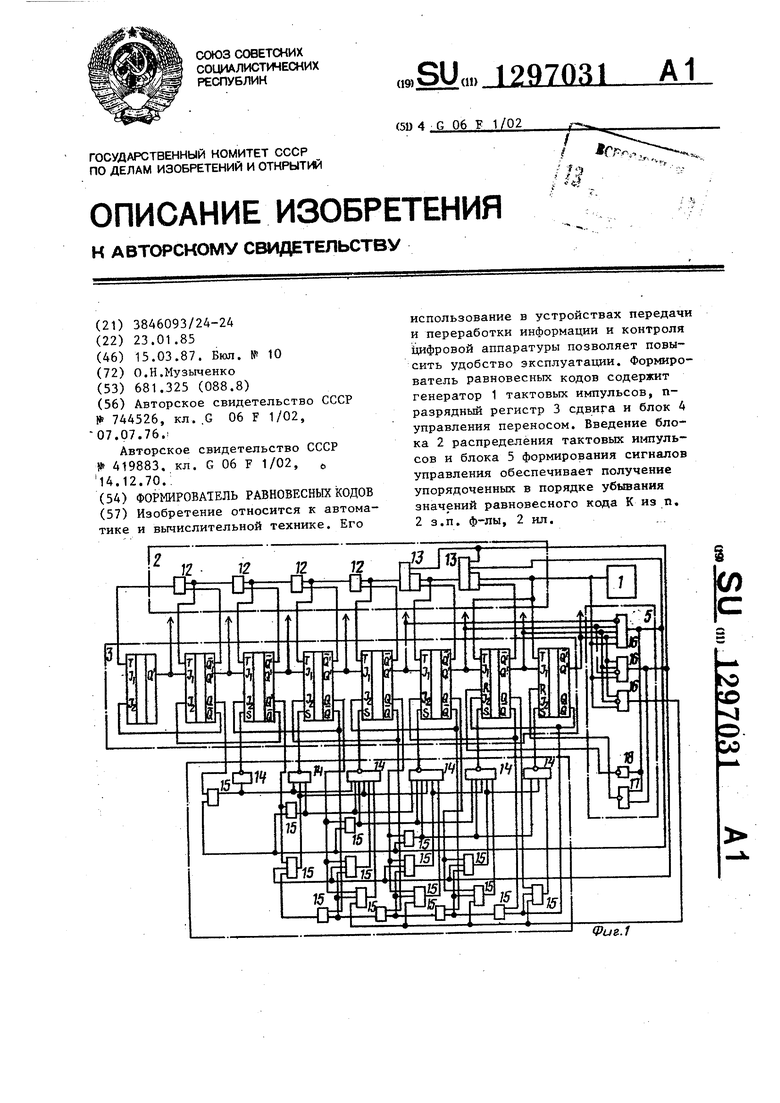

На фиг.1 приведена функциональная схема формирователя; на фиг.2 - принципиальная схема разряда п-разрядного регистра сдвига.

Формирователь равновесных кодов содержит генератор 1 тактовых импульсов, блок 2 распределения тактовых импульсов, п-разрядный регистр 3 сдвига, блок 4 управления переносом и блок 5 формирования сигналов управления. Каждый разряд п разрядного регистра 3 сдвига (фиг.2) выполнен на триггерах 6 и 7 и элементах И-НЕ 8-11.

Блок 2 распределения тактовых импульсов служит для поочередной подачи тактовых импульсов на соответствующий тактовый вход регистра 3 и может быть вьтолнен на п-К элементах И 12 и К-2 элементах И-ИЛИ 13, где К - вес формируемого кода.

Блок 4 управления переносом включает в себя п-2 элементов ИЛИ-НЕ 14 и К групп по п-К элементов И-НЕ 15, Последние входы элементов Й-НЕ 15 всех групп, кроме последней, - импульсные .

Блок 5 формирования сигналов управления может быть выполнен на К-1 элементах И 16, К-3 элементах ИЛИ-НЕ 17 и элементе НЕ 18.

Работа формирователя равновесного кода К из п происходит следующим образом.

В исходном состоянии разряды 3-1 - 3-К регистра 3 находятся в единичном состоянии, остальные разряды 3 - К+1 3-п - в нулевом состоянии.

При этом единичные потенциалы имеются на выходах Q и Q разрядов 3-1 - 3-К и на выходах Q и Q разрядов 3-(К+1) - 3-п. По мере поступления тактовых импульсов от генератора 1 они проходят через блок 2 распределения тактовых импульсов только на входы разрядов 3-п - З-Р , где Р, - номер крайнего правого разряда,

который находится в единичном состоя

НИИ. При этом каждый раз крайняя правая единица перемещается на 1 разряд вправо. Когда в единичном состоянии оказывается разряд 3-п, блок 2 про

5

0

5

0

(пускает очередной тактовый импульс на входы разрядов 3-п - -Р j где Р - номер крайнего правого из оставшихся (не считая разряда 3-п) разряда, который находится в единичном состоянии. При этом разряды 3-п и 3-Pj обнуляются, а в единичное состо-- ян,ие переходит разряд 3-(Р, +1). Одновременно на соответствующем выходе блока 5 формируется сигнал переноса, который через блок 4 поступает на вход S разряда 3-(Р2+2), устанавливая его в единичное состояние в момент окончания сигнала на выходе блока 5 (по окончании тактового импульса) ..

Далее по мере поступления тактовых импульсов опять производится сдвиг вправо крайней правой единицы.

Когда на некотором такте работы формирователя в единичном состоянии оказьшаются t крайних правых разрядов 3-п - 3-(n-t+1) регистра 3, а разряд 3-(n-t) - в нулевом состоянии, то при поступлении очередного тактового импульса на t-м выходе блока 5 появляется импульс, поступающий через блок 2 тактовых импульсов на входы разрядов 3-п - З-PI регистра 3, где, Р, - номер крайнего правого разряда

e

0

регистра 3, в который записана единица (не считая разрядов З-п - 3-(n-t+1) . При этом разряды 3-Pt иЗ-() устанавливаются в нулевое состояние, а 5 разряды 3-() - в единичное. Одновременно сигнал с блока 5 проходит на входы сброса разрядов 3-п - 3- -(n-t+2) регистра 3, устанавливая их в нулевое состояние.

Кроме того, указанный сигнал через блок 4 поступает на установочные входы S разрядов 3-(Р+2) - 3- -(Р +t+1) регистра 3, устанавливая их в единичное состояние (в момент окончания сигнала на t-м выходе бло- ка 5) .

Таким образом, на выходах Q разрядов регистра 3 сдвига последовательно появляются слова кода К из п от 1.,10..0 до 0..01..1.

При появлении единичных потенциалов на выходах последних К разрядов регистра 3 работа устройства прекращается.

Таким образом, формирователь обеспечивает сформирование равновесного кода К из п, упорядоченного в порядке убывания двоичных кодов.

5

0

Формула изобретения

1. Формирователь равновесных кодов, содержащий п-разрядный регистр сдвига, генер-атор тактовых импульсов и блок управления переносом, отличающийся тем, что, с целью

2. Формирователь по п.1, о т л и чающийся тем, что каждый разряд п-разрядного регистра сдвига включает в себя два-триггера и четы ре элемента И-НЕ, выход первого эле мента И-НЕ соединен с первым входом установки в единицу первого триггеповьшения удобства эксплуатации формирователя, в него введены блок формирования сигналов управления и блок О ра и первым входом второго элемента распределения тактовых импульсов, вы- И-НЕ, выход которого подключен к

ходы которого соединены с тактовыми входами соответствующих разрядов п- разрядного регистра сдвига, первый прямой выход каждого из которых явля - ется соответствующим выходом формирователя и подключен, кроме последнего,к первому информационному входу следующего разряда, первые прямые выходы последних К разрядов п-разрядного 20 регистра сдвига, где К - вес формируемого кода, соединены с первыми входами блока формирования сигналов управления, первые инверсные выходы

входу установки в нуль первого триггера, инверсный и прямой выходы которого соединены с разрешающими 15 входами соответственно третьего и четвертого элементов И-НЕ, выходы которых подключены к входам установки соответственно в единицу и в нуль второго триггера, первый вход первого элемента И-НЕ является входом установки в нуль разряда, вторые входы первого и второго и запрещающие входы третьего и четвертого элементов И-НЕ объединены и являются

разрядов п-раэрядного регистра сдвига тактовым входом разряда, третий и с второго по (п-1)-й подключены к четвертый входы первого элемента

И-НЕ являются соответственно первым и вторым информационными входами

разряда, второй вход установки в

первым входам блока распределения

тактовых импульсов, второй инверсный

выход каждого разряда п-разрядного

регистра сдвига, кроме первого, сое- - единицу первого триггера является

динен с вторым информационным входом входом установки в единицу разряда,

инверсный и прямой выходы второго триггера являются первыми соответстпредыдущего разряда, вторые прямые выходы разрядов п-разрядного регистра сдвига с второго по (п-1)-й подключены к входам первой группы блока 35 разряда, прямой и инверсный выходы управления переносом соответственно первого триггера являются вторыми с первого по (п-2)-й, вторые инверсные выходы разрядов п-разрядного регистра сдвига с (К-1)-го по п-й соевенно прямым и инверсным выходами

соответственно прямым и инверсным выходами разряда,

3. Формирователь поп.1, отл и-

динены с входами второй группы блока чающийся тем, что блок управления переносом выполнен на п-2 элементах ИЛИ-НЕ и К группах по п-К элементов И, выход i-ro элемента И j-й группы, 1еГ1,п-К, ,K-1,

управления переносом соответственно с первого по (п-К+1)-й, выходы блока управления переносом с первого по (п-2)-й подключены к входам установки в единицу разрядов п-разрядного регистра сдвига соответственно с третьего по п-й, выход генератора так- товьрс импульсов подключен к вторым входам блока распределения тактовых импульсов и блока формирования сигналов управления, первые выходы которого подключены к входам установки в нуль разрядов п-разрядного регистра сдвига с (п-К+3)-го по п-й.

равления переносом выполнен на п-2 элементах ИЛИ-НЕ и К группах по п-К элементов И, выход i-ro элемента И j-й группы, 1еГ1,п-К, ,K-1,

45 подключен к j-м входам элементов ИЛИ-НЕ с i-ro по (i+K-j)-A, выход .i-ro элемента И К-й группы подключен к первому входу (i-l)-ro элемента И этой группы и первому входу (i-j+

50 +К-1)-го элемента И j-й группы, кроме первой, первые входы (п-К)-х элементов И (К-1)-й и К-й групп объеди нены, первый вход i-ro элемента И первой группы объединен с вторым

вторые выходы блока формирования сиг- входом (i-j+1)-ro элемента И j-й

налов управления соединены ссоответ- группы, кроме первой, и является

ствующими третьими входами блокаi-м первым входом блока, вторые вхс

распределения тактовых импульсов иды элементов И К-й группы и первый

входами третьей группы блока .управления переносом.

2. Формирователь по п.1, о т л и- чающийся тем, что каждый разряд п-разрядного регистра сдвига включает в себя два-триггера и четыре элемента И-НЕ, выход первого элемента И-НЕ соединен с первым входом установки в единицу первого триггера и первым входом второго элемента И-НЕ, выход которого подключен к

входу установки в нуль первого триггера, инверсный и прямой выходы которого соединены с разрешающими входами соответственно третьего и четвертого элементов И-НЕ, выходы которых подключены к входам установки соответственно в единицу и в нуль второго триггера, первый вход первого элемента И-НЕ является входом установки в нуль разряда, вторые входы первого и второго и запрещающие входы третьего и четвертого элементов И-НЕ объединены и являются

разряда, второй вход установки в

разряда, прямой и инверсный выходы первого триггера являются вторыми

венно прямым и инверсным выходами

разряда, прямой и инверсный выходы первого триггера являются вторыми

соответственно прямым и инверсным выходами разряда,

3. Формирователь поп.1, отл и-

чающийся тем, что блок управления переносом выполнен на п-2 элементах ИЛИ-НЕ и К группах по п-К элементов И, выход i-ro элемента И j-й группы, 1еГ1,п-К, ,K-1,

подключен к j-м входам элементов ИЛИ-НЕ с i-ro по (i+K-j)-A, выход .i-ro элемента И К-й группы подключен к первому входу (i-l)-ro элемента И этой группы и первому входу (i-j+

+К-1)-го элемента И j-й группы, кроме первой, первые входы (п-К)-х элементов И (К-1)-й и К-й групп объеди нены, первый вход i-ro элемента И первой группы объединен с вторым

вход (п-К)-го элемента И этой группы являются вторыми входами блока соответственно с первого по (п-К+1)-й вторые входы элементов И первой группы и третьи входы элементов И j-й

группы, кроме первой, соответственно объединены и являются третьими входами блока ,, выходы элементов ИЛИ-НЕ являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для упорядочивания чисел | 1984 |

|

SU1241228A1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1319043A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для суммирования @ -разрядных последовательно поступающих чисел | 1982 |

|

SU1075260A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в устройствах передачи и переработки информации и контроля Ьщфровой аппаратуры позволяет повысить удобство эксплуатации. Формирователь равновесных кодов содержит генератор 1 тактовых импульсов, п- разрядный регистр 3 сдвига и блок 4 управления переносом. Введение блока 2 распределения тактовых импульсов и блока 5 формирования сигналов управления обеспечивает получение упорядоченных в порядке убывания значений равновесного кода К из п, 2 з.п. ф-лы, 2 ил. (Л 0)иг.1

Редактор И.Касарда

Составитель О.Ровинский

Техред М.Ходанич Корректор И. My ска

Заказ 781/51Тираж 673, Подписное

ВНИИПИ Государственного комитета СССР

по делам иэобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Фиг. 2

Авторы

Даты

1987-03-15—Публикация

1985-01-23—Подача