Изобретение относится к технике измерения статистических характеристик случайных процессов и предназначено для определения дисперсии ординат центрированных случайных процессов.

Известно устройство для определения дисперсии, содержащее преобразователь аналогкод, вычитающий счетчик и накопитель, недостатком которого является сложность цифрового устройства и узкий спектр анализируемых частот.

Целью предлагаемого устройства является упрощение цифрового устройства дисперсии и раощирение спектра анализируемых им частот случайных центрированных процессов.

Поставленная цель достигается тем, что в состав устройства вводятся триггер, схемы совпадения и сборки. Информационный выход преобразователя через первую схему совпадения, управляющим входом подключенную к единичному выходу триггера, связан с вычитающим входом счетчика и входом установки единицы триггера, а через вторую схему совпадения, управляющцм входом подключенную к нулевому выходу тр.иггера и к управляющему входу третьей схемы со впадения, через первую и вторую схемы сборки соответственно - с щиной опроса инверсного кода счетчика п с входом перВого разряда накопителя, а также с входом установки нуля триггера. Знаковый выход преобразователя подключен ко второму управляющему входу третьей схемы совпадения, импульсный вход которой связан со входом элемента задержки, вторым входом второй схемы сборки и выходом цризнака конца преобразования преобразователя аналог-код. Выход элемента задерл ки связан

с шиной сброса счетчика (поразрядные выходы последнего, начиная с младщего разряда, связаны соответственно со входами накопителя, начиная со второго по к-ый).

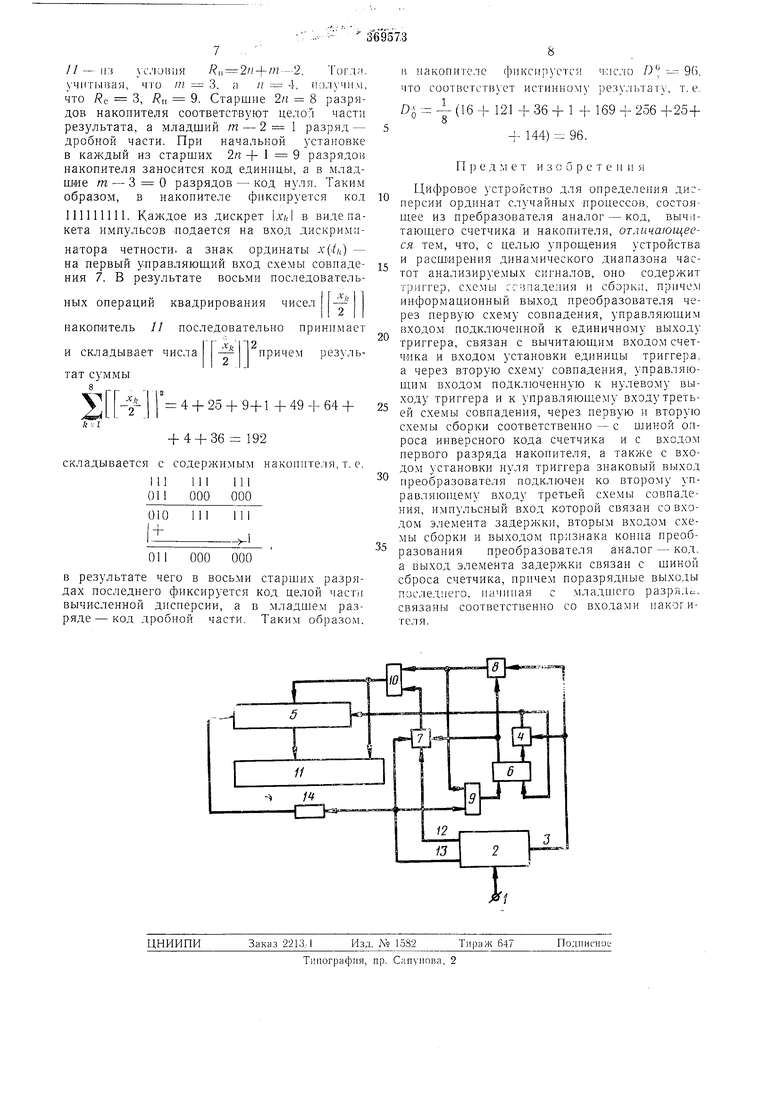

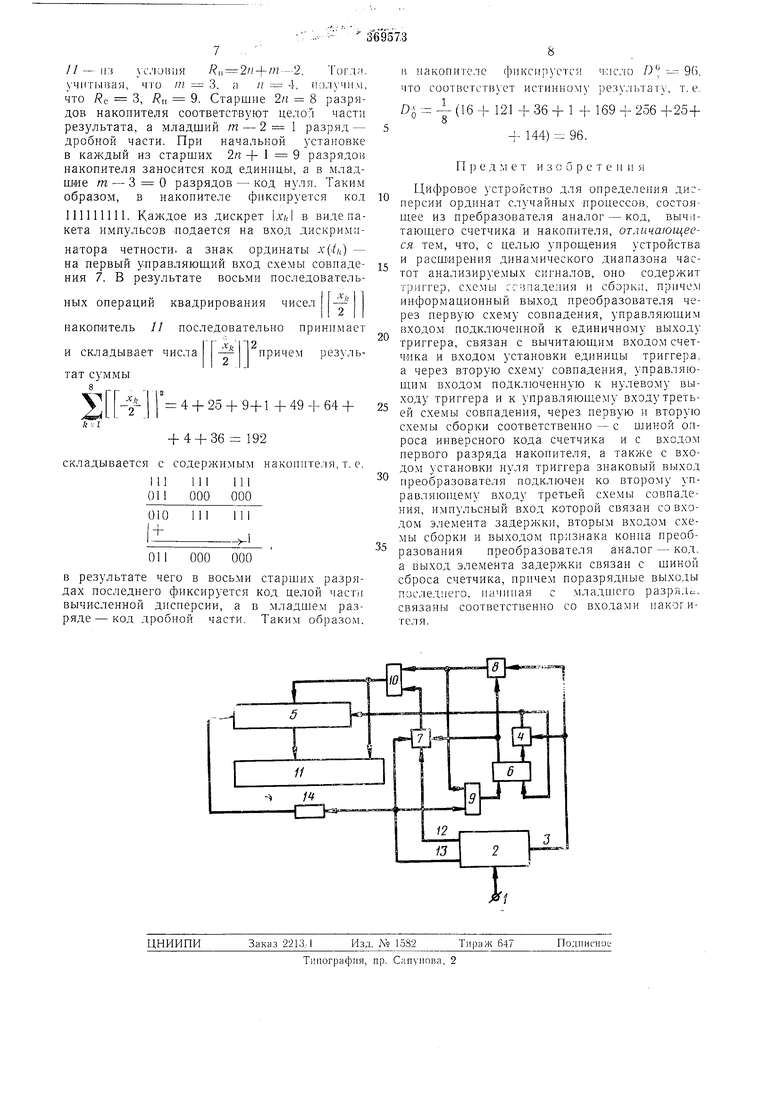

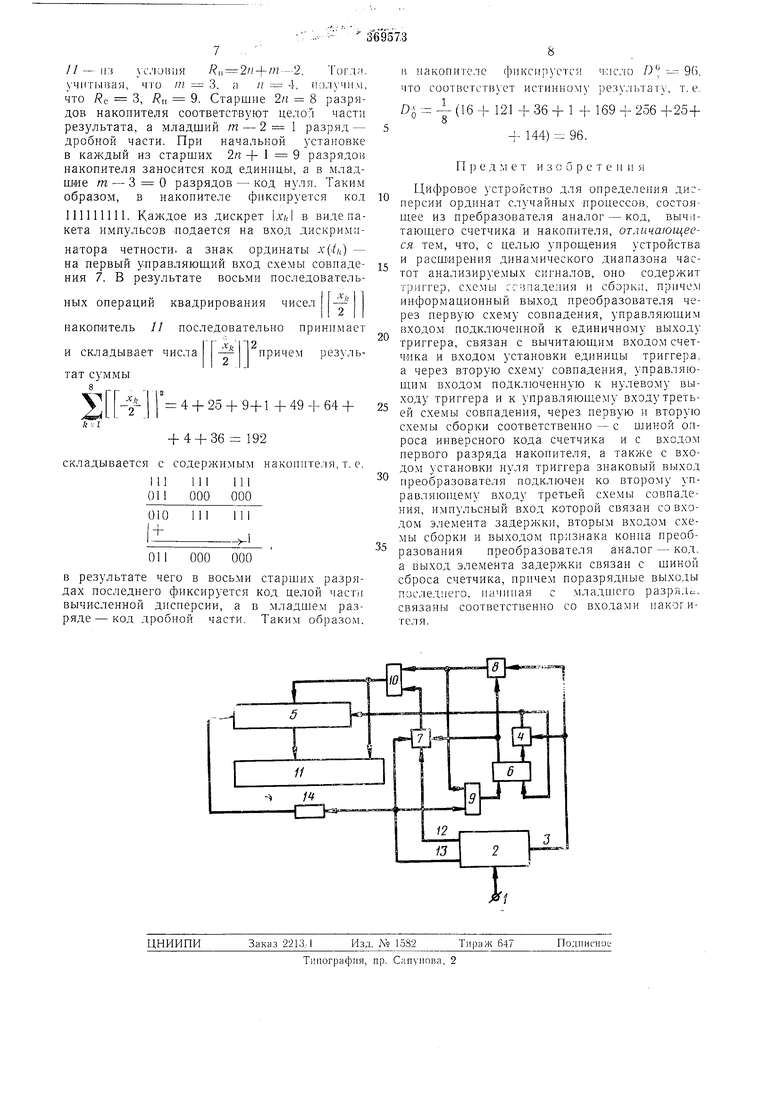

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содерл ит входную клемму /, преобразователь 2 аналог-код, информационный выход 3 преобразователя, схему совпадения 4, вычитающий счетчик 5, триггер 6, схемы

совпадения 7 и 8, схемы сборки 9 и 10, накопитель //, знаковый выход 12 преобразователя, выход 13 «конец преобразований и элемент задержки 14.

Преобразователь 2 типа аналог-код производит время-импульсное преобразование .исследуемого процесса xt, подаваемого на клемму / в виде аналогового сигнала. Разрядность вычитающего двоичного счетчика 5 равна (л,-1). В (2/г-2+т) разрядном накопителе // Б качестве младших /г разрядов используется сумматор со сквозным nepeiiOCOiM, а в качестве старших (п-2 + т) разряло - обычный двоичный счетчик, иричем выход последнего связан с входом (т - 2)-го разряда накопителя. Информационный выход 3 преобразователя 2 подключен к импульсным входам схем совпадения 4 и 8, выход первой из которых подключен к счетному входу счетчика 5 и к единичному входу триггера 6. Выход схемы совпадения S через схемы сборки 9 и 10 связан соответственно с нулевым входом триггера 6, а также с шиной опроса инверсного кода счетчика 5 и входом младшего разряда накопителя 11. Выход J2 преобразователя 2 связан с первым упраБляюш,им входом схемы совпадения 7, второй управляющий вход которой .подключен к управляющему входу схемы совпадения 8 и к нулевому выходу триггера 6, единичный .выход которого связан с управляюЩИм входом -схемы совпадения 4. Выход 13 преобразователя 2 связан с импульсным входом схемы совпадения 7 и со вторым входом схемы сборки 9 непосредственно, а через элемент задержки 14 - с шиной сброса счетчика 5. Выход схемы совпадения 7 подключен ко BTOipoMy входу схемы сборки 10. Длительность элемента задержки 14 равна т -, где / - рабочая частота используемого в устройстве логического комплекса элементов. Поразрядный перенос инверсного кода числа из счетчика 5 в Н1акопитель J осуществляется по цепям, образованым за счет подключения выходов счетчика 5 (начиная с первого по (п-1)-й разряд) к соответствующим входам (начиная со второго по «-и) младших раарядов накопителя 11 (цепи начальных установок на схеме не показаны). Перед началом анализа в накопителе 11 устанавливается двоичный код числа посредством установки (2/г-(-1) старших разрядов накопителя 11 в единичное положение, а (т - 3) младших разрядов - в нулевое положение. Счетчик 5 И триггер 6 находятся в положении нуля, схема совпадения 4 открыта, а схемы совпадения 7и S закрыты. Известный цифровой алгоритм определения диспресии центрированных процессов имеет вид D N ft l где Хй - текущая дискрета ординаты K(ti,} не- 55 следуемого процесса х(/); yV - объем выборки. Учитывая, что появление четных и нечетных дискрет равновероятна, т. е. количество четных А-{ И нечетных A-J дискрет в полной выборке V Л одинаково и равно -, то, сгруппировав четные и нечетные дискреты, выражение (1) переписывается в виде - гд на (2 ш 45 ри в му пу с ие не ф 60 в ва со ни 65 ну , Л U- .. е сумма по переменной i распространяется все четные, а / - та нечетные дискреты. Введя обозначения л; А;+1 выражение ) преобразуется к виду ,()1Знак означает окружение до меньего целого с учетом знака. Итак D- --- N В устройстве реализуется цифровой алготм вида (3), иричем принимается л-)41макс 2 Устройство работает следующим образом. Исследуемый центрированный нроцесс x(t) виде аналогового сигнала подается на клем/. Преобразователь 2 производит время-имльсное преобразование аналогового представлением ординат x(i) в в,иде сооттствующих пакетов импульсов Xh, которое зависимо от полярности входного сигнала рмируются на .информационном выходе 3. В процессе преобразования ординаты x(tk} пакет импульсов Xk с выхода 12 преобразотеля 2 на первый управляющий вход схемы впадения 7 подается напряжение кода едицы, если x(th) О, или напряжение кода ля, если x(th) 0. Это напряжение поддерживается в течение времеп.н каждого предетавления пакета импульсов Xk и синмаегся после око;нчания импульса конца пакета, который формируется на выходе 13 преобразователя 2 через время т - (где / - частота импульсов в пакете) после последнего импульса пакета х.

Рассмотрим k-ъш цикл работы устройства. Пусть перед началом k-ro преобразования

с

ординаты x(tk) в накопителе /У зафиксирован двоичный код разности сумд1ы квадратов дисза первые (k- 1) преобразований

крет и числа т. е. двоичный код разности В счетчике 5 зафиксирован код нуля, триггер 6 находится в положении нуля. В процессе k-ro преобразования ординаты x(tk) каждый нечетный импульс пакета х,,, пройдя через схему совпадения 4, поступает на счетный вход счетчика 5 и на единичный вход триггера 6. При этом каждый раз производится выч.итание единицы из содержимого счетчика 5 и уста1нозка единицы триггера 6, в результате чего схема совпадения 4 закрывается, а схема совпадения S открывается. Каждый четный импульс пакета производит перенос инверсного кода из счетчика 5 в накопитель // с посылкой единицы на вход его младшего разряда, а также установку триггера 6 в положение нуля, в результате чего схема совпадения 8 закрывается, а схема совпадения 4 открывается. Если преобразоваипая ордината x(tk) представилась четным числом импульсов х, то Т;риггер 6 будет находиться в положении нуля. При этом на втором управляющем входе схемы совпадения 7 напряжение кода единицы отсутствует, и последняя закрыта, независимо от того, было ли л-(//,.)0 или л-(4)0, поэтому имиульс конца пачки Xk, сформированный на выходе 13 преобразователя 2, не пройдет ва выход схемы совпадения 7. На выход последней импульс не поступит и в случае, когда V(/;i);0 и Xh четно. В случае же, когда л;(//г)0 и Xh нечетно, импульс конца пакета, пройдя через схемы совпадения 7 и сборки W, произведет перепись инверсного кода числа из счетчика 5 в накопитель // с за,носом единицы в нервый разряд накопителя. Импульс коица пачки, пройдя через схему сборки 9, произведет установку триггера 6 в положение нуля, а через элемент задержки М - сброс счетчика 5. Ввиду того, что последний собран по схеме вычитания. 1мпульс сброса не вызывает последовательного переноса единицы из предыдущего разряда (если указанный разряд находился в единичном положении) в последующий, поэтому для сброса после,диего достаточно одного «короткого нмпульса.

Спустя время 3т после окончагмя представления пакета л/; независимо от его четнюстл

и знака соответствующей ему ординаты x{ti,) все переходные процессы в счетчике 5 и в накопителе // завершаются, и возможна подача команды на очередное (А+1)-ое преобразование ординаты x(tii+i). С завершением переходных процессов после k-ro преобразования в накопителе // фиксируется двоичный код числа -f I I I I 9 -3 I т II - - С набором полной выборки ;V 2 в накопителе // фиксируется двоичный код числа причем в старших 2 находится целая часть D , ft-i а в (т - 2) младших разрядах-дробная часть указанного числа. Процесс квадрирования дискрет - люстрируется примерами и А-(/А.)0, тогда первый, третий, пятый и седьмой импульсы пакета устанавливают в счетчике 5 соответственно коды 1...ПК I....110, 1....101, 1....100, а второй, четвертый, шестой и восьмой импульсы производят последовательный занос кодов 0...0001. 0...0011, 0...0101, O...OI11 Б накопитель, т. е. в накопитель посылается число 0...010000 Если хл- 9 и .v(/;()0, то девятый )1мпульс устанавливает в счетчике 5 код 1...10П, а импульс конца иачки производит дополнительный занос кода 0...01001 в накопитель. Рассмотрим на конкретном примере процесс вычисления диспрессии. Пусть N 2 8, |л-маис1 2 16, дискреты Xk исследуемого процесса x(t) соответственно равны -4, 11, 6, -1, -13, -16, 5, 12, причем X 0. Разрядность счетчика 5 выбиваем из УСЛОВИЯ Rc . а накопителя

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР | 1972 |

|

SU337784A1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU387370A1 |

| СПОСОБ ФОРМИРОВАНИЯ ИНФОРМАЦИОННОГО ПОЛЯ ЛАЗЕРНОЙ СИСТЕМЫ ТЕЛЕОРИЕНТАЦИИ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2080615C1 |

| Устройство для ввода информации | 1974 |

|

SU516032A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ В ДВОИЧНЫЙ КОД | 1969 |

|

SU253458A1 |

| Многоканальный преобразователь кода во временной интервал | 1972 |

|

SU484638A1 |

| Коррелятор | 1984 |

|

SU1180927A1 |

| Преобразователь интервала времени в цифровой код | 1976 |

|

SU636640A2 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

Даты

1973-01-01—Публикация