1

Устройство относится к области автоматики л вычислительной техники и может быть использовано при реализации технических средств цифровой автоматики и специализированных электронных вычислительных машии.

Известны устройства для вычитания чисел, представленных кодами с произвольными основаниями, содержащие два сумматора и логические схемы. Реализация вычитания заменяется сложением уменьшаемото с дополнительным кодом вычитаемого. Первый из сумматоров служит для сложения операндов и переноса, а с -помощью второго осуществляется введение корректирующего кода. Однако реализация с помощью этих устройств непосредств-еппого вычитания чисел, представленных комбинированными кодами при двоич,ном кодировании чисел В труопах, особенно с разнородными основаниями, затруднительна, так как получение допол,нения вычитаемого в этом случае трудоемко.

Предлагаемое устройство отличается от известных тем, что в цепь -переноса первого сум.матора введена схема «ИЛИ, другим входом связанная с шиной одиночного имяульса, а выходом соединенная со входом схемы задержки; выход переноса первого сумматора через схему «И, связанную другим выходом с одной из шин опорных импульсов, соединен с входом ключа, два других входа которого

связаны с щи;нои двоичных кодов основания счета в группах и другой шиной опорных импульсов, а выход ключа соединен со вторым входом второго сумматора. Выход переноса сумматора через лоследователь-но соединенные схему « Ьапрета, схему задержки и схему «ИЛИ связан с его третьим входом, а вторые входы схем «ИЛИ и «Запрета соединены с шинами изменения знака и второй шииой опориых импульсов соответственно. Это обеспечивает возможность непосредственного вычитания чисел, лредставленных ком бинированными кодами при двоичном кодировании чисел В группах и произвольным числом разрядов в них.

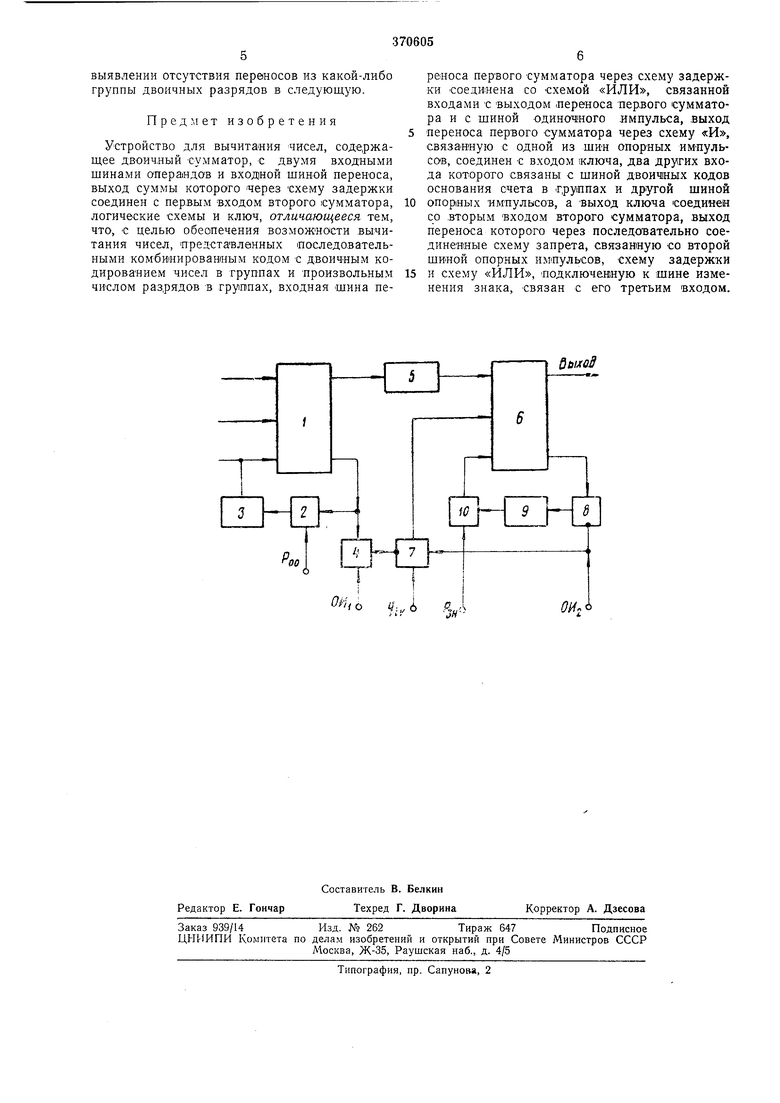

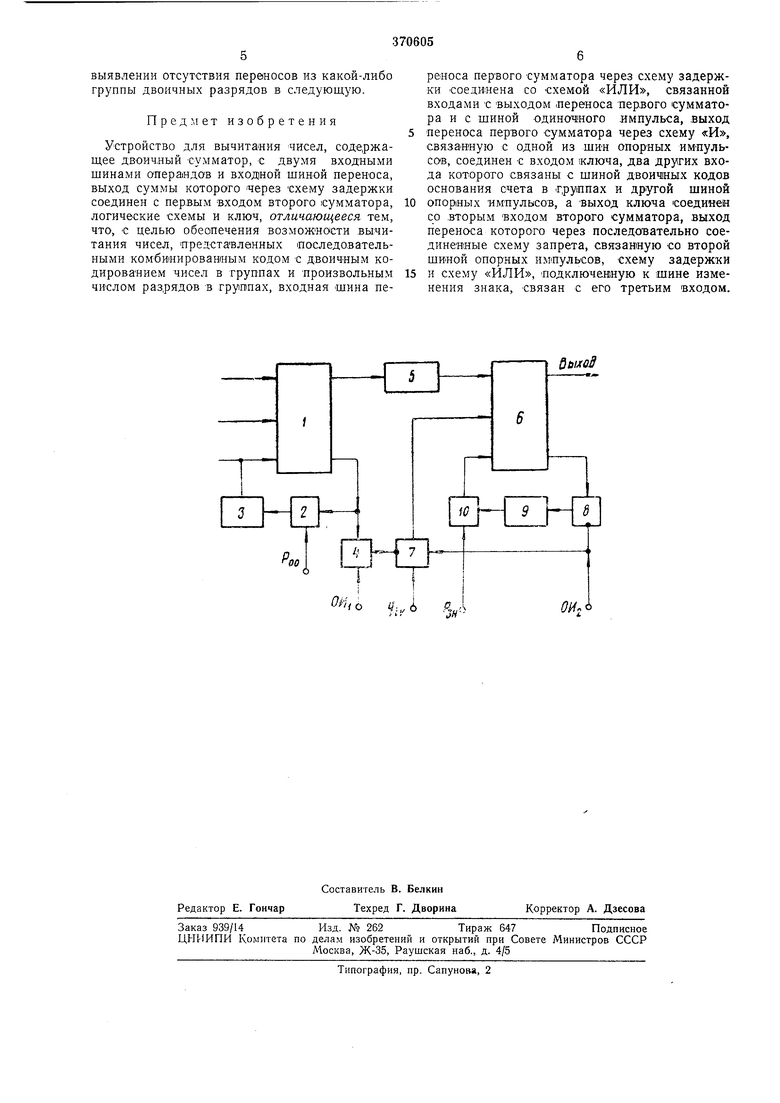

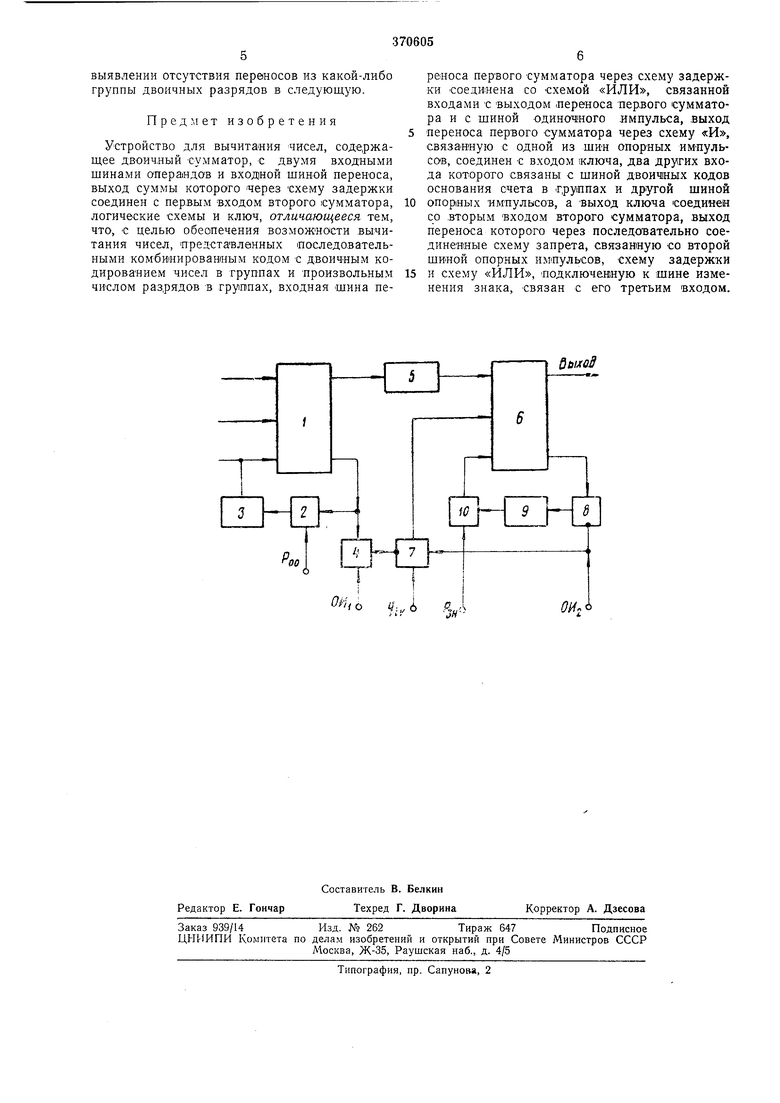

На чертеже цриведена блок-схема предлагаемого устройства.

Устройство содержит одноразрядный двоичный сумматор 1, выход переносов котораго через схему «ИЛИ 2 и линию задержки 3 соединен с одним из его входов. Кроме того, выход переноса сумматора 1 дополнительно соединея, надример, с одним из входов Схемы совпадения «И 4. На другой вход ее в соответствующие .моменты времени подают опорные (управляющие) импульсы (ОИ1). Выход суммы сумматора 1 через линию задержки 5 соединен с одним из входов второго одноразрядного двоичного сумматора 6. На другой

вход сумматора 6 подают двоичные коды оснований счета в группах (giv), через ключ 7. Выход схемы «И 4 ювязав со входом выключения ключа 7, а включение его производят ругими опорными (уцра.вляющ.ими) импульсами (ОИо). Выход переносов второго сумматора 6 соединен с третьим его входом, через схему запрета 8 переносов между группами, задержки 9 и собирательную схему «ИЛИ 10. На запрещающий ъход схемы запрета подают вторые опорные импульсы (ОИа), а на свободный вход схемы «ИЛИ 10 - сигнал изменения значения знакового разряда результата (Язн)- Выходом устройства вычитания является выход суммы последнего двоичного сумматора 6.

Устройство работает следующим образом. На вход схемы «ИЛИ 2 подают одиночный импульс (РОО), который задерживается с помощью линии задержки 3 и поступает .на один из ВХОДОВ одноразрядного двоичного сумматора 1. К этому же времени на два других входа, сумматора подают младшие разряды комбинир.ованных кодов уменьшаемого и вычит.аемого, цричем значения двоичных разрядов в Tpyliinax для вычитаемого должны 1быть предварительно проинвертированы. Вслед за млад щими разрядами на входы сумматора с заданной тактовой частотой последовательно подают следующие, .старщие по весу, разряды уменьшаемого и вычитаемого, а также импульсы переносов от сложения .предыдущих разрядов, проходящие че,рез схему «ИЛИ 2 и линию задерж ки 5.

Таким образом перечисленные элементы (узлы) обеспечивают сложение уменьшаемого с поразрядной ИИ-версией вычитаемого и добавочной единицей по правилу простого двоичното сложения, т. е. без учета разбиения комбинированного кода на группы двоичных разрядов, внутри которых счет должен производиться по заданному основанию (пределу). Однако такое сложение не может дать правильный результат непосредственно в используемой системе счисления. С целью его корректирования выявляют наличие импульсов переносов между группами с помощью схемы совпадения «И 4, один вход которой соединен с выходом переносов сумматора, а на другой в соответствующее время подают опорные (управляю1щие) импульсы (OHi). В случае наличия импульса переноса из одной группы двоичных разрядов в следующую результат сложения в ней равен требуемой разности. Если же он отсутствует, то результат от первого сложения в этой груопе требует иоправления. В предлагаемом устройстве вычитания коррекция групп производится путем добавления соответствующего двоичного кода основания (предела) счета и запрета переноса из дайной груп1пы в следующую с помощью другого двоичного сумматора 6, в -цепи переносов которого включена схема запрета 8. На ее запрещаю|щий вход и на вход вклю чвния ключа 7 подают другие «порные (управляющие) импульсы (ОИ2). Они определяют моменты запрета переносов и подготовки ключа 7. Если на выходе схемы «И 4 появится импульс, свидетельствующий о наличии переноса в следующую т,руппу, то ключ 7 закрывается, прерывая поступление кода основания счета на вход последнего сумматора 6. Следует отметить, что лрн равенстве основания (предела) счета в группе 2 в любой целой степени (2) результат лервого сложения в ней соответствует искомой разности и не требует дополнительных коррекций. Поэтому подачу кода такого основа1ния на вход ключа 7 нужно опустить. Для обеспечения сложения кода основания и соответствующих разрядов первой суммы, поступление шоследних на вход сумматора 6 задерживается (на время выявления наличия переноса в следующую группу) с помощью ЛИ1НИИ задержки 5. При использовании системы счисления с разнородными основаниями

счета эта задерж1ка определяется максимальным числом старщих разрядов в группах, требующих коррекцию. Так наприме р, для системы счета времени, кодированной группами двоичных разрядов, получим:

Для минут . . или 1010

Для десятков

минут ... 6 или 110

Для часов . .(72 24 или 11000

Сравнивая между собой записи оанований (пределО;В) счета (о, gi и дг} легко заметить, что для такой системы достаточно задержать код первой суммы на три лериода частоты следова1ния разрядов, так как остальные ,разряды не требуют коррекций.

Предлагаемое устройство вычитания может быть использовано и для переводов дополнительного комбинированного кода в прямой или обратный. Для этого достаточно подать

такой код 1на вход сумматора 1, предварительно проиЕв ртировав з начения всех его разрядов в группах, включая знаковый, произвести вычитание (из нуля) описанным путем и добавить единицу (Ран) в момент прихода

значения знакового разряда на вход второго сумматора 6.

Работа устройства вычитания не изменится, если поменять местами схему «ИЛИ 2 и линию задерж|ки 3, но импульс (Роо) в этом случае необходимо подавать одновременно с подачей младших разрядов кодов. Схема совпадения «И 4 может быть заменена любой другой схемой выявления наличия или отсутствия переносов между группами, но в последнем

случае требуется поменять местами входы включения и выключения ключа 7 и согласовать время Прихода на них импульсов. Схема запрета 8 может быть заменена, например, схемой совпадения, разрещающей переносы

внутри групп. Схема «ИЛИ 10 может быть перенесена на вход ключа 7, так как знаковый разряд не требует коррекции. И наконец, ключ 7 может быть заменен, например, регистром, в который записывается код основа1ния

счета или только его значащие разряды при

выявлении отсутствия переносов из какой-либо группы двоичных разрядов в следующую.

Предмет изобретения

Устройство для вычитания чисел, содержащее двоичдый Сумматор, € двумя входными щинами операндов и входной щиной переноса, выход суммы которого -через схему задержки соединен с первым входом второго сумматора, логические схемы и ключ, отличающееся тем, что, с целью обеспечения возможности вычитания чисел, представленных последовательными комбинированным кодом с двоич-ным кодированием чисел в группах и произвольным числом разрядов в , входная шина переноса первого сумматора через схему задержки соединена со схемой «ИЛИ, связанной входами с выходом .переноса первого сумматора и с шиной одиночного импульса, выход

переноса первого сумматора через схему «И, связанную с одной из шин опорных имлульсов, соединен с входом ключа, два других входа которого связаны с шиной двоичных кодов основания счета в группах и другой шиной

опорных импульсов, а выход ключа соединен со вторым входом второго сумматора, выход переноса которого через последовательно соединенные схему запрета, связанную со второй шиной опорных импульсов, схему задержки

и схему «ИЛИ, оодключевную к шине изменения знака, связан с его третьим входом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| Устройство для вычисления порядковых статистик последовательности @ @ -разрядных двоичных чисел | 1983 |

|

SU1144102A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Конвейерный сумматор | 1987 |

|

SU1427359A1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

QuiJiad

зн

Авторы

Даты

1973-01-01—Публикация