I

Изобретение относится к вычислительной тех«ике и приборостроению и предназначено для счета и индикации количества импульсов, вырабатываемых Несколькими датчиками.

Известен многоканалыный счетчик импульсов, содержащий запоминающие триггеры, выходы переноса которых через выходную схему «ИЛИ соединены с индикатором счета импульсов, логические схемы «И и «ИЛИ.

Цель изобретения-- увеличить быстродействие :11 повысить надежность работы счетчика.

Это достигается тем, что в нем входная клемма каждого из каналов через схему «ИЛИ подключена « счетному входу триггера, Нулевой и единичный выход которого соединены, соответственно с первыми входами первой .и второй схем «И. Цричем выход первой схемы «И соединен с другим вхОДом схемы «ИЛИ, выход второй схемы «И каждого предыдущего разряда связан со вторыми входами первой схемы «И каждого последующего разряда , а клемма импульсов считывания соединена со вторыми входами схем «И младщего разряда.

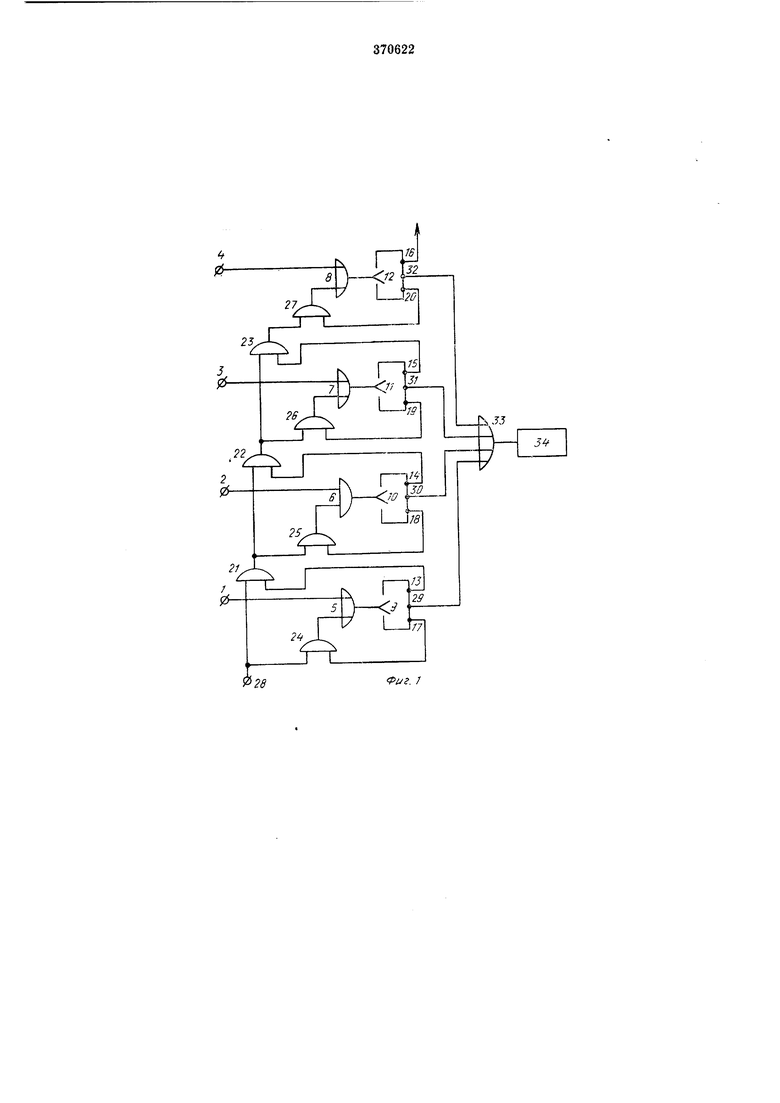

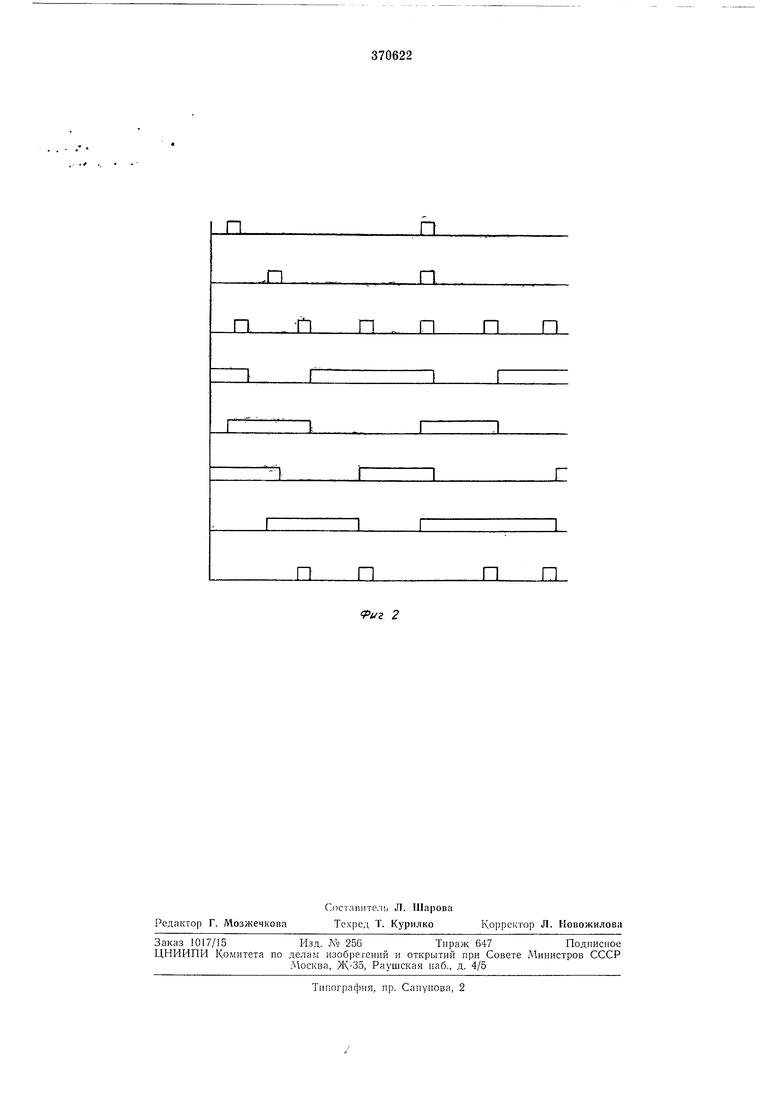

Нг- фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 - временная диагра мма сум.мироваиия последовательностей импульсов.

Устройство содержит входные клеммы /- 4 каналов, схеы «ИЛИ 5-8, запоминающие триггеры 9-12 с единичными 13-16 и нулевыми 18-20 выходами а: схемы совпадения «И 21-23 и 24-27. Кроме того, устройство включает клемму 28 импульсов считывания, выходы 29-32 переноса триггеров, выходную схему «ИЛИ 33 п индикатор 34 счета ИМПУЛЬСОВ.

10

Устройство работает следующим обрааом. Импульсы, поступающие на клеммы /-4 через схемы 5-8, перебрасывают триггеры 9-12 из нулевого в единичное состояние. Благодар-я тому, что единичные выхОДЫ 13-16 и нулевые выходы /7-20 триггеров 9-12 соединены соответственно со Входами схем 21- 23 и 24-27, импульс считывания с клеммы 28 поступает на вход того триггера, который из

единичного состояния переходит IB исходное нуле-вое. Образующийся при этом на выходах 29-33 им пульс через схему «ИЛИ 33 поступает на индикатор 34.

Благодаря схемаМ «И 24-27 переход

триггера из нулевого состояния в единичное происходит только от импульсов, подлежащих счету и приходящ;их на клеммы /-4, а считывающий импульс поступает на вход того т риггера, который находится в единичном состоянии. Таким образом, ассоциативным признаком считывания является единичное состояние триггера.

Схемы 21-23 обеспечивают прохождение счит:ывающих импульсов только при нулевых состояниях триггеров 9-12 и не цропускают импульс считывания, когда упомянутые триггеры. находятся в единичном состоянии. Благодаря этому импульс считывания проходит в последующие каналы только после считывания информации предыдущего канала.

При этом, если на все клеммы 1-4 импульсы, подлежащие счету, приходят одновременно, их считывание на индикатор происходит последювательно с частотой считывания.

Этот случай накладывает требование к частоте считывающих импульсов Го макс

где /о - частота считывающих импульсов;

ге -Количество каналов; -Рмакс - максимальная частота следования импульсов, подлежащих счету по одному из каналов.

Импульсы поступают по двум каналам многоканального счетчика импульсов, в котором в качестве запоминающих ячеек используются триггеры со счетным входом, меняющие свое состояние по заднему фронту входного импульса. как триггеры ,9-12 меняют свое

состояние по заднему фронту входного импульса, то длительность импульсов, подлежащих счету, практически не ограничена. Отсутствие дифференцирующих С-цепей обусловливает пониженные требования к фронтам импульсов.

Предмет изобретения

Многоканальный счетчик импульсо.в, содержащий запоминающие триггеры, зыходы переноса которых через выходную схему «ИЛИ соединены с индикатором счета импульсов, логические схемы «И и «ИЛИ, отличающийся тем, что, с целью увеличения быстродействия устройства и повышения надежности работы счетчика, в нем входная клемма, каждого из каналов через схему «ИЛИ подключена к счетному входу триггера, нулевой и

единичнып выходы которого соединены, соответственно, с первыми входаМИ первой и второй схем «И, причем выход первой схемы «И соединен с другим входом схемы «ИЛИ, выход второй схемы «И каждого предыдущего разряда связан со вторыми входами первой схемы «И .каждого последующего разряда, а клемма импульсов считывания соединена со вторыми входами схем «И младшего разряда.

Риг. /

JIL

П

П -П

П

П.

ПП

П , П

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное счетное устройство | 1976 |

|

SU640342A1 |

| Многоканальный фазометр | 1989 |

|

SU1720028A1 |

| Автоматический измеритель импульсной мощности СВЧ - радиосигналов | 1989 |

|

SU1704102A1 |

| Электронные вторичные часы с цифровой индикацией | 1983 |

|

SU1170417A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство задержки | 1985 |

|

SU1257819A1 |

| Устройство для задержки импульсов | 1982 |

|

SU1100723A1 |

| УСТРОЙСТВО для РЕГИСТРАЦИИ ОРДИНАТ СЧИТЫВАЕМЫХ ГРАФИКОВ | 1968 |

|

SU220652A1 |

| Генератор сигналов специальной формы | 1988 |

|

SU1550603A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

по.

пп.

Авторы

Даты

1973-01-01—Публикация