л 23

&-г1

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков, средств вычислительной техники и дискретной автоматики.

Целью изобретения является повышение быстродействия процесса контроля за счет возможности определения места неисправности объекта контроля без остановки процесса контроля.

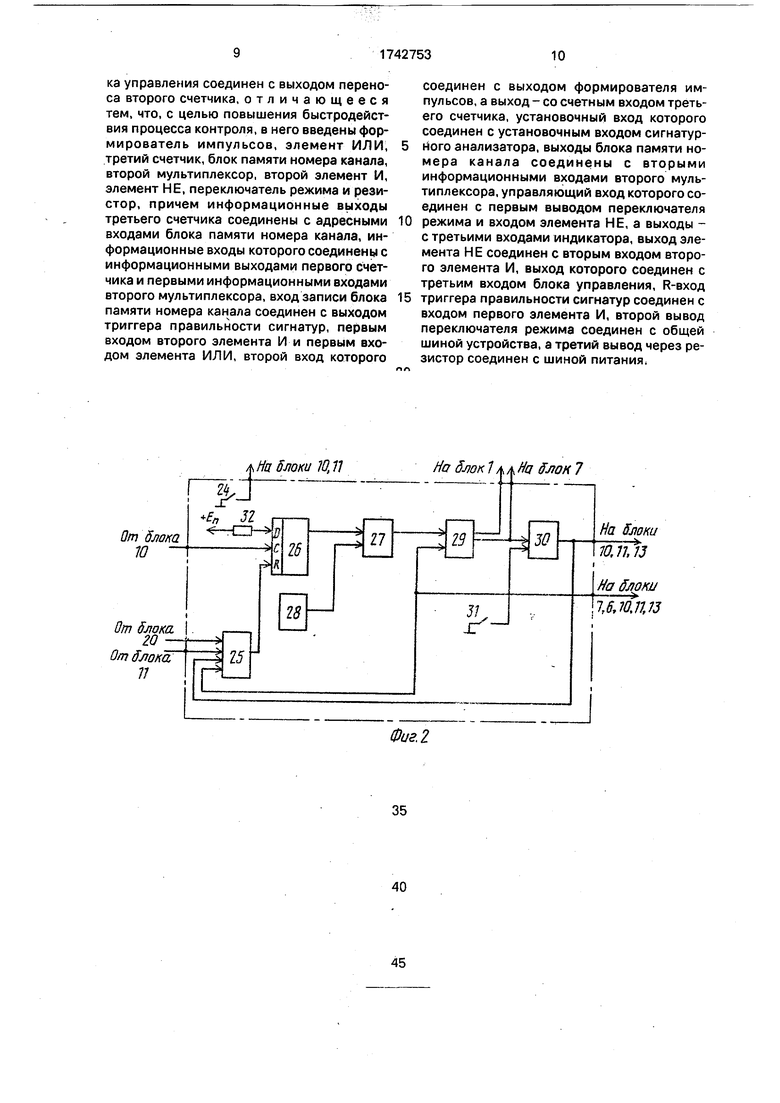

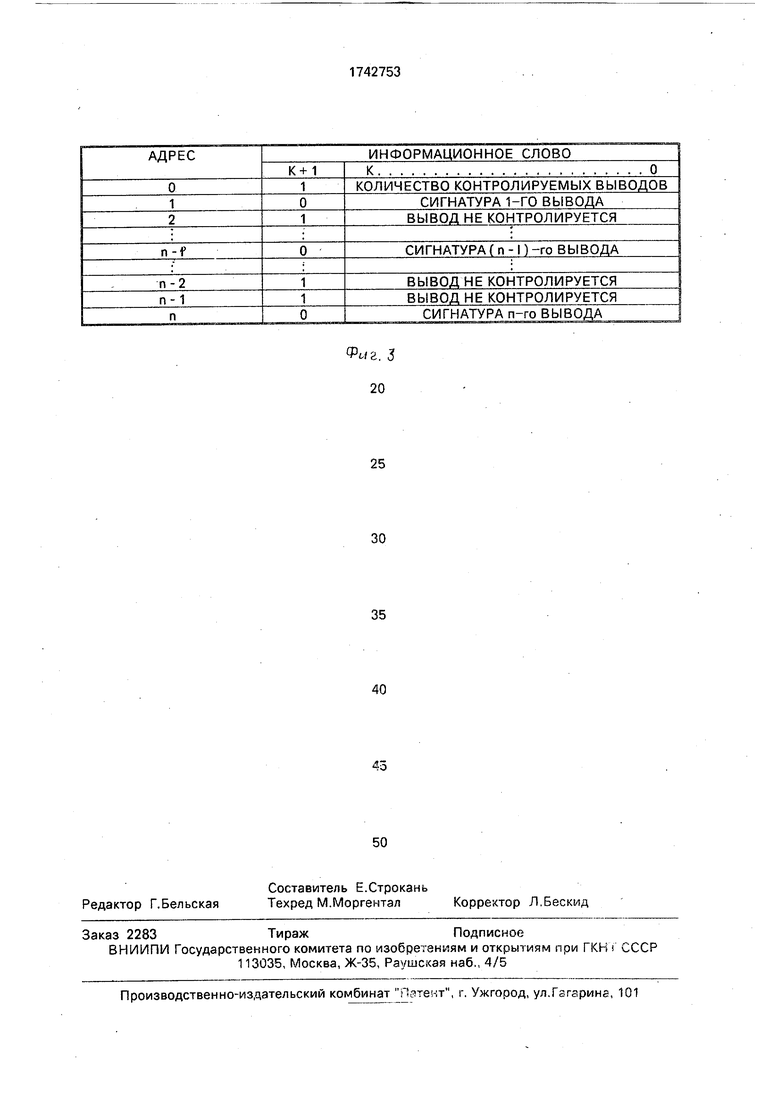

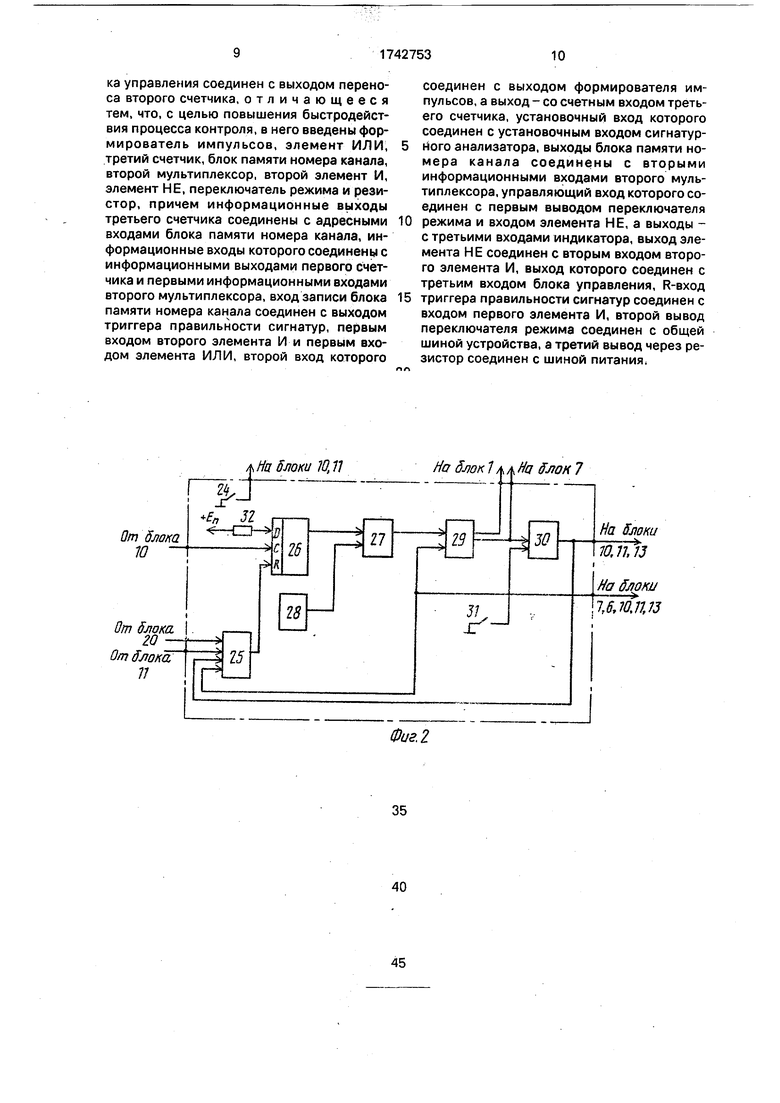

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока управления; на фиг, 3 - формат информации, хранящийся в блоке памяти сигнатур.

Устройство для контроля цифровых блоков содержит задатчик 1 тестов, подключенный к контролируемому цифровому блоку 2, первый мультиплексор 3, генератор 4 пачки импульсов, первый элемент И 5, первый счетчик 6, сигнатурный анализатор 7, блок 8 управления, блок 9 памяти сигнатур, D-триг- гер 10, второй счетчик 11, блок 12 сравнения, триггер 13 правильности сигнатур, индикатор 14, формирователь 15 импульсов, элемент ИЛИ 16, третий счетчик 17, блок 18 памяти номера канала, второй мультиплексор 19, второй элемент И 20, элемент НЕ 21, переключатель 22 режима, резистор 23.

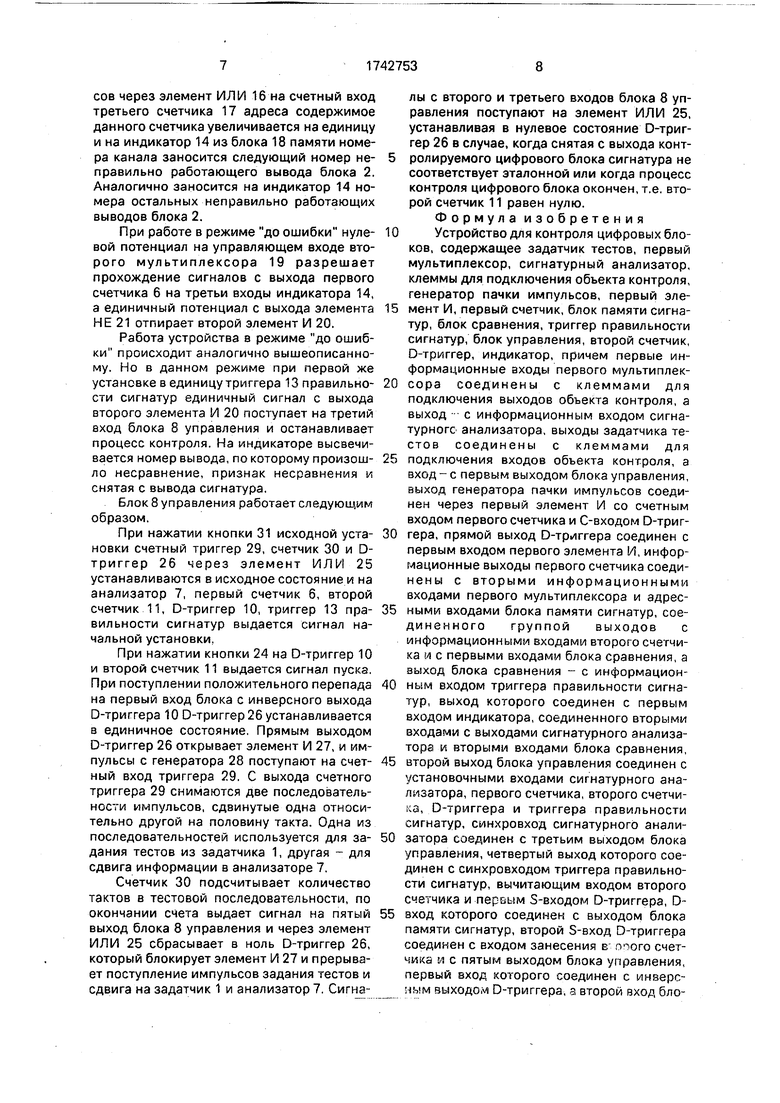

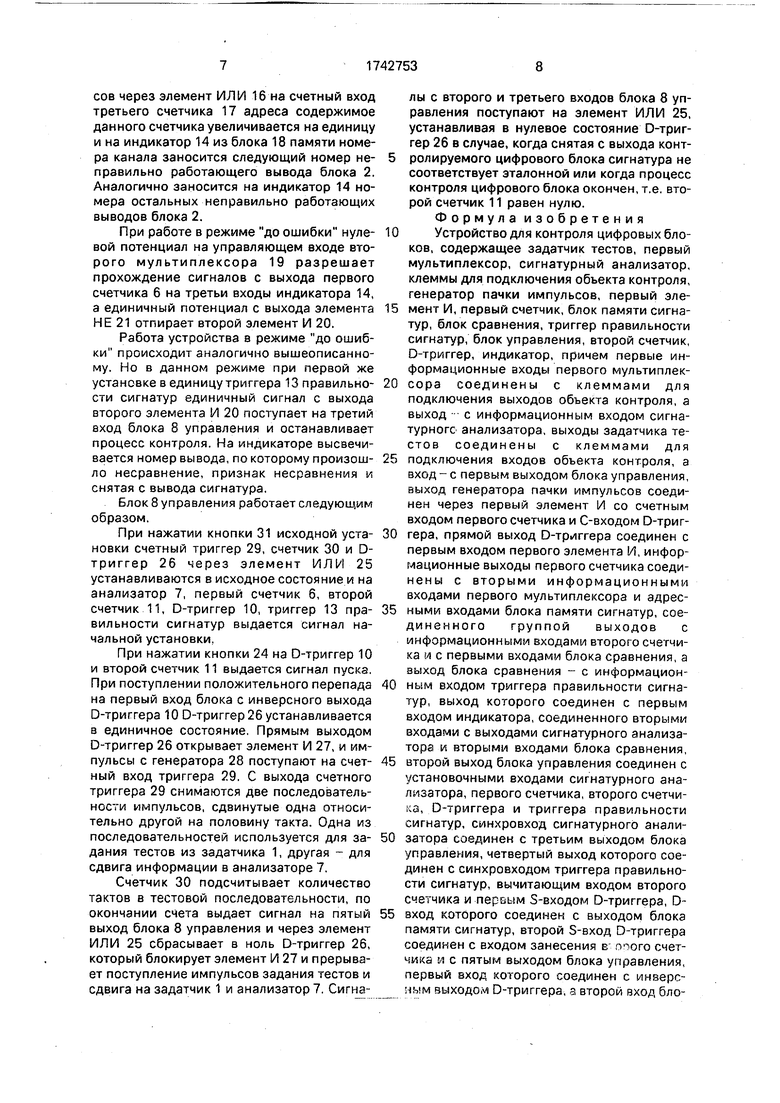

Блок 8 управления содержит кнопку 24 пуска, элемент ИЛИ 25 D-триггер 26, элемент И 27, генератор 28 импульсов, счетный триггер 29, счетчик 30, кнопку 31 исходной установки,резистор 32.

Блок 9 памяти сигнатур представляет собой постоянное запоминающее устройство (ПЗУ) с организацией п-(К + 1) бит, где п - максимальный номер выхода контролируемого цифрового блока; К - разрядность сигнатуры.

По нулевому адресу в ПЗУ записывают количество выходов контролируемого цифрового блока 2 в двоичном коде. В адресном поле (с 1 по п), в информационном слове (с 1 по К) записывают эталонную сигнатуру каждого выхода контролируемого цифрового блока 2 в ячейку, адрес которой соответствует порядковому номеру выхода, при этом в информационном слове (разряд К + 1) записывают О, если этот выход подлежит контролю по данной сигнатуре, или 1, если данный вывод в контролируемом цифровом блоке 2 отсутствует или он является входом.

Устройство работает следующим образом,

Блок 8 управления выдает сигнал начальной установки, который устанавливает сигнатурный анализатор 7, первый счетчик

6, второй счетчик 11, третий счетчик 17, D- триггер 10 и триггер 13 правильности сигнатур в исходное нулевое состояние. Переключателем 22 режимов задается либо

режим до ошибки (на выходе переключателя 22 режимов задается потенциал лог. О), либо режим до конца (на выходе переключателя 22 режимов задается потенциал лог. 1).

0 При работе в режиме до конца единичный потенциал на управляющем входе второго мультиплексора 19 разрешает прохождение сигналов с выходов блока 18 памяти номера канала на третьи входы ин5 дикатора 14, а нулевой потенциал с выхода элемента НЕ 21 закрывает второй элемент И 20.

По сигналу Пуск из блока 8 управления во второй счетчик 11 записывается по

0 информационным входам из блока 9 памяти сигнатур количество проверяемых выходов в контролируемом цифровом блоке 2 в двоичном коде. По этому же сигналу D-триггер 10 устанавливается в единичное состояние

5 и своим прямым выходом открывает первый элемент И 5,

По первому сигналу с генератора 4 пачки импульсов через первый элемент И 5 первый счетчик 6 устанавливается в единич0 ное состояние, из блока Э памяти сигнатур выбирается содержимое первого адреса, Если первый вывод в контролируемом цифровом блоке 2 является выходным, то в разряде (К + 1) блока 9 памяти сигнатур

5 записывается О.

По заднему фронту сигнала с первого элемента И 5 D-триггер 10 сбрасывается в ноль и элемент И 5 запирается. На первом счетчике 6 фиксируется единичное состоя0 ние. К информационному входу сигнатурного анализатора 7 через первый мультиплексор 3 заключается первый выход контролируемого цифрового блока 2, Эталонная сигнатура, соответствующая перво5 му выходу, записана по первому адресу в блоке 9 памяти сигнатур, Эталонная сигнатура поступает с информационных выходов блока 9 памяти сигнатур на первые входы блока 12 сравнения. По положительному пе0 репаду с инверсного выхода D-триггера 10 блек 8 управления выдает сигнал по первому выходу, по которому осуществляется вывод с задатчика 1 тестов первого теста на входы контролируемого блока 2. С первого

5 выхода блока 2 информация через мультиплексор 3 поступает на сигнатурный анализатор 7, представляющий собой сдвигающий pei метр, охваченный обратными связями через схему сложения по модулю два. По первому сигналу сдвига с блока

8 управления эта информация записывается в первый разряд анализатора 7.

По второму сигналу с блока 8 управления задатчик 1 тестов выдает второй тест на блок 2, а с первого выхода блока 2 через мультиплексор 3 второй бит информации поступает на вход анализатора 7 и по второму сигналу сдвига с блока 8 управления записывается в анализатор 7 и т.д. до тех пор, пока вся тестовая программа не будет выведена из задатчика 1 тестов и вся последова- тельность кодов с первого выхода контролируемого блока 2 не окажется свернутой в сигнатурном анализаторе 7. Свертка этой информации поступает в параллельном коде на вторые входы блока 12 сравнения и на вторые входы индикатора 14. После этого блок 8 управления выдает сигнал с четвертого выхода, который фиксирует на триггере 13 правильности сигнатур результат сравнения информации, полученной на сигнатурном анализаторе 7 с первого выхода блока 2 и выведенной из первого адреса блока 9 памяти сигнатур. В случае сравнения и эталонной сигнатуры, т.е. триггер 13 правильности сигнатур находится в нулевом состоянии, по заднему фронту сигнала с четвертого выхода блока 8 управления содержимое второго счетчика 11 уменьшается на единицу, а D-триггер 10 устанавливается в единичное состояние и своим прямым выходом открывает первый элемент И 5. Сигналы с генератора 4 пачки импульсов через открытый элемент И 5 поступают на счетный вход первого счетчика 6. Из блока 9 памяти сигнатур выбирается содержимое второго адреса, и к сигнатурному анализатору 7 через мультиплексор 3 подключается второй выход блока 2.

Если с второго выхода блока 9 памяти сигнатур считан ноль, означающий, что второй выход контролируемого блока 2 подлежит контролю, D-триггер 10 устанавливается в нугевое состояние и происходит снятие и сравнение сигнатуры с второго вывода, как и для первого. В случае, если с второго выхода блока 9 памяти сигнатур считана единица, означающая, что данный вывод контролируемого цифрового блока 2 не подлежит контролю, D-триггер 10 остается в единичном состоянии, первый счетчик 6 изменяет состояние на единицу, из блока 9 памяти сигнатур выбирается информация со следующего адреса и т.д., пока с второго выхода блока 9 памяти сигнатур не считывается ноль, означающий, что данный выход контролируемого цифрового блока 2 подлежит контролю по эталонной сигнатуре, записанной в этом адресе.

После каждого снятия сигнатуры с выходов контролируемого цифрового блока 2 и ее сравнения с эталонной содержимое второго счетчика 11 уменьшается на единицу.

После того как все выходы контролируемого блока 2 будут проверены, содержимое второго счетчика 11 станет равно нулю и по сигналу переноса с второго счетчика 11 блок 8 управления прекратит процесс контроля.

0 Если снятая с какого-либо вывода блока 2 сигнатура отлична от эталонной, записанной в адресе, соответствующем номеру проверяемого в настоящий момент вывода, считается, что данный вывод неисправен.

5 Сигнал единичного уровня с выхода триггера 13 правильности сигнатур в качестве счетного импульса поступает через элемент ИЛИ 16 на вход третьего счетчика 17 адреса и в качестве сигнала записи - на вход записи

0 блока 18 памяти номера канала. Останов блока 8 управления блокируется элементом И 20. В блоке 18 памяти номера канала по нулевому адресу оказывается зафиксированным номер неправильно работающего

5 вывода блока 2.

По заднему фронту сигнала с четвертого выхода блока 8 управления содержимое второго счетчика 11 уменьшается на единицу, а D-триггер 10 устанавливается в единичное

0 состояние и своим прямым входом открывает первый элемент И 5. Сигнал с генератора 4 пачки импульсов через открытый первый элемент И 5 вновь поступает на счетный вход первого счетчика 6, на С-вход D-триг5 гера 10 и одновременно сбрасывает в ноль триггер 13 правильности сигнатур, и по заднему фронту сигнала с его выхода увеличивается на единицу содержимое счетчика 17 адреса, Работа устройства продолжается

0 аналогично вышеописанному.

В случае повторной установки в единицу триггера 13 правильности сигнатур (при обнаружении очередного неправильно работающего вывода блока 2) третий счетчик

5 17 адреса увеличивает свое содержимое на единицу и запись номера очередного неправильно работающего вывода блока 2 в блок 18 памяти номера канала осуществляется аналогично вышеописанному,

0 По окончании проверки блока 2 по всем выводам из блока 8 управления вновь подается сигнал начальной установки. Третий счетчик 17 адреса устанавливается в ноль, и информация из нулевого адреса блока 18

5 памяти номера канала через второй мультиплексор 19 поступает на индикатор 14. Таким образом, на индикатор заносится номер первого обнаруженного неправильно работающего вывода блока 2. При поступлении импульса с формирователя 15 импульсов через элемент ИЛИ 16 на счетный вход третьего счетчика 17 адреса содержимое данного счетчика увеличивается на единицу и на индикатор 14 из блока 18 памяти номера канала заносится следующий номер не- правильно работающего вывода блока 2, Аналогично заносится на индикатор 14 номера остальных неправильно работающих выводов блока 2.

При работе в режиме до ошибки нуле- вой потенциал на управляющем входе второго мультиплексора 19 разрешает прохождение сигналов с выхода первого счетчика 6 на третьи входы индикатора 14, а единичный потенциал с выхода элемента НЕ 21 отпирает второй элемент И 20.

Работа устройства в режиме до ошибки происходит аналогично вышеописанному. Но в данном режиме при первой же установке в единицу триггера 13 правильно- сти сигнатур единичный сигнал с выхода второго элемента И 20 поступает на третий вход блока 8 управления и останавливает процесс контроля. На индикаторе высвечивается номер вывода, по которому произош- ло несравнение, признак несравнения и снятая с вывода сигнатура.

Блок 8 управления работает следующим образом.

При нажатии кнопки 31 исходной уста- новки счетный триггер 29, счетчик 30 и D- триггер 26 через элемент ИЛИ 25 устанавливаются в исходное состояние и на анализатор 7, первый счетчик 6, второй счетчик 11, D-триггер 10, триггер 13 пра- вильности сигнатур выдается сигнал начальной установки,

При нажатии кнопки 24 на D-триггер 10 и второй счетчик 11 выдается сигнал пуска. При поступлении положительного перепада на первый вход блока с инверсного выхода D-триггера 10 D-триггер 26 устанавливается в единичное состояние. Прямым выходом D-триггер 26 открывает элемент И 27, и импульсы с генератора 28 поступают на счет- ный вход триггера 29. С выхода счетного триггера 29 снимаются две последовательности импульсов, сдвинутые одна относительно другой на половину такта. Одна из последовательностей используется для за- дания тестов из задатчика 1, другая - для сдвига информации в анализаторе 7.

Счетчик 30 подсчитывает количество тактов в тестовой последовательности, по окончании счета выдает сигнал на пятый выход блока 8 управления и через элемент ИЛИ 25 сбрасывает в ноль D-триггер 26, который блокирует элемент И 27 и прерывает поступление импульсов задания тестов и сдвига на задатчик 1 и анализатор 7. Сигналы с второго и третьего входов блока 8 управления поступают на элемент ИЛИ 25, устанавливая в нулевое состояние D-триггер 26 в случае, когда снятая с выхода контролируемого цифрового блока сигнатура не соответствует эталонной или когда процесс контроля цифрового блока окончен, т.е. второй счетчик 11 равен нулю.

Формула изобретения Устройство для контроля цифровых блоков, содержащее задатчик тестов, первый мультиплексор, сигнатурный анализатор, клеммы для подключения объекта контроля, генератор пачки импульсов, первый элемент И, первый счетчик, блок памяти сигнатур, блок сравнения, триггер правильности сигнатур, блок управления, второй счетчик, D-триггер, индикатор, причем первые информационные входы первого мультиплексора соединены с клеммами для подключения выходов объекта контроля, а выход с информационным входом сигнатурного анализатора, выходы задатчика тестов соединены с клеммами для подключения входов объекта контроля, а вход - с первым выходом блока управления, выход генератора пачки импульсов соединен через первый элемент И со счетным входом первого счетчика и С-входом D-триггера, прямой выход D-триггера соединен с первым входом первого элемента И, информационные выходы первого счетчика соеди- нены с вторыми информационными входами первого мультиплексора и адресными входами блока памяти сигнатур, соединенного группой выходов с информационными входами второго счетчика и с первыми входами блока сравнения, а выход блока сравнения - с информационным входом триггера правильности сигнатур, выход которого соединен с первым входом индикатора, соединенного вторыми входами с выходами сигнатурного анализатора и вторыми входами блока сравнения, второй выход блока управления соединен с установочными входами сигнатурного анализатора, первого счетчика, второго счетчика, D-триггера и триггера правильности сигнатур, синхровход сигнатурного анализатора соединен с третьим выходом блока управления, четвертый выход которого соединен с синхровходом триггера правильности сигнатур, вычитающим входом второго счетчика и первым 3-входом D-триггера, D- вход которого соединен с выходом блока памяти сигнатур, второй S-вход D-триггера соединен с входом занесения в счетчика и с пятым выходом блока управления, первый вход которого соединен с инверс- HS M выходом D-триггера, а второй вход блока управления соединен с выходом переноса второго счетчика, отличающееся тем, что, с целью повышения быстродействия процесса контроля, в него введены формирователь импульсов, элемент ИЛИ, третий счетчик, блок памяти номера канала, второй мультиплексор, второй элемент И, элемент НЕ, переключатель режима и резистор, причем информационные выходы третьего счетчика соединены с адресными входами блока памяти номера канала, информационные входы которого соединены с информационными выходами первого счетчика и первыми информационными входами второго мультиплексора, вход записи блока памяти номера канала соединен с выходом триггера правильности сигнатур, первым входом второго элемента И и первым входом элемента ИЛИ, второй вход которого

соединен с выходом формирователя импульсов, а выход- со счетным входом третьего счетчика, установочный вход которого соединен с установочным входом сигнатурйого анализатора, выходы блока памяти номера канала соединены с вторыми информационными входами второго мультиплексора, управляющий вход которого соединен с первым выводом переключателя

режима и входом элемента НЕ, а выходы - с третьими входами индикатора, выход элемента НЕ соединен с вторым входом второго элемента И, выход которого соединен с третьим входом блока управления, R-вход

триггера правильности сигнатур соединен с входом первого элемента И, второй вывод переключателя режима соединен с общей шиной устройства, а третий вывод через резистор соединен с шиной питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1458841A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

Сущность изобретения: устройство содержит: задатчик тестов (1), подключенный к контролируемому цифровому блоку (2), первый мультиплексор (3), генератор пачки импульсов (4), первый элемент И (5), первый счетчик (6), сигнатурный анализатор(7), блок управления (8), блок памяти сигнатур (9). D- триггер (10), второй счетчик (11), блок сравнения (12), триггер правильности сигнатур

Ни блоки 10,11

От Злака 10

От блока.

2Q От йлока.

77

На 8лох1 ЛА№ йлок 7

На $локи

10,1113 На блоки

WQ.W3

. 3 20

25 30 35

40 43 50

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1458841A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-06-23—Публикация

1989-01-09—Подача