1

Изобретение относится к импульсной и цифровой вычислительной технике и может использоваться в устройствах регулируемой временной задержки дискретной информации.

Целью изобретения является расширение области применения за счет обеспечения возможности задержки импульсов произвольной длительности и регулировки длительности задержки прямым или дополнительным двоичным кодом.

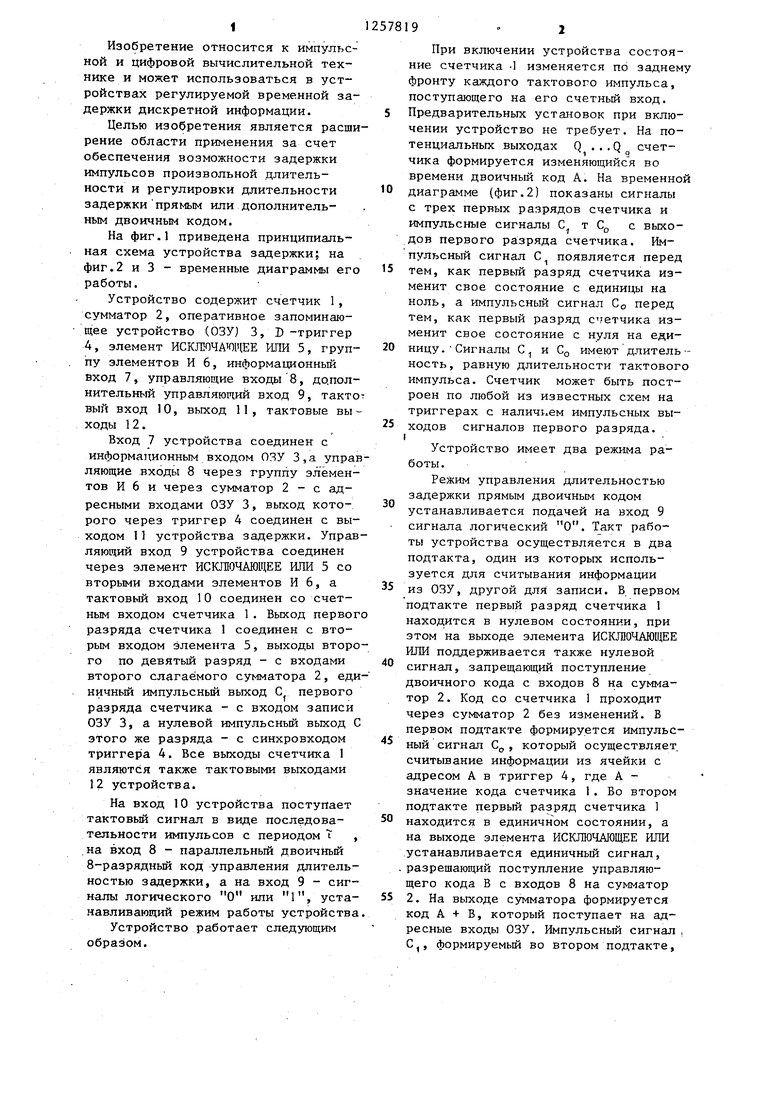

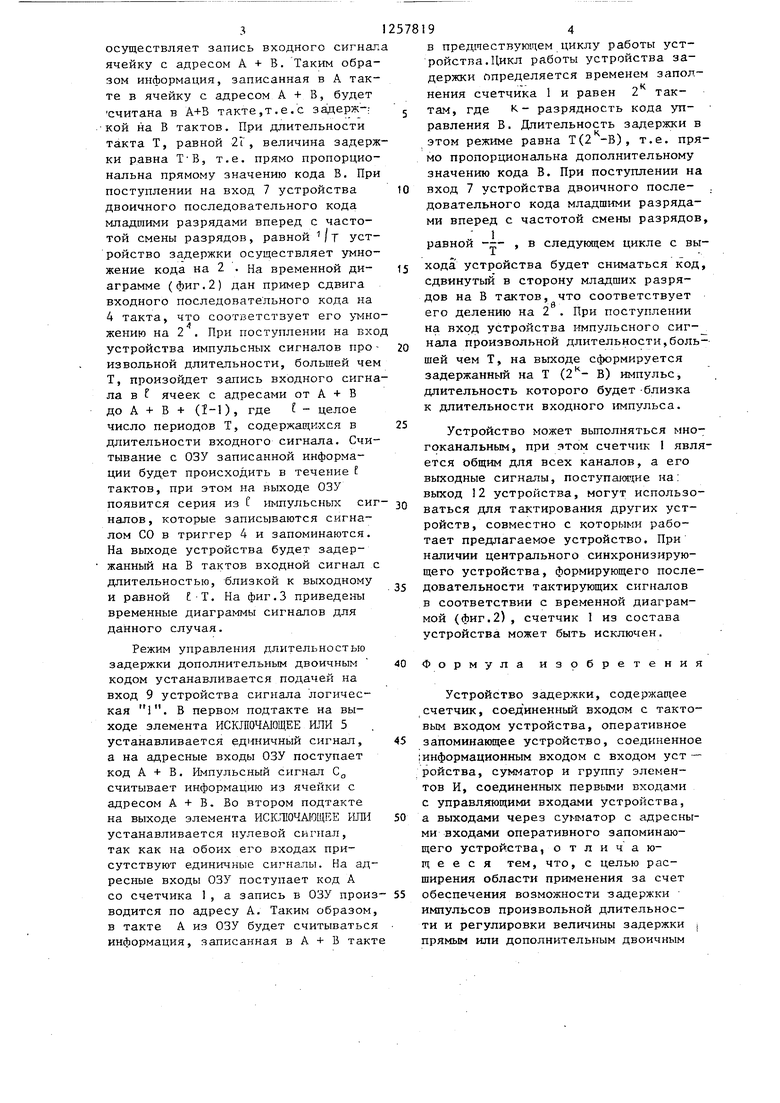

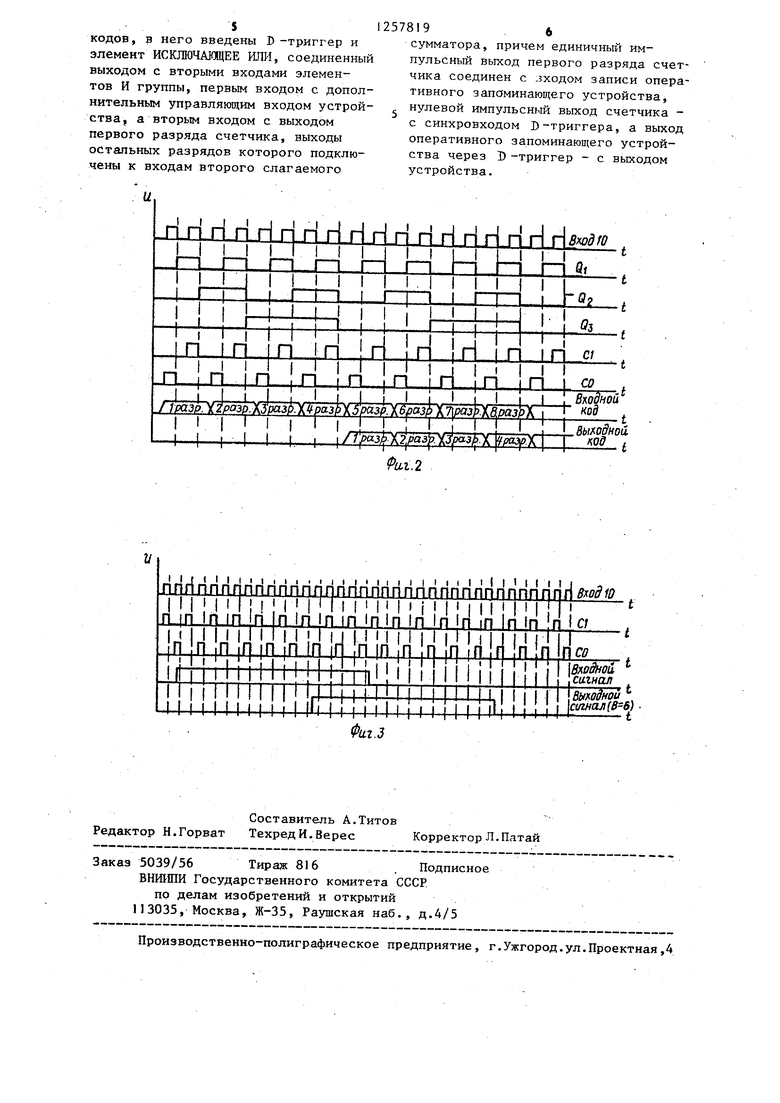

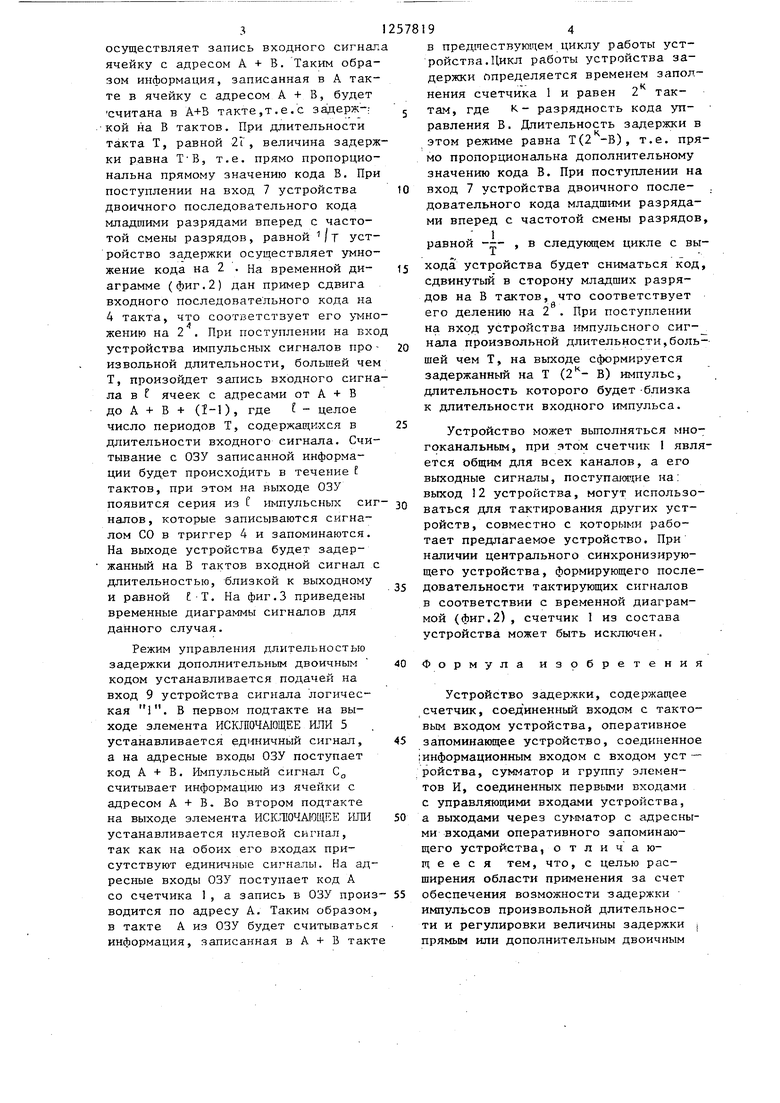

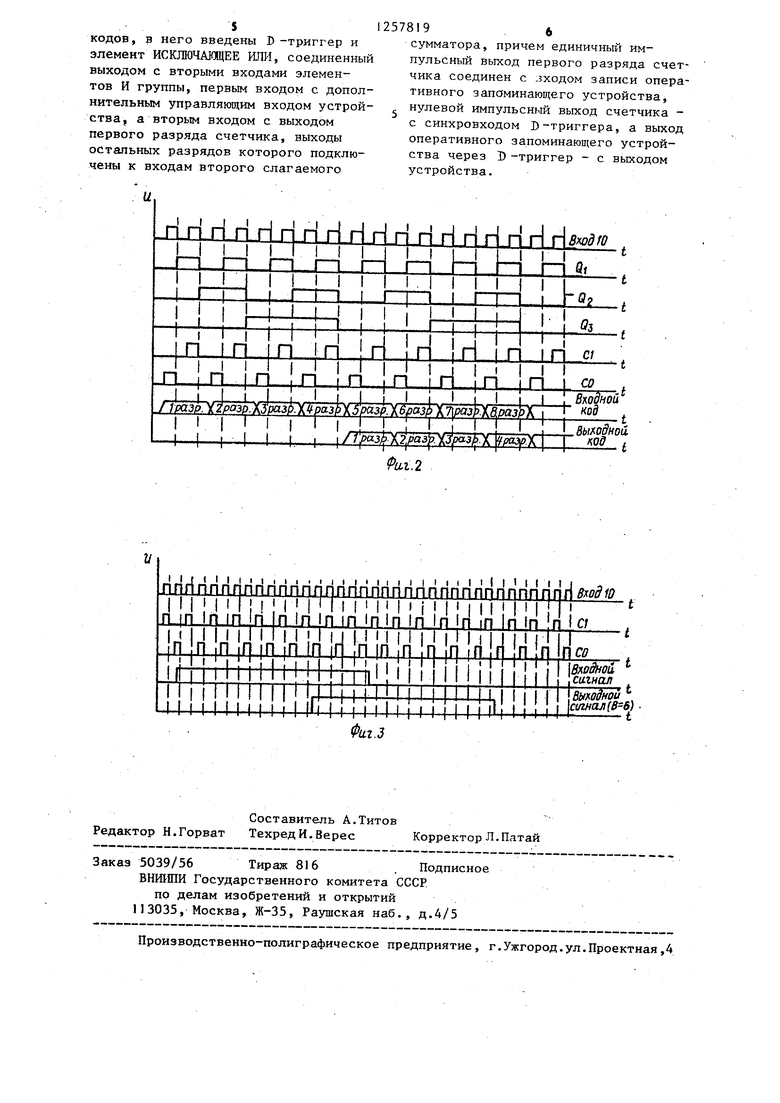

На фиг.1 приведена принципиальная схема устройства задержки; на фиг.2 и 3 - временные диаграммы ег работы.

Устройство содержит счетчик 1, сумматор 2, оперативное запоминающее устройство (ОЗУ) 3, D -триггер 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, груп пу элементов И 6, информационньш вход 7, управляющие входы 8, дополнительный управляющий вход 9, такт вый вход 10, выход 11, тактовые вы ходы 12.

Вход 7 устройства соединен с информационным входом ПЯУ 3,а упраляющие входы 8 через группу элементов И 6 и через сумматор 2-е адресными входами ОЗУ 3, выход кото- рого через триггер 4 соединен с выходом 11 устройства задержки. Упраляющий вход 9 устройства соединен через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 со вторыми входами элементов И 6, а тактовый вход 10 соединен со счетным входом счетчика 1. Выход перво разряда счетчика 1 соединен с вторым входом элемента 5, выходы вторго по девятый разряд - с входами второго слагаемого сумматора 2, ед ничный импульсньй выход С первого разряда счетчика - с входом записи ОЗУ 3, а нулевой импульсный выход этого же разряда - с синхровходом триггера 4. Все выходы счетчика 1 являются также тактовыми выходами 12 устройства.

На вход 10 устройства поступает тактовый сигнал в виде последова- тельности импульсов с периодом Т ,на вход 8 - параллельный двоичный 8-разрядный код управления длительностью задержки, а на вход 9 - сигналы логического О или 1, уста навливающий режим работы устройств

Устройство работает следующим образом.

5

5

0

0 5 0 5

0 5

При включении устройства состояние счетчика -1 изменяется по заднему фронту каждого тактового импульса, поступающего на его счетный вход. Предварительных установок при включении устройство не требует. На потенциальных выходах Q ...Q счетчика формируется изменяющийся во времени двоичный код А. На временной диаграмме (фиг.2) показаны сигналы с трех первых разрядов счетчика и импульсные сигналы С т С с выходов первого разряда счетчика. Импульсный сигнал С появляется перед тем, как первый разряд счетчика изменит свое состояние с единицы на ноль, а импульсный сигнал Со перед тем, как первый разряд с етчика изменит свое состояние с нуля на единицу. Сигналы С и Со имеют длитель- ность, равную длительности тактового импульса. Счетчик может быть построен по любой из известных схем на триггерах с налич1.ем импульсных выходов сигналов первого разряда. I

Устройство имеет два режима работы.

Режим управления длительностью задержки прямым двоичным кодом устанавливается подачей на вход 9 сигнала логический О. Такт работы устройства осуществляется в два подтакта, один из которых используется для считывания информации из ОЗУ, другой для записи. В. первом подтакте первый разряд счетчика 1 находится в нулевом состоянии, при этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ поддерживается также нулевой сигнал, запрещающий поступление двоичного кода с входов 8 на сумматор 2. Код со счетчика 1 проходит через сумматор 2 без изменений. В первом подтакте формируется импульсный сигнал С , который осуществляет, считывание информация из ячейки с адресом А в триггер 4, где А - значение кода счетчика 1. Во втором подтакте первый разряд счетчика 1 находится в единичном состоянии, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается единичный сигнал, разрешающий поступление управляющего кода В с входов 8 На сумматор 2. На выходе сумматора формируется код А + Б, который поступает на адресные входы ОЗУ. Импульсный сигнал ,

1

формируемый во втором подтакте.

что соответствует его умно 2 . При поступлении на вхо

осуществляет запись входного сигнал ячейку с адресом А + В. Таким образом информация, записанная в А такте в ячейку с адресом А + В, будет считана в А+В такте,т.е.с задерж-: кой на В тактов. При длительности такта Т, равной 21, величина задержки равна Т В, т.е. прямо пропорциональна прямому значению кода В. При поступлении на вход 7 устройства двоичного последовательного кода младшими разрядами вперед с частотой смены разрядов, равной /т устройство за держки осуществляет умножение кода на 2 .На временной диаграмме (фиг.2) дан пример сдвига входного последовательного кода на 4 такта, жеПИЮ на

устройства импульсных сигналов про - извольной длительности, большей чем Т, произойдет запись входного сигнала в f ячеек с адресами от А + В до А + В + (1-1), где f - целое число периодов Т, содержащихся в длительности входного сигнала. Считывание с ОЗУ записанной информации будет происходить в течение Е тактов, при этом на выходе ОЗУ появится серия из f импульсных сигналов, которые записываются сигналом СО в триггер 4 и запоминаются. На выходе устройства будет задержанный на В тактов входной сигнал с длительностью, близкой к выходному и равной Е-Т. На фиг.З приведены временные диаграммы сигналов для данного случая.

Режим управления длительностью задержки дополнительным двоичным кодом устанавливается подачей на вход 9 устройства сигнала логическая 1. В первом подтакте на выходе элемента ИСКЛОЧАЮЩЕЕ ИЛИ 5 устанавливается единичный сигнал, а на адресные входы ОЗУ поступает код А+В. Импульсный сигнал С считывает информацию из ячейки с адресом А+В. Во втором подтакте на выходе элемента ИСК.ГПОЧАЮЩЕЕ Шт устанавливается нулевой сигнал, так как на обоих его входах присутствуют единичные сигналы. На адресные входы ОЗУ поступает код А со счетчика 1 , а запись в ОЗУ произ- водится по адресу А. Таким образом, в такте А из ОЗУ будет считываться информация, записанная в А + В такте

10

5

0

5

0

5

равной --в предшествующем циклу работы устройства. Цикл работы устройства задержки определяется временем заполнения счетчика 1 и равен 2 тактам, где к- разрядность кода уп- равнения В. Длительность задержки в этом режиме равна Т(2 -В), т.е. прямо пропорциональна дополнительному значению кода В. При поступлении на вход 7 устройства двоичного последовательного кода младшими разрядами вперед с частотой смены разрядов,

1

, в следующем цикле с выхода; устройства будет сниматься код, сдвинутый в сторону младших разрядов на В тактов, что соответствует его делению на 2 . При поступлении на вход устройства 1-1мпульсного сиг- нала произвольной длительности,большей чем Т, на выходе сформируется задержанный на Т ( В) импульс, длительность которого будет -близка к длительности входного импульса.

Устройство может вьшолняться многоканальным, при этом счетчик 1 является общим для всех каналов, а его выходные сигналы, поступакщие на: выход 12 устройства, могут использоваться для тактирования других устройств, совместно с которыми работает предлагаемое устройство. При наличии центрального синхронизирующего устройства, формирующего последовательности тактирующих сигналов в соответствии с временной диаграммой (фиг.2), счетчик I из состава устройства может быть исключен.

5

40 Формула изобретения

Устройство задержки, содержащее счетчик, соед иненный входом с тактовым входом устройства, оперативное запоминающее устройство, соединенное информационным входом с входом уст - ройства, сумматор и группу элементов И, соединенных первыми входами с управляющими входами устройства, а выходами через сумматор с адресными входами оперативного запоминающего устройства, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности задержки импульсов произвольной длительности и регулировки величины задержки прямым или дополнительным двоичным

кодов, в него введены D -триггер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, соединенный выходом с вторыми входами элементов И группы, первым входом с дополнительным управляющим входом устройства, а вторым входом с выходом первого разряда счетчика, выходы остальных разрядов которого подключены к входам второго слагаемого

I I f I I I I I I I I I I I I I I r I I I I I I I I I I I I I I I J -3

nnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnnn gg g

т

I I I I I I I I I I I I

щи

I 11 I I j I 1 I (( I I I I |У( I In In In InJri in InJn nlc/

MM I inlftinJnJjilnjnirL

578196

сумматора, причем единичный им- пульсньш выход первого разряда счетчика соединен с зходом записи оперативного запоминающего устройства, нулевой импульсный выход счетчика - с синхровходом D-триггера, а выход оперативного запоминающего устройства через D -триггер - с вькодом устройства.

I I r I I I I I I I I I I I I I I I J

nnnnnnnnnnnnnnnnnn g

I I I I I I I I I I I I

щи

I 11 I I j I 1 I (( I I I I |У( I In In In InJri in InJn nlc/

I I

4fl

4П

If, I 11 f Г ) I 1 I Т

I I I и 11 I 11 I I h 111111 I I

444W

I 1

m

ce

сигнал

t

мЗнои IctoHOji e)

Т

11 I I

йД

Фаг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования @ последовательно поступающих чисел | 1985 |

|

SU1322262A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1982 |

|

SU1077539A1 |

| ЛАЗЕРНЫЙ ИМПУЛЬСНЫЙ ДАЛЬНОМЕР | 2014 |

|

RU2551700C1 |

| Многоканальное устройство для формирования импульсных последовательностей | 1987 |

|

SU1443745A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Цифровой генератор функций | 1986 |

|

SU1324092A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

Изобретение относится к импульсной и цифровой вычислительной технике и может быть использовано в устройствах регулируемой временной задержки дискретной информации. Цель изобретения - расширение области применения устройства. Устройство содержит счетчик 1, сумматор 2, оперативное запоминающее устройство 3 и группу элементов И 6. Введение D -триггера 4 и элемента : ИСКЛОЧАЩЕЕ ИЛИ 5 обеспечивает возможность задержки импульсов произвольной длительности и регулировку длительности задержки прямым или дополнительным двоичным кодом. 3 ил. 9 (Л 11 Ю сл 00 со

Составитель А.Титов Редактор Н.Горват Техред И. Верес Корректор Л.Патай

Заказ 5039/56 Тираж 816 . Подписное ВНЮШИ Государственного комитета СССР.

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород.ул.Проектная,4

| Цифровая линия задержки | 1983 |

|

SU1109895A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-09-15—Публикация

1985-01-23—Подача