J1550603

Изобретение относится к импульсной технике и может быть использовано для испытаний аппаратуры в условиях наличия в цепях питания или на входах различных помех, а также для генерирования импульсов специальной формы, в частном случае генератор может быть использован в качестве имитатора проторого соединен со вторым входом запоминающего блока 8, третий выход блока 3 соединен с первым входом запоминающего блока 9, четвертый выход блока 3 соединен с первым входом второго блока 6, выход которого соединен со вторым выходом запоминающего блока 9. Первый выход запоминающего

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1495996A2 |

| Генератор знаков | 1979 |

|

SU911576A2 |

| Устройство для контроля дискретного объекта | 1984 |

|

SU1218398A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

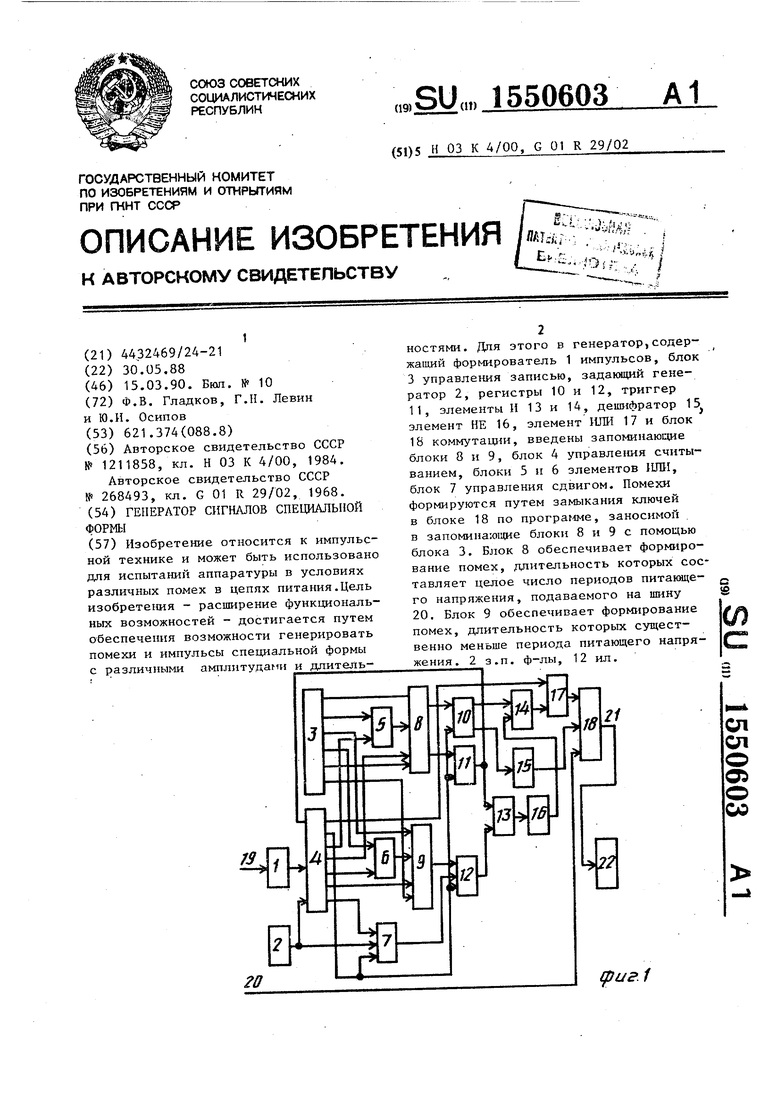

Изобретение относится к импульсной технике и может быть использовано для испытаний аппаратуры в условиях различных помех в цепях питания. Цель изобретения - расширение функциональных возможностей - достигается путем обеспечения возможности генерировать помехи и импульсы специальной формы с различными амплитудами и длительностями. Для этого в генератор, содержащий формирователь 1 импульсов, блок 3 управления записью, задающий генератор 2, регистры 10, 12, триггер 11, элементы И 13, 14, дешифратор 15, элемент НЕ 16, элемент ИЛИ 17 и блок 18 коммутации, введены запоминающие блоки 8, 9, блок 4 управления считыванием, блоки 5, 6 элементов ИЛИ, блок 7 управления сдвигом. Помехи формируются путем замыкания ключей в блоке 18 по программе, заносимой в запоминающие блоки 8, 9 с помощью блока 3. Блок 8 обеспечивает формирование помех, длительность которых составляет целое число периодов питающего напряжения, подаваемого на шину 20. Блок 9 обеспечивает формирование помех, длительность которых существенно меньше периода питающего напряжения. 2 з.п. ф-лы, 12 ил.

валов и кратковременных помех первич- JQ блока 8 соединен с первым входом пер

нон сети электропитания.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности генерировать помехи и импульсы специальной формы, в частности помехи с различными амплитудами и длительностями.

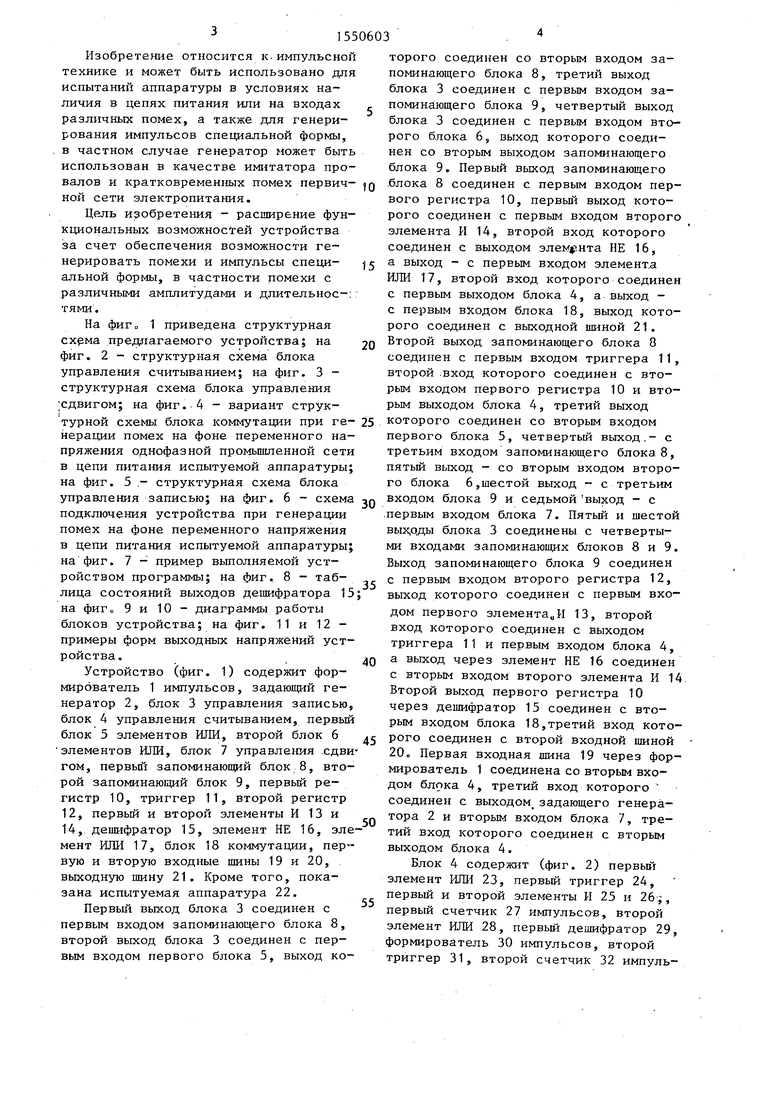

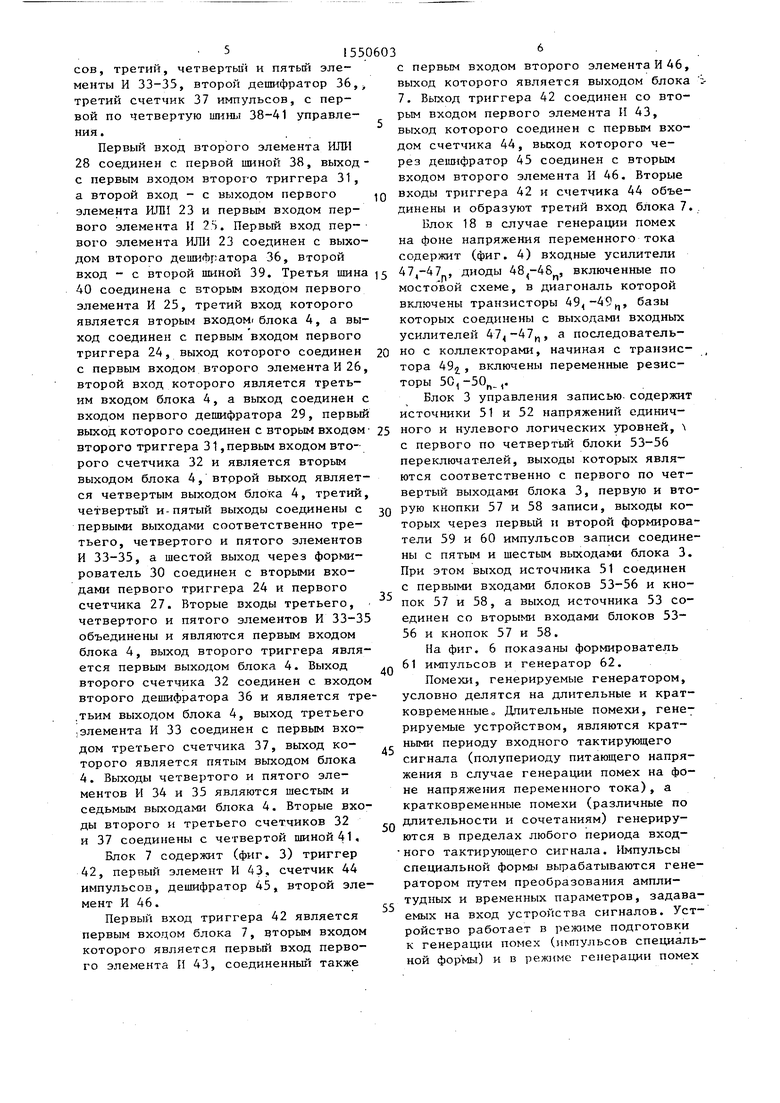

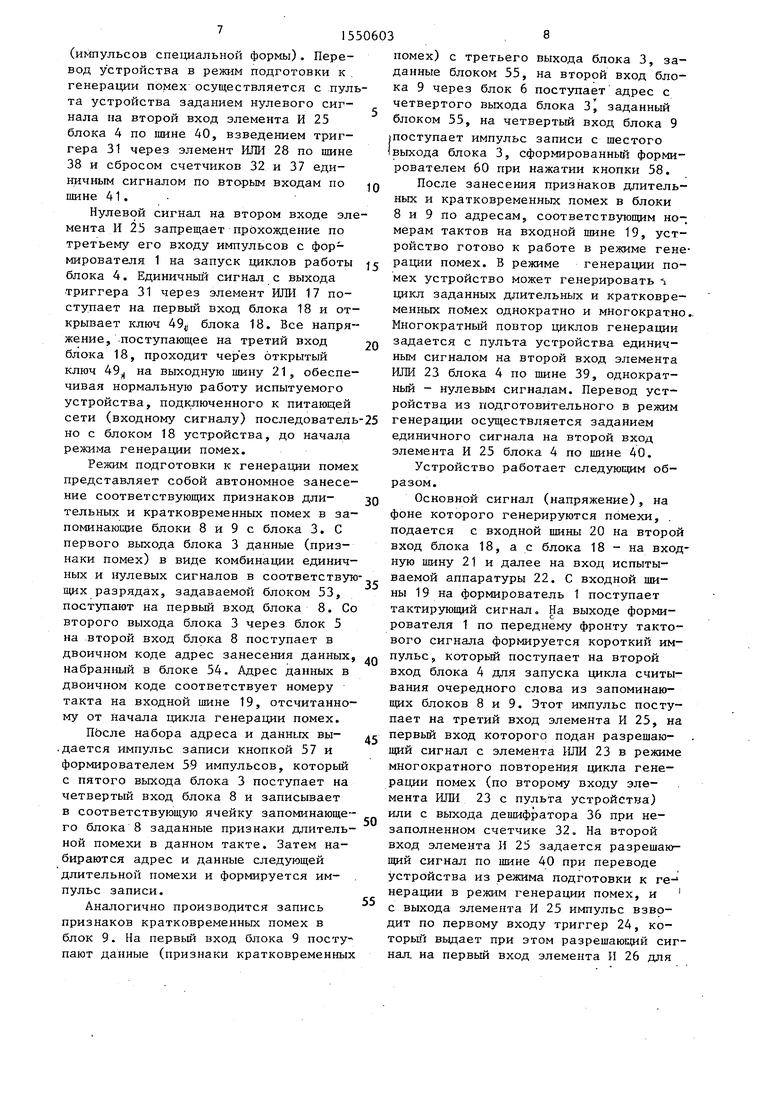

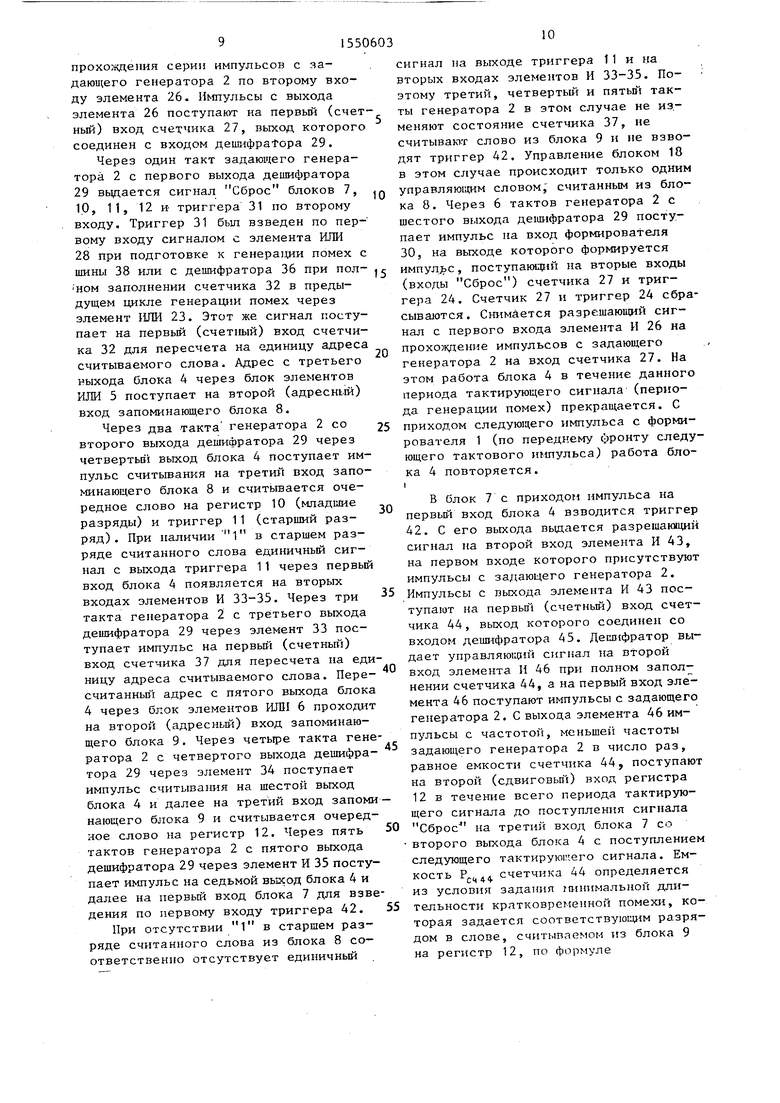

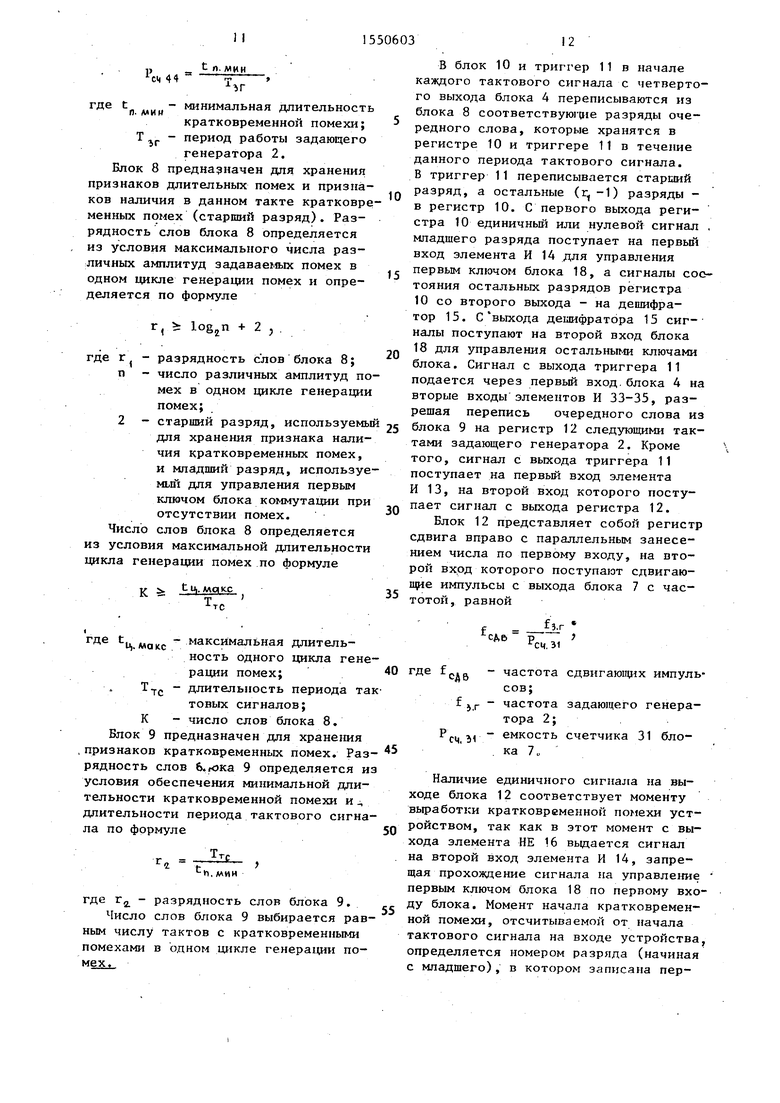

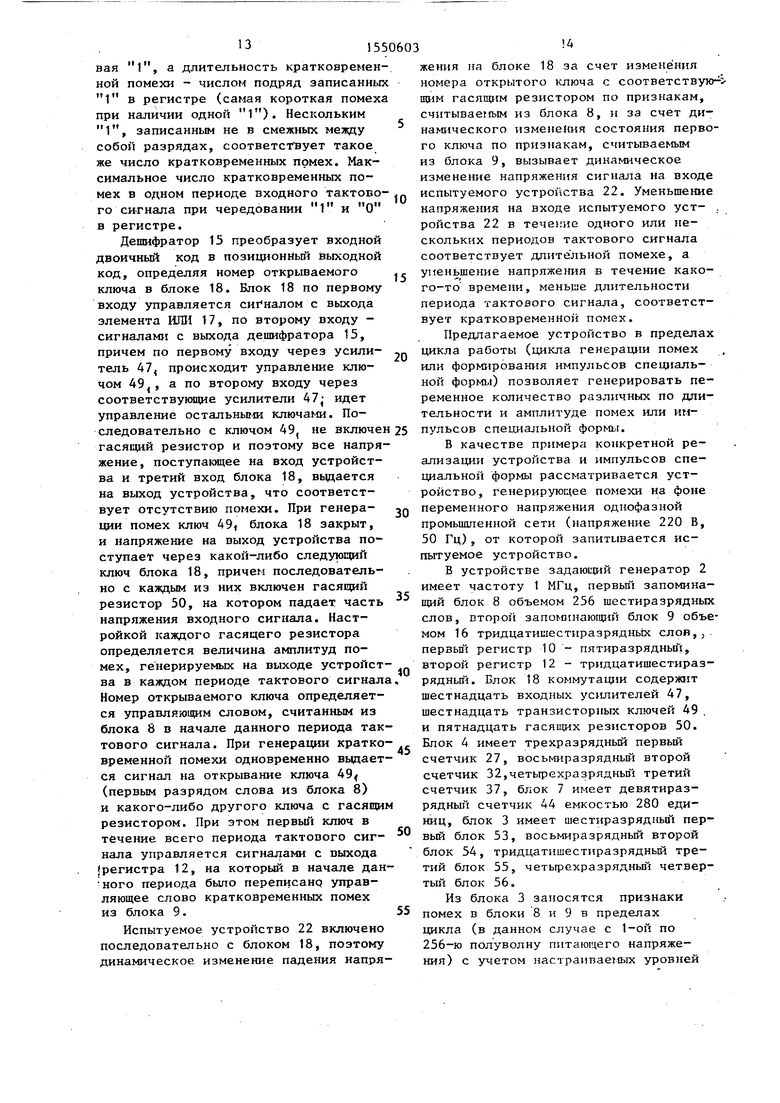

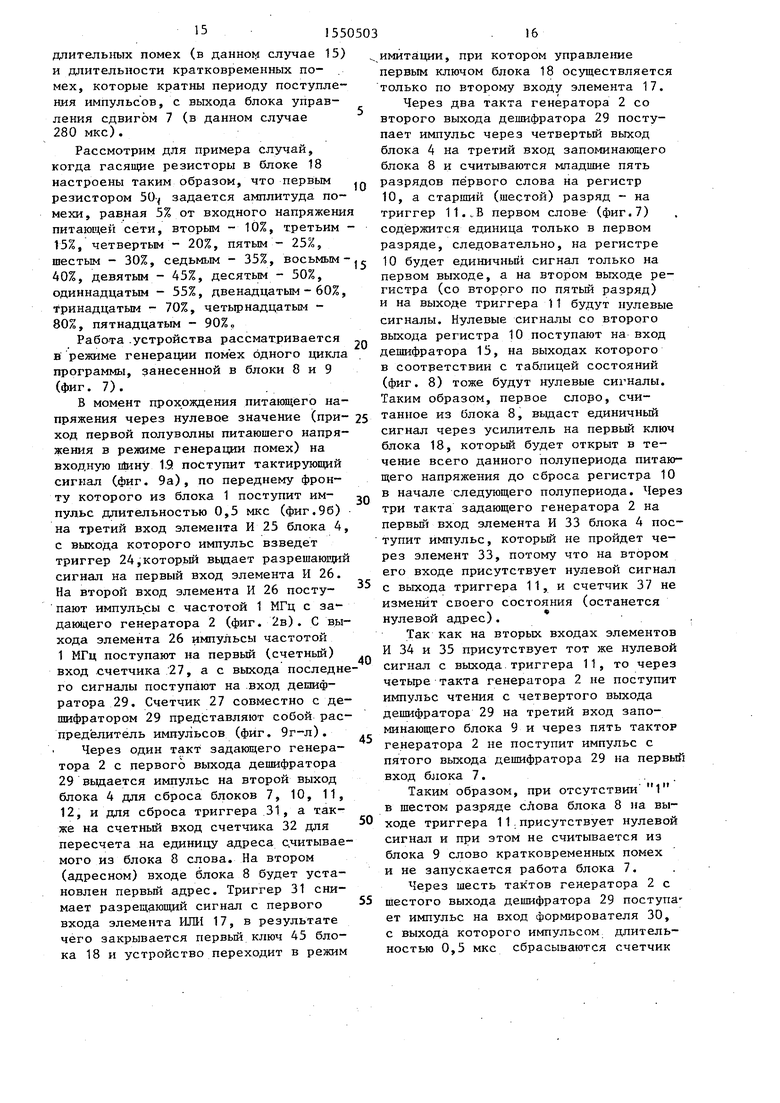

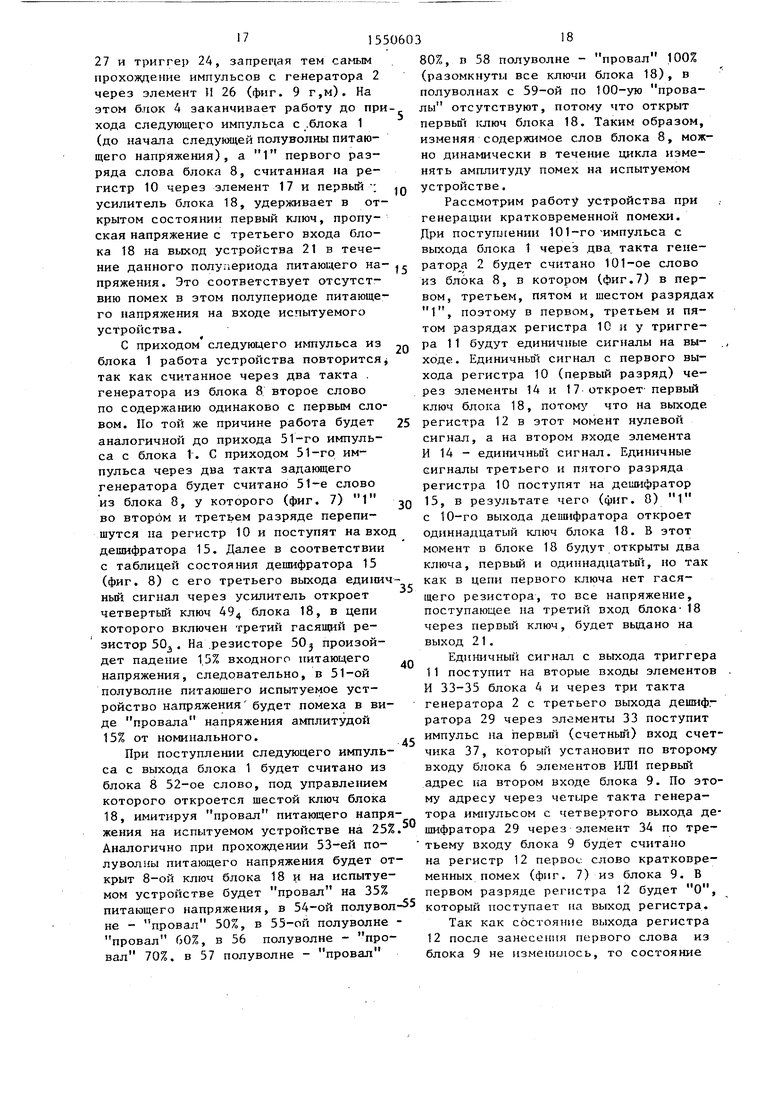

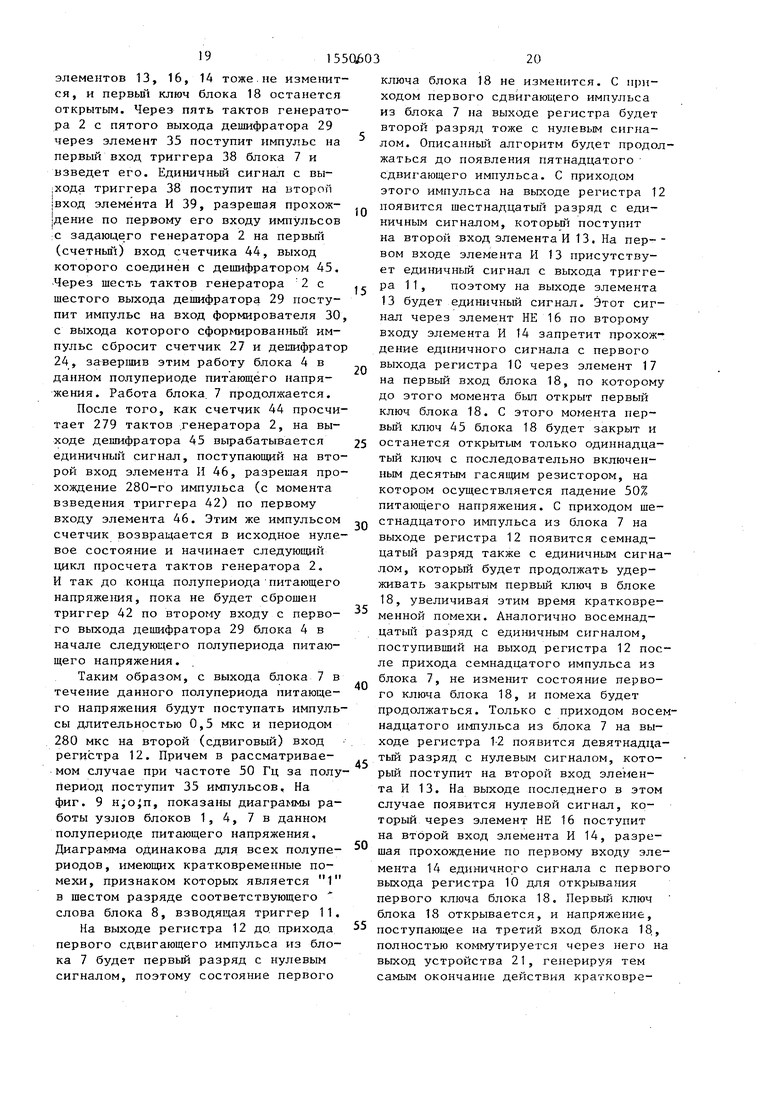

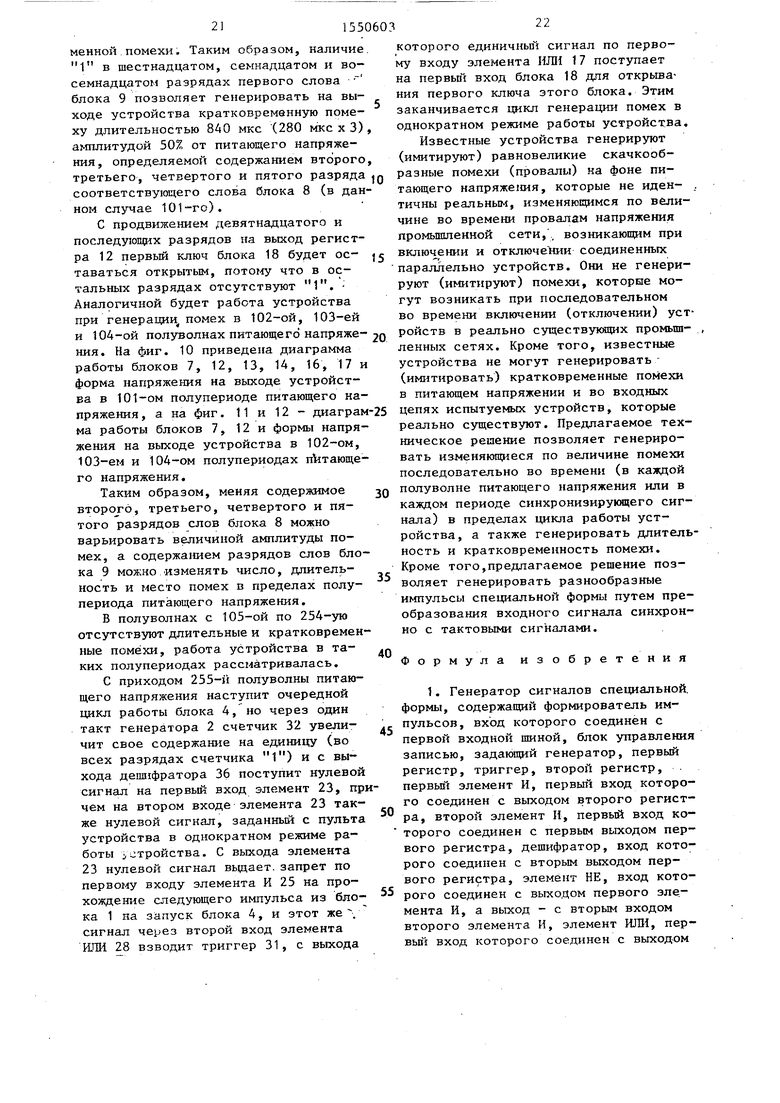

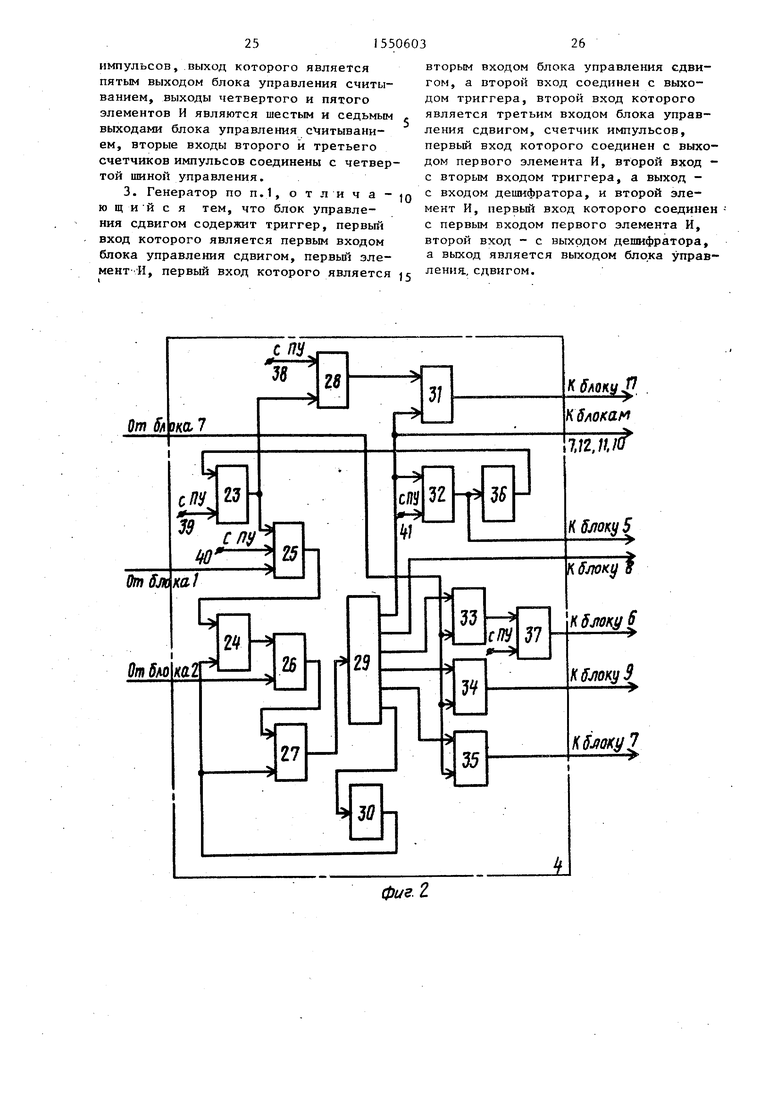

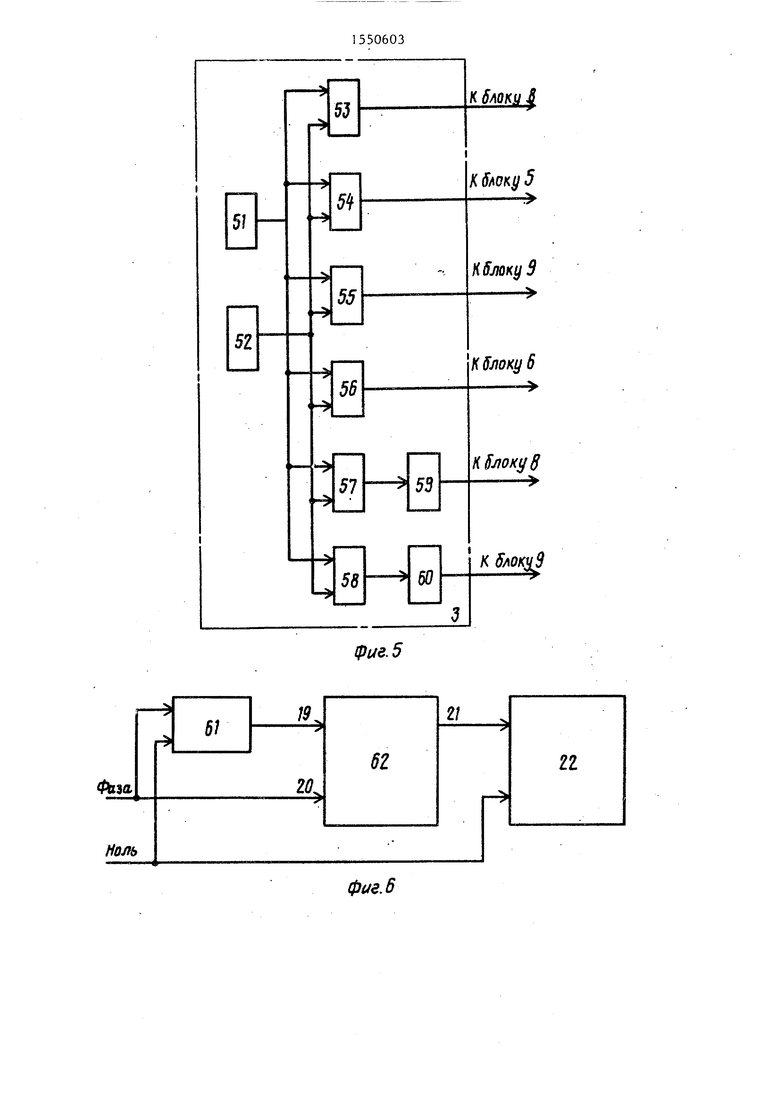

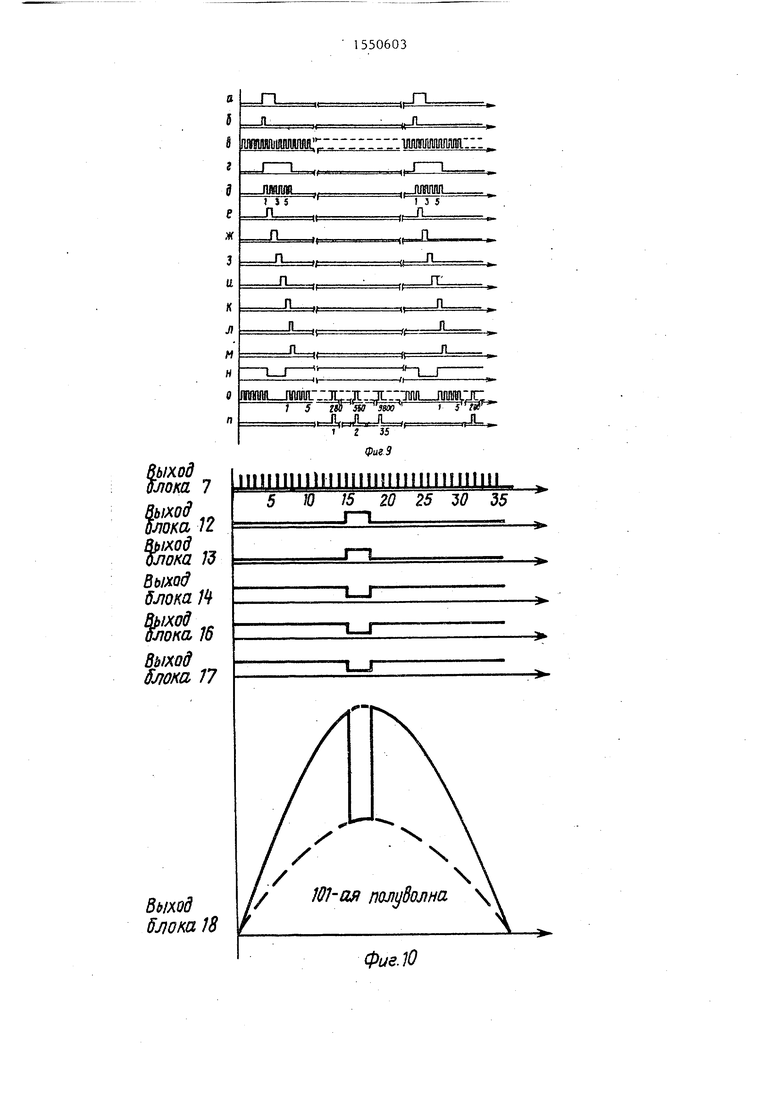

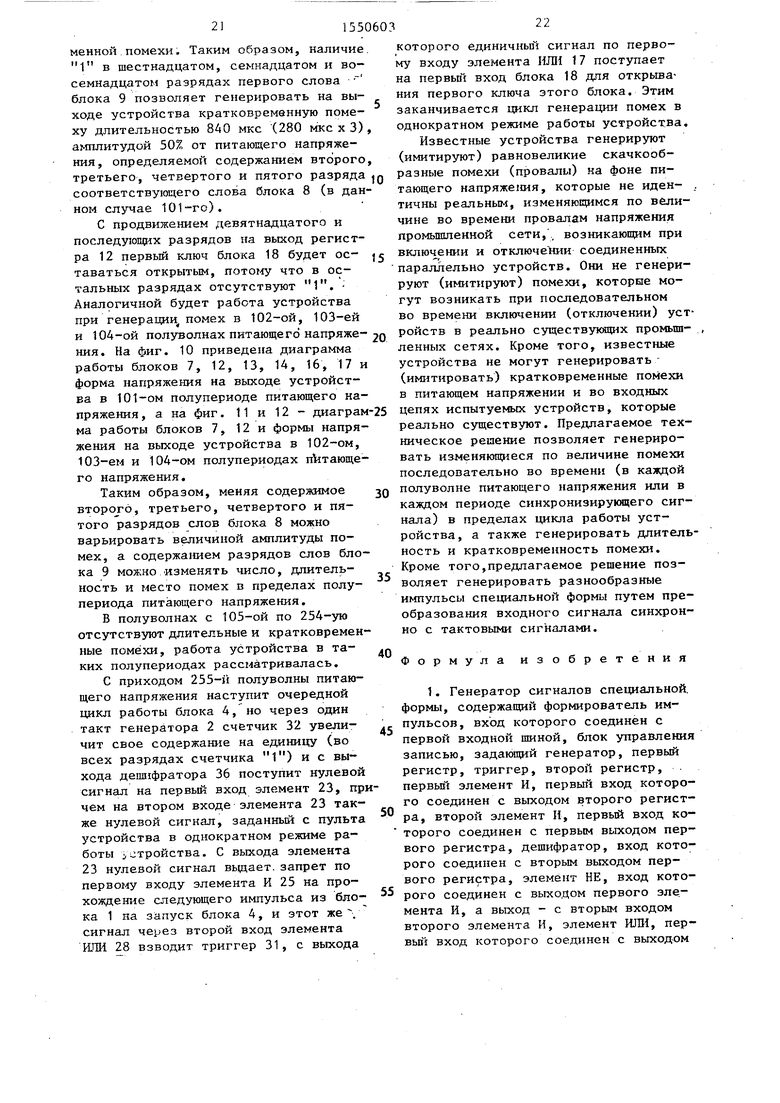

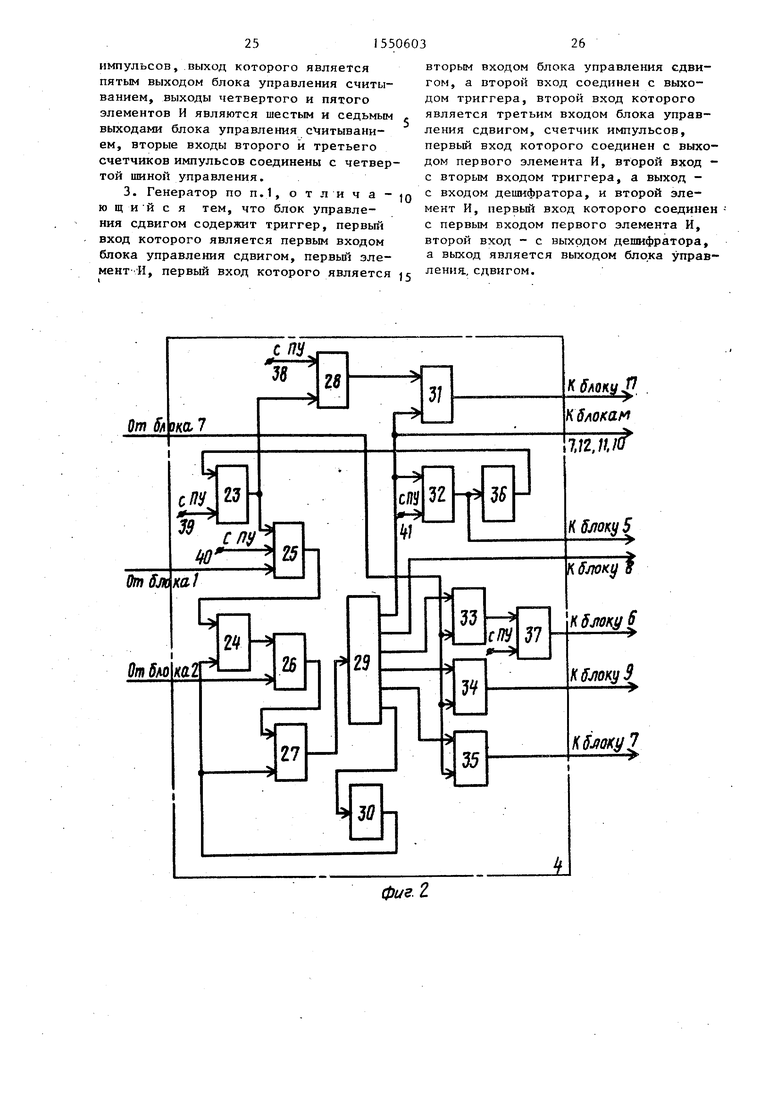

На фиг о 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока управления считыванием; на фиг. 3 - структурная схема блока управления сдвигом; на фиг. 4 - вариант струк- турной схемы блока коммутации при ге- нерации помех на фоне переменного напряжения однофазной промышленной сети в цепи питания испытуемой аппаратуры; на фиг. 5 - структурная схема блока управления записью; на фиг. 6 - схема подключения устройства при генерации помех на фоне переменного напряжения в цепи питания испытуемой аппаратуры; на фиг. 7 - пример выполняемой устройством программы; на фиг. 8 - таблица состояний выходов дешифратора 15 на фиг о 9 и 10 - диаграммы работы блоков устройства; на фиг. 11 и 12 - примеры форм выходных напряжений устройства.

Устройство (фиг. 1) содержит формирователь 1 импульсов, задающий генератор 2, блок 3 управления записью, блок 4 управления считыванием, первый блок 5 элементов ИЛИ, второй блок 6

элементов ИЛИ, блок 7 управления сдвигом, первый запоминающий блок 8, второй запоминающий блок 9, первый регистр 10, триггер 11, второй регистр 12, первый и второй элементы И 13 и 14, дешифратор 15, элемент НЕ 16, элемент ИЛИ 17, блок 18 коммутации, первую и вторую входные шины 19 и 20, выходную шину 21. Кроме того, показана испытуемая аппаратура 22.

Первый выход блока 3 соединен с первым входом запоминающего блока 8, второй выход блока 3 соединен с первым входом первого блока 5, выход ко5

0

5

0

вого регистра 10, первый выход которого соединен с первым входом второго элемента И 14, второй вход которого соединен с выходом элемента НЕ 16, а выход - с первым входом элемента ИЛИ 17, второй вход которого соединен с первым выходом блока 4, а выход - с первым входом блока 18, выход которого соединен с выходной шиной 21. Второй выход запоминающего блока 8 соединен с первым входом триггера 11, второй вход которого соединен с вторым входом первого регистра 10 и вторым выходом блока 4, третий выход которого соединен со вторым входом первого блока 5, четвертый выход - с третьим входом запоминающего блока 8, пятый выход - со вторым входом второго блока 6,шестой выход - с третьим входом блока 9 и седьмой выход - с первым входом блока 7. Пятый и шестой выхдцы блока 3 соединены с четвертыми входами запоминающих блоков 8 и 9. Выход запоминающего блока 9 соединен с первым входом второго регистра 12, выход которого соединен с первым входом первого элементами 13, второй вход которого соединен с выходом триггера 11 и первым входом блока 4, а выход через элемент НЕ 16 соединен с вторым входом второго элемента И 14 Второй выход первого регистра 10 через дешифратор 15 соединен с вторым входом блока 18,третий вход которого соединен с второй входной шиной 20„ Первая входная шина 19 через формирователь 1 соединена со вторым входом блока 4, третий вход которого соединен с выходом, задающего генератора 2 и вторым входом блока 7, третий вход которого соединен с вторым выходом блока 4.

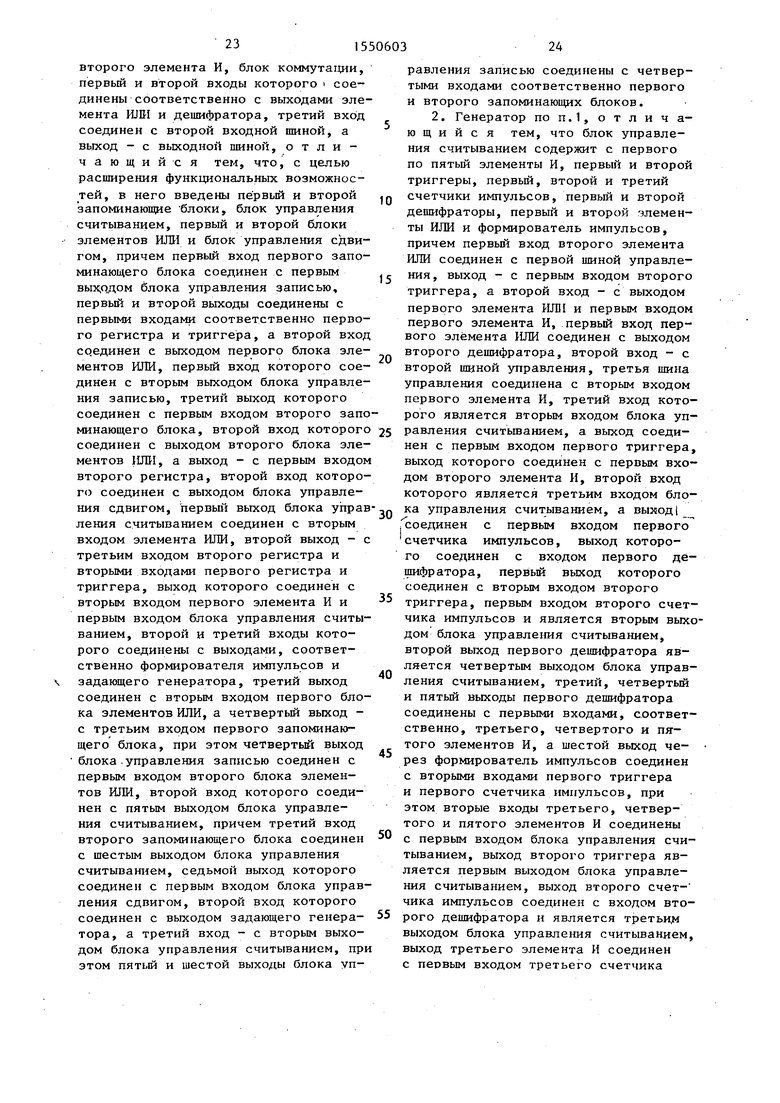

Блок 4 содержит (фиг. 2) первый элемент ИЛИ 23, первый триггер 24, первый и второй элементы И 25 и 26;, первый счетчик 27 импульсов, второй элемент ИЛИ 28, первый дешифратор 29, формирователь 30 импульсов, второй триггер 31, второй счетчик 32 импуль5

0

5

0

сов, третий, четвертый и пятый элементы И 33-35, второй дешифратор 36,, третий счетчик 37 импульсов, с первой по четвертую шины 38-41 управления.

Первый вход второго элемента ИЛИ 28 соединен с первой шиной 38, выход - с первым входом второго триггера 31, а второй вход - с выходом первого элемента ИЛИ 23 и первым входом первого элемента И 2S. Первый вход первого элемента ИЛИ 23 соединен с выходом второго дешифратора 36, второй

вход - с второй шиной 39. Третья шина 55 47,-47 , диоды , включенные по

40 соединена с вторым входом первого элемента И 25, третий вход которого является вторым входом блока 4, а выход соединен с первым входом первого триггера 24, выход которого соединен с первым входом второго элемента И 26, второй вход которого является третьим входом блока 4, а выход соединен с входом первого дешифратора 29, первый

мостовой схеме

, в диагональ которой базы

20

включены транзисторы , которых соединены с выходами входных усилителей 474-47п, а последовательно с коллекторами, начиная с транзистора 49, включены переменные резисторы 50,-50П .

Блок 3 управления записью, содержит источники 51 и 52 напряжений единич- выход которого соединен с вторым входом 25 ного и нулевого логических уровней, второго триггера 31, первым входом вто- с первого по четвертый блоки 53-56

рого счетчика 32 и является вторым выходом блока 4, втррой выход является четвертым выходом блока 4, третий, четвертый и-пятый выходы соединены с первыми выходами соответственно третьего, четвертого и пятого элементов И 33-35, а шестой выход через формирователь 30 соединен с вторыми входами первого триггера 24 и первого счетчика 27. Вторые входы третьего, четвертого и пятого элементов И 33-35 объединены и являются первым входом блока 4, выход второго триггера является первым выходом блока 4. Выход второго счетчика 32 соединен с входом второго дешифратора 36 и является тре .тьим выходом блока 4, выход третьего :элемента И 33 соединен с первым входом третьего счетчика 37, выход которого является пятым выходом блока 4. Выходы четвертого и пятого элементов И 34 и 35 являются шестым и седьмым выходами блока 4. Вторые входы второго и третьего счетчиков 32 и 37 соединены с четвертой шиной 41,

Блок 7 содержит (фиг. 3) триггер 42, первый элемент И 43, счетчик 44 импульсов, дешифратор 45 второй элемент И 46.

Первый вход триггера 42 является первым входом блока 7, в,торым входом которого является первый вход первого элемента И 43, соединенный также

с первым входом второго элемента И 46, выход которого является выходом блока 7. Выход триггера 42 соединен со вторым входом первого элемента И 43, выход которого соединен с первым входом счетчика 44, выход которого через дешифратор 45 соединен с вторым входом второго элемента И 46. Вторые входы триггера 42 и счетчика 44 объединены и образуют третий вход блока 7.

Блок 18 в случае генерации помех на фоне напряжения переменного тока содержит (фиг. 4) входные усилители

мостовой схеме

, в диагональ которой базы

включены транзисторы , которых соединены с выходами входных усилителей 474-47п, а последовательно с коллекторами, начиная с транзис тора 49, включены переменные резисторы 50,-50П .

0

5

5

0

5

переключателей, выходы которых являются соответственно с первого по четвертый выходами блока 3, первую и вторую кнопки 57 и 58 записи, выходы которых через первый и второй формирователи 59 и 60 импульсов записи соединены с пятым и шестым выходами блока 3. При этом выход источника 51 соединен с первыми входами блоков 53-56 и кнопок 57 и 58, а выход источника 53 соединен со вторыми входами блоков 53- 56 и кнопок 57 и 58.

На фиг. 6 показаны формирователь 61 импульсов и генератор 62.

Помехи, генерируемые генератором, условно делятся на длительные и кратковременные Длительные помехи, генерируемые устройством, являются кратными периоду входного тактирующего сигнала (полупериоду питающего напряжения в случае генерации помех на фоне напряжения переменного тока), а кратковременные помехи (различные по длительности и сочетаниям) генерируются в пределах любого периода входного тактирующего сигнала. Импульсы специальной формы вырабатываются генератором путем преобразования амплитудных и временных параметров, задаваемых на вход устройства сигналов. Устройство работает в режиме подготовки к генерации помех (импульсов специальной фор мы) и в режиме генерации помех

(импульсов специальной формы). Перевод устройства в режим подготовки к генерации помех осуществляется с пульта устройства заданием нулевого сигнала на второй вход элемента И 25 блока 4 по шине 40, взведением триггера 31 через элемент ИЛИ 28 по шине 38 и сбросом счетчиков 32 и 37 единичным сигналом по вторым входам по шине 41.

Нулевой сигнал на втором входе элемента И 25 запрещает прохождение по третьему его входу импульсов с формирователя 1 на запуск циклов работы блока 4. Единичный сигнал с выхода триггера 31 через элемент ИЛИ 17 поступает на первый вход блока 18 и открывает ключ 49, блока 18. Все напряжение, поступающее на третий вход блока 18, проходит через открытый ключ 49 на выходную шину 21, обеспечивая нормальную работу испытуемого устройства, подключенного к питающей сети (входному сигналу) последователь но с блоком 18 устройства, до начала режима генерации помех.

Режим подготовки к генерации помех представляет собой автономное занесение соответствующих признаков длительных и кратковременных помех в запоминающие блоки 8 и 9 с блока 3. С первого выхода блока 3 данные (признаки помех) в виде комбинации единичных и нулевых сигналов в соответствующих разрядах, задаваемой блоком 53, поступают на первый вход блока 8. Со второго выхода блока 3 через блок 5 на второй вход блока 8 поступает в двоичном коде адрес занесения данных, набранный в блоке 54. Адрес данных в двоичном коде соответствует номеру такта на входной шине 19, отсчитанному от начала цикла генерации помех.

После набора адреса и данных вы- ,дается импульс записи кнопкой 57 и формирователем 59 импульсов, который с пятого выхода блока 3 поступает на четвертый вход блока 8 и записывает в соответствующую ячейку запоминающего блока 8 заданные признаки длительной помехи в данном такте. Затем набираются адрес и данные следующей длительной помехи и формируется импульс записи.

Аналогично производится запись признаков кратковременных помех в блок 9. На первый вход блока 9 поступают данные (признаки кратковременных

0

5

0 5

0

5

0

5

0

5

помех) с третьего выхода блока 3, заданные блоком 55, на второй вход блока 9 через блок 6 поступает адрес с четвертого выхода блока Ъ заданный блоком 55, на четвертый вход блока 9 шоступает импульс записи с шестого Iвыхода блока 3, сформированный формирователем 60 при нажатии кнопки 58.

После занесения признаков длительных и кратковременных помех в блоки 8 и 9 по адресам, соответствующим номерам тактов на входной шине 19, устройство готово к работе в режиме генерации помех. В режиме генерации помех устройство может генерировать цикл заданных длительных и кратковременных помех однократно и многократно. Многократный повтор циклов генерации задается с пульта устройства единичным сигналом на второй вход элемента ИЛИ 23 блока 4 по шине 39, однократный - нулевым сигналам. Перевод устройства из подготовительного в режим генерации осуществляется заданием единичного сигнала на второй вход элемента И 25 блока 4 по шине 40.

Устройство работает следующим образом.

Основной сигнал (напряжение), на фоне которого генерируются помехи, подается с входной шины 20 на второй вход блока 18, ас блока 18 - на входную шину 21 и далее на вход испытываемой аппаратуры 22. С входной шины 19 на формирователь 1 поступает тактирующий сигнал. На выходе формирователя 1 по переднему фронту тактового сигнала формируется короткий импульс, который поступает на второй вход блока 4 для запуска цикла считывания очередного слова из запоминающих блоков 8 и 9. Этот импульс поступает на третий вход элемента И 25, на первый вход которого подан разрешающий сигнал с элемента ИЛИ 23 в режиме многократного повторения цикла генерации помех (по второму входу элемента ИЛИ 23 с пульта устройства) или с выхода дешифратора 36 при незаполненном счетчике 32. На второй вход элемента И 25 задается разрешающий сигнал по шине 40 при переводе устройства из режима подготовки к ге-1 нерации в режим генерации помех, и с выхода элемента И 25 импульс взводит по первому входу триггер 24, который выдает при этом разрешающий сигнал на первый вход элемента И 26 для

у1550

прохождения серии импульсов с задающего генератора 2 по второму входу элемента 26. Импульсы с выхода элемента 26 поступают на первый (счетный) вход счетчика 27, выход которого соединен с входом дешифратора 29.

Через один такт задающего генератора 2 с первого выхода дешифратора 29 выдается сигнал Сброс блоков 7, 10, 11, 12 и триггера 31 по второму входу. Триггер 31 был взведен по первому входу сигналом с элемента ИЛИ 28 при подготовке к генерации помех с шины 38 или с дешифратора 36 при пол- ном заполнении счетчика 32 в предыдущем цикле генерации помех через элемент ИЛИ 23. Этот же сигнал поступает на первый (счетный) вход счетчика 32 для пересчета на единицу адреса считываемого слова. Адрес с третьего ныхода блока 4 через блок элементов ИЛИ 5 поступает на второй (адресный) вход запоминающего блока 8.

Через два такта генератора 2 со второго выхода дешифратора 29 через четвертый выход блока 4 поступает импульс считывания на третий вход запоминающего блока 8 и считывается очередное слово на регистр 10 (младшие разряды) и триггер 11 (старший разряд) . При наличии в старшем разряде считанного слова единичный сигнал с выхода триггера 11 через первый вход блока 4 появляется на вторых входах элементов И 33-35. Через три такта генератора 2 с третьего выхода дешифратора 29 через элемент 33 поступает импульс на первый (счетный) вход счетчика 37 для пересчета на единицу адреса считываемого слова. Пере- считанный адрес с пятого выхода блока 4 через блок элементов ИЛИ 6 проходит на второй (адресный) вход запоминающего блока 9. Через четыре такта генератора 2 с четвертого выхода дешифратора 29 через элемент 34 поступает импульс считывания на шестой выход блока 4 и далее на третий вход запоми нающего блока 9 и считывается очередное слово на регистр 12. Через пять тактов генератора 2 с пятого выхода дешифратора 29 через элемент И 35 поступает импульс на седьмой выход блока 4 и далее на первый вход блока 7 для взведения по первому входу триггера 42.

При отсутствии 1 в старшем разряде считанного слова из блока 8 соответственно отсутствует единичный

-

5 5 0 5

0

10

сигнал на выходе триггера 11 и на вторых входах элементов И 33-35. Поэтому третий, четвертый и пятый такты генератора 2 в этом случае не изменяют состояние счетчика 37, не считывают слово из блока 9 и не взводят триггер 42. Управление блоком 18 в этом случае происходит только одним управляющим словом, считанным из блока 8. Через 6 тактов генератора 2 с шестого выхода дешифратора 29 поступает импульс на вход формирователя 30, на выходе которого формируется импульс, поступающий на вторые входы (входы Сброс) счетчика 27 и трИ1- гера 24, Счетчик 27 и триггер 24 сбрасываются. Снимается разрешающий сигнал с первого входа элемента И 26 на прохождение импульсов с задающего генератора 2 на вход счетчика 27. На этом работа блока 4 в течение данного периода тактирующего сигнала (периода генерации помех) прекращается. С приходом следующего импульса с формирователя 1 (по переднему фронту следующего тактового импульса) работа блока 4 повторяется, i

В блок 7 с приходом импульса на первый вход блока 4 взводится триггер 42. С его выхода выдается разрешающий сигнал на второй вход элемента И 43, на первом входе которого присутствуют импульсы с задающего генератора 2. Импульсы с выхода элемента И 43 поступают на первый (счетный) вход счетчика 44, выход которого соединен со входом дешифратора 45. Дешифратор выдает управляющий сигнал на второй вход элемента И 46 при полном заполнении счетчика 44, а на первый вход элемента 46 поступают импульсы с задающего генератора 2. С выхода элемента 46 импульсы с частотой, меньшей частоты задающего генератора 2 в число раз, равное емкости счетчика 44, поступают на второй (сдвиговый) вход регистра 12 в течение всего периода тактирующего сигнала до поступления сигнала Сброс на третий вход блока 7 со второго выхода блока 4 с поступлением следующего тактирующего сигнала. Емкость РСЦ44. счетчика 44 определяется из условия задания минимальной длительности кратковременной помехи, которая задается соответствующим разрядом в слове, считываемом из блока 9 на регистр 12, по формуле

1еч 44

t ft МИН,

т Ч г

где t - минимальная длительность

кратковременной помехи; Т - период работы задающего

генератора 2.

Блок 8 предназначен для хранения признаков длительных помех и признаков наличия в данном такте кратковременных помех (старший разряд). Разрядность слов блока 8 определяется из условия максимального числа различных амплитуд задаваемых помех в одном цикле генерации помех и определяется по формуле

г, Ь logzn + 2 ,

где г - разрядность слов блока 8;

п - число различных амплитуд помех в одном цикле генерации помех;

2 - старший разряд, используемы для хранения признака наличия кратковременных помех, и младший разряд, используемый для управления первым ключом блока коммутации при отсутствии помех. Число слов блока 8 определяется из условия максимальной длительности цикла генерации помех по формуле

К S:

tU. длдкс

Т

где t максимальная длительность одного цикла генерации помех;

Ттс - длительность периода тактовых сигналов; К - число слов блока 8. Блок 9 предназначен для хранения , признаков кратковременных помех. Раз- рядность слов 6.ока 9 определяется из условия обеспечения минимальной длительности кратковременной помехи и , длительности периода тактового сигнала по формуле50

г, -и, мин

где га - разрядность слов блока 9.

Число слов блока 9 выбирается равным числу тактов с кратковременными помехами в оцном цикле генерации помех

5

5

В блок 10 и триггер 11 в начале каждого тактового сигнала с четвертого выхода блока 4 переписываются из блока 8 соответствующие разряды очередного слова, которые хранятся в регистре 10 и триггере 11 в течение данного периода тактового сигнала. В триггер 11 переписывается старший разряд, а остальные (г(-1) разряды - в регистр 10. С первого выхода регистра 10 единичный или нулевой сигнал , младшего разряда поступает на первый вход элемента И 14 для управления первым ключом блока 18, а сигналы состояния остальных разрядов регистра 10 со второго выхода - на дешифратор 15. С выхода дешифратора 15 сигналы поступают на второй вход блока 18 для управления остальными ключами блока. Сигнал с выхода триггера 11 подается через первый вход блока 4 на вторые входы элементов И 33-35, разрешая перепись очередного слова из блока 9 на регистр 12 следующими тактами задающего генератора 2. Кроме того, сигнал с выхода триггера 11 поступает на первый вход элемента И 13, на второй вход которого поступает сигнал с выхода регистра 12.

Блок 12 представляет собой регистр сдвига вправо с параллельным занесением числа по первому входу, на второй вход которого поступают сдвигающие импульсы с выхода блока 7 с частотой , равной

fj.r

-CAB

ГСЧ 31

где f

сдв

f

S.r

CM, 31

частота сдвигающих импульсов;

частота задающего генератора 2;

емкость счетчика 31 блока 7„

Наличие единичного сигнала на выходе блока 12 соответствует моменту выработки кратковременной помехи устройством, так как в этот момент с выхода элемента НЕ 16 выдается сигнал на второй вход элемента И 14, запрещая прохождение сигнала на управление первым ключом блока 18 по первому входу блока. Момент начала кратковременной помехи, отсчитываемой от начала тактового сигнала на входе устройства, определяется номером разряда (начиная с младшего), в котором записана пер1315506

вая 1, а длительность кратковременной помехи - числом подряд записанных 1 в регистре (самая короткая помеха при наличии одной 1). Нескольким 111, записанным не в смежных между собой разрядах, соответствует такое же число кратковременных помех. Максимальное число кратковременных помех в одном периоде входного тактового си-гнала при чередовании 1 и О в регистре.

Дешифратор 15 преобразует входной двоичный код в позиционный выходной код, определяя номер открываемого ключа в блоке 18. Блок 18 по первому входу управляется сигналом с выхода элемента ИЛИ 17, по второму входу - сигналами с выхода дешифратора 15, причем по первому входу через усилитель 47, происходит управление клю10

15

20

чом 49t, а по второму входу через соответствующие усилители 47j идет управление остальными ключами. Последовательно с ключом 49( не включен гасящий резистор и поэтому все напряжение, поступающее на вход устройства и третий вход блока 18, выдается на выход устройства, что соответствует отсутствию помехи. При генерации помех ключ 49, блока 18 закрыт, и напряжение на выход устройства поступает через какой-либо следующий ключ блока 18, причем последовательно с каждым из них включен гасящий резистор 50, на котором падает часть напряжения входного сигнала. Настройкой каждого гасящего резистора определяется величина амплитуд помех, генерируемых на выходе устройства в каждом периоде тактового сигнала Номер открываемого ключа определяется управляющим словом, считанным из блока 8 в начале данного периода тактового сигнала. При генерации кратко- временной помехи одновременно выдается сигнал на открывание ключа 49 (первым разрядом слова из блока 8) и какого-либо другого ключа с гасящим резистором. При этом первый ключ в течение всего периода тактового сиг нала управляется сигналами с выхода {регистра 12, на который в начале дан- ного периода было переписано управляющее слово кратковременных помех из блока 9.

Испытуемое устройство 22 включено последовательно с блоком 18, поэтому динамическое изменение падения напря

„.

4

жения на блоке 18 за счет изменения номера открытого ключа с соответствую- щим гасящим резистором по признакам, считываемым из блока 8, и за счет динамического изменения состояния перво

10

15

20

30

35

40

50

55

го ключа по признакам, считываемым из блока 9, вызывает динамическое изменение напряжения сигнала на входе испытуемого устройства 22. Уменьшение напряжения на входе испытуемого уст- . ройства 22 в течение одного или нескольких периодов тактового сигнала соответствует длительной помехе, а уменьшение напряжения в течение какого-то времени, меньше длительности периода тактового сигнала, соответствует кратковременной помех.

Предлагаемое устройство в пределах цикла работы (цикла генерации помех или формирования импульсов специальной формы) позволяет генерировать переменное количество различных по длительности и амплитуде помех или импульсов специальной формы.

В качестве примера конкретной реализации устройства и импульсов специальной формы рассматривается устройство, генерирующее помехи на фоне переменного напряжения однофазной промышленной сети (напряжение 220 В, 50 Гц), от которой запитывается испытуемое устройство.

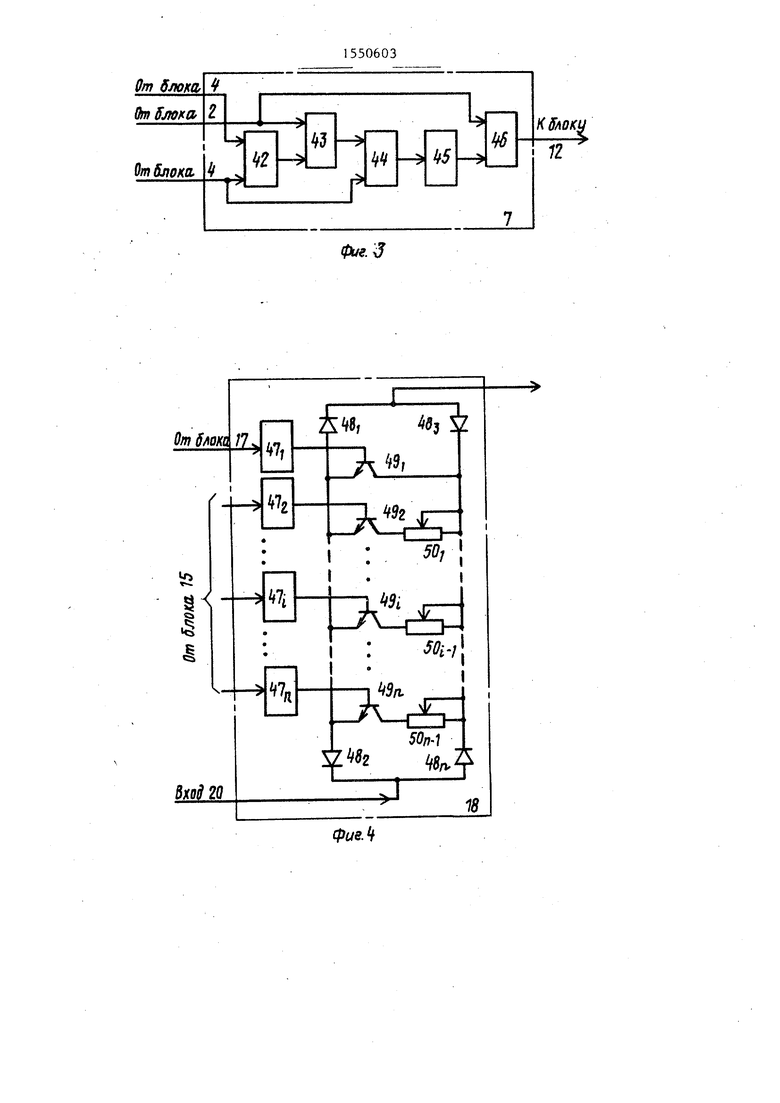

В устройстве задающий генератор 2 имеет частоту 1 МГц, первый запомина- щий блок 8 объемом 256 шестиразрядных слов, второй запоминающий блок 9 объемом 16 тридцатишестиразрядных слов,, первый регистр 10 - пятиразрядный, второй регистр 12 - тридцатишестиразрядный. Блок 18 коммутации содержит шестнадцать входных усилителей 47, шестнадцать транзисторных ключей 49 и пятнадцать гасящих резисторов 50. Блок 4 имеет трехразрядный первый счетчик 27, восьмиразрядный второй счетчик 32,четырехразрядный третий счетчик 37, блок 7 имеет девятиразрядный счетчик 44 емкостью 280 единиц, блок 3 имеет шестиразрядный первый блок 53, восьмиразрядный второй блок 54, тридцатишестнразрядный третий блок 55, четырехразрядный четвертый блок 56.

Из блока 3 заносятся признаки помех в блоки 8 и 9 в пределах цикла (в данном случае с 1-ой по 256-ю полуволну питающего напряжения) с учетом настраиваемых уровней

15155

длительных помех (в данное случае 15) и длительности кратковременных помех, которые кратны периоду поступления импульсов, с выхода блока управления сдвигом 7 (в данном случае 280 мкс).

Рассмотрим для примера случай, когда гасящие резисторы в блоке 18 настроены таким образом, что первым

резистором 50-, задается амплитуда поЧерез два такта генератора 2 со второго выхода дешифратора 29 поступает импульс через четвертый выход блока 4 на третий вход запоминающего блока 8 и считываются младшие пять разрядов первого слова на регистр 10, а старший (шестой) разряд - на триггер 11.„В первом слове (фиг.7) содержится единица только в первом разряде, следовательно, на регистре

мехи, равная 5% от входного напряжения

питающей сети, вторым - 10%, третьим 15%, четвертым - 20%, пятым - 25%,

шестым - 30%, седьмым - 35%, восьмым- ю будет единичный сигнал только на

40%, девятым - 45%, десятым - 50%,

одиннадцатым - 55%, двенадцатым - 60%,

тринадцатым - 70%, четырнадцатым 80%, пятнадцатым - 90%„

Работа .устройства рассматривается в режиме генерации помех одного цикла программы, занесенной в блоки 8 и 9 (фиг. 7).

В момент прохождения питающего на20

первом выходе, а на втором выходе ре гистра (со второго по пятый разряд) и на выходе триггера 11 будут нулевы сигналы. Нулевые сигналы со второго выхода регистра 10 поступают на вход дешифратора 15, на выходах которого в соответствии с таблицей состояний (фиг. 8) тоже будут нулевые сигналы. Таким образом, первое слово, счи30

35

40

пряжения через нулевое значение (при- 25 танное из блока 8, выдаст единичный ход первой полуволны питаюшего напряжения в режиме генерации помех) на входную шину 1.9 поступит тактирующий сигнал (фиг. 9а), по переднему фронту которого из блока 1 поступит импульс длительностью 0,5 мкс (фиг.96) на третий вход элемента И 25 блока 4, с выхода которого импульс взведет триггер 24,который выдает разрешающий сигнал на первый вход элемента И 26. На второй вход элемента И 26 поступают импульсы с частотой 1 МГц с за дающего генератора 2 (фиг. 2в). С выхода элемента 26 импульсы частотой 1 МГц поступают на первый (счетный) вход счетчика 27, ас выхода последнего сигналы поступают на вход дешифратора 29. Счетчик 27 совместно с дешифратором 29 представляют собой распределитель импульсов (фиг. 9г-л).

Через один такт задающего генератора 2 с первого выхода дешифратора 29 выдается импульс на второй выход блока 4 для сброса блоков 7, 10, 11, 12, и для сброса триггера 31, а также на счетный вход счетчика 32 для пересчета на единицу адреса учитываемого из блока 8 слова. На втором (адресном) входе блока 8 будет установлен первый адрес. Триггер 31 снимает разрещающий сигнал с первого входа элемента ИЛИ 17, в результате чего закрывается первый ключ 45 блока 18 и устройство переходит в режим

45

50

55

сигнал через усилитель на первый клю блока 18, который будет открыт в течение всего данного полупериода пита щего напряжения до сброса регистра 1 в начале следующего полупериода. Чер три такта задающего генератора 2 на первый вход элемента И 33 блока 4 по тупит импульс, который не пройдет че рез элемент 33, потому что на втором его входе присутствует нулевой сигна с выхода триггера 11, и счетчик 37 н изменит своего состояния (останется нулевой адрес).

Так как на вторых входах элементо И 34 и 35 присутствует тот же нулево сигнал с выхода триггера 11, то чере четыре такта генератора 2 не поступи импульс чтения с четвертого выхода дешифратора 29 на третий вход запоминающего блока 9 и через пять такто генератора 2 не поступит импульс с пятого выхода дешифратора 29 на перв вход блока 7.

Таким образом, при отсутствии в шестом разряде слова блока 8 на вы ходе триггера 11 присутствует нулево сигнал и при этом не считывается из блока 9 слово кратковременных помех и не запускается работа блока 7.

Через шесть тактов генератора 2 с шестого выхода дешифратора 29 поступ ет импульс на вход формирователя 30, с выхода которого импульсом длитель ностью 0,5 мкс сбрасываются счетчик

16

имитации, при котором управление первым ключом блока 18 осуществляется только по второму входу элемента 17.

Через два такта генератора 2 со второго выхода дешифратора 29 поступает импульс через четвертый выход блока 4 на третий вход запоминающего блока 8 и считываются младшие пять разрядов первого слова на регистр 10, а старший (шестой) разряд - на триггер 11.„В первом слове (фиг.7) содержится единица только в первом разряде, следовательно, на регистре

ю будет единичный сигнал только на

0

первом выходе, а на втором выходе регистра (со второго по пятый разряд) и на выходе триггера 11 будут нулевые сигналы. Нулевые сигналы со второго выхода регистра 10 поступают на вход дешифратора 15, на выходах которого в соответствии с таблицей состояний (фиг. 8) тоже будут нулевые сигналы. Таким образом, первое слово, счи0

5

0

5 танное из блока 8, выдаст единичный

5

0

5

сигнал через усилитель на первый ключ блока 18, который будет открыт в течение всего данного полупериода питающего напряжения до сброса регистра 10 в начале следующего полупериода. Через три такта задающего генератора 2 на первый вход элемента И 33 блока 4 поступит импульс, который не пройдет через элемент 33, потому что на втором его входе присутствует нулевой сигнал с выхода триггера 11, и счетчик 37 не изменит своего состояния (останется нулевой адрес).

Так как на вторых входах элементов И 34 и 35 присутствует тот же нулевой сигнал с выхода триггера 11, то через четыре такта генератора 2 не поступит импульс чтения с четвертого выхода дешифратора 29 на третий вход запоминающего блока 9 и через пять тактов генератора 2 не поступит импульс с пятого выхода дешифратора 29 на первый вход блока 7.

Таким образом, при отсутствии в шестом разряде слова блока 8 на выходе триггера 11 присутствует нулевой сигнал и при этом не считывается из блока 9 слово кратковременных помех и не запускается работа блока 7.

Через шесть тактов генератора 2 с шестого выхода дешифратора 29 поступает импульс на вход формирователя 30, с выхода которого импульсом длительностью 0,5 мкс сбрасываются счетчик

17155

27 и триггер 24, запрещая тем самым прохождение импульсов с генератора 2 через элемент И 26 (фиг. 9 г,м). На этом бпок 4 заканчивает работу до прихода следующего импульса с .блока 1 (до начала следующей полуволны питающего напряжения), а 1 первого разряда слова блока 8, считанная на регистр 10 через элемент 17 и первый усилитель блока 18, удерживает в открытом состоянии первый ключ, пропуская напряжение с третьего входа блока 18 на выход устройства 21 в течение данного полулериода питающего на- пряжения. Это соответствует отсутствию помех в этом полупериоде питающего напряжения на входе испытуемого устройства.

С приходом следующего импульса из блока 1 работа устройства повторится, так как считанное через два такта . генератора из блока 8 второе слово по содержанию одинаково с первым словом. По той же причине работа будет аналогичной до прихода 51-го импульса с блока 1. С приходом 51-го импульса через два такта задающего генератора будет считано 51-е слово из блока 8, у которого (фиг. 7) 1 во втором и третьем разряде перепишутся на регистр 10 и поступят на вход дешифратора 15. Далее в соответствии с таблицей состояния дешифратора 15

(фиг. 8) с его третьего выхода единичный сигнал через усилитель откроет четвертый ключ 494 блока 18, в цепи которого включен третий гасящий резистор 503 . На резисторе 50$ произойдет падение 15% входного иитаюцего напряжения, следовательно, в 51-ой полуволне питающего испытуемое устройство напряжения будет помеха в виде провала напряжения амплитудой 15% от номинального.

При поступлении следующего импульса с выхода блока 1 будет считано из блока 8 52-ое слово, под управлением которого откроется шестой ключ блока 18, имитируя провал питающего напряжения на испытуемом устройстве на 25%. Аналогично при прохождении 53-ей полуволны питающего напряжения будет открыт 8-ой ключ блока 18 и на испытуемом устройстве будет провал на 35% питающего напряжения, в 54-ой полуволне - провал 50%, в 55-ой полуволне провал

вал

- про60%, в 56 полуволне 70%. в 57 полуволне - провал

18

0

80%, D 58 полуволне - провал

0

5

0

35

40

45

100%

(разомкнуты все ключи блока 18), в полуволнах с 59-ой по 100-ую провалы отсутствуют, потому что открыт первый 1слюч блока 18. Таким образом, изменяя содержимое слов блока 8, можно динамически в течение цикла изменять амплитуду помех на испытуемом устройстве.

Рассмотрим работу устройства при генерации кратковременной помехи. Дри поступлении 101-го импульса с выхода блока 1 через два такта генератора 2 будет считано 101-ое слово из блока 8, в котором (фиг.7) в первом, третьем, пятом и шестом разрядах 1, поэтому в первом, третьем и пятом разрядах регистра 10 и у триггера 11 будут единичные сигналы на выходе. Единичный сигнал с первого выхода регистра 10 (первый разряд) через элементы 14 и 17 откроет первый ключ блока 18, потому что на выходе регистра 12 в этот момент нулевой сигнал, а на втором входе элемента И 14 - единичный сигнал. Единичные сигналы третьего и пятого разряда регистра 10 поступят на дешифратор 15, в результате чего (фиг. 8) 1 с 10-го выхода дешифратора откроет одиннадцатый ключ блока 18. В этот момент в блоке 18 будут открыты два ключа, первый и одиннадцатый, но так как в цепи первого ключа нет гасящего резистора, то все напряжение, поступающее на третий вход блока-18 через первый ключ, будет выдано на выход 21.

Единичный сигнал с выхода триггера

11поступит на вторые входы элементов И 33-35 блока 4 и через три такта генератора 2 с третьего выхода дешифг ратора 29 через элементы 33 поступит импульс на первый (счетный) вход счетчика 37, который установит по второму входу блока 6 элементов ИЛИ первый адрес на втором входе блока 9. По этому адресу через четыре такта генератора импульсом с четвертого выхода дешифратора 29 через элемент 34 по третьему входу блока 9 будет считано

на регистр 12 первое слово кратковременных помех (фиг. 7) из блока 9. В первом разряде регистра 12 будет О, который поступает па выход регистра. Так как состояние выхода регистра

12после занесения первого слова из блока 9 не изменилось, то состояние

0

15

20

элементов 13, 16, 14 тоже не изменится, и первый ключ блока 18 останется открытым. Через пять тактов генератора 2 с пятого выхода дешифратора 29 через элемент 35 поступит импульс на первый вход триггера 38 блока 7 и взведет его. Единичный сигнал с выхода триггера 38 поступит на второй {вход элемента И 39, разрешая прохождение по первому его входу импульсов с задающего генератора 2 на первый (счетный) вход счетчика 44, выход которого соединен с дешифратором 45. Через шесть тактов генератора 2 с шестого выхода дешифратора 29 поступит импульс на вход формирователя 30, с выхода которого сформированный импульс сбросит счетчик 27 и дешифратор 24, завершив этим работу блока 4 в данном полупериоде питающего напряжения. Работа блока 7 продолжается.

После того, как счетчик 44 просчитает 279 тактов генератора 2, на выходе дешифратора 45 вырабатывается 25 единичный сигнал, поступающий на второй вход элемента И 46, разрешая прохождение 280-го импульса (с момента взведения триггера 42) по первому входу элемента 46. Этим же импульсом счетчик возврацается в исходное нулевое состояние и начинает следующий цикл просчета тактов генератора 2. И так до конца полупериода питающего напряжения, пока не будет сброшен триггер 42 по второму входу с первого выхода дешифратора 29 блока 4 в начале следующего полупериода питающего напряжения.

Таким образом, с выхода блока 7 в течение данного полупериода питающего напряжения будут поступать импульсы длительностью 0,5 мкс и периодом 280 мкс на второй (сдвиговый) вход регистра 12. Причем в рассматриваемом случае при частоте 50 Гц за полупериод поступит 35 импульсов. На фиг. 9 , показаны диаграммы работы узлов блоков 1, 4, 7 в данном полупериоде питающего напряжения, Диаграмма одинакова для всех полупериодов, имеющих кратковременные помехи, признаком которых является 1 в шестом разряде соответствующего слова блока 8, взводящая триггер 11.

На выходе регистра 12 до прихода 55 первого сдвигающего импульса из блока 7 будет первый разряд с нулевым сигналом, поэтому состояние первого

155Q60320

ключа блока 18 не изменится. С приходом первого сдвигающего импульса из блока 7 на выходе регистра будет второй разряд тоже с нулевым сигналом. Описанный алгоритм будет продолжаться до появления пятнадцатого сдвигающего импульса. С приходом этого импульса на выходе регистра 12 появится шестнадцатый разряд с единичным сигналом, который поступит на второй вход элемента И 13. На пер- - вом входе элемента И 13 присутствует единичный сигнал с выхода триггера 11, поэтому на выходе элемента 13 будет единичный сигнал. Этот сигнал через элемент НЕ 16 по второму входу элемента И 14 запретит прохождение единичного сигнала с первого выхода регистра 10 через элемент 17 на первый вход блока 18, по которому до этого момента был открыт первый ключ блока 18. С этого момента первый ключ 45 блока 18 будет закрыт и останется открытым только одиннадцатый ключ с последовательно включенным десятым гасящим резистором, на котором осуществляется падение 50% питающего напряжения. С приходом шестнадцатого импульса из блока 7 на выходе регистра 12 появится семнадцатый разряд также с единичным сигналом, который будет продолжать удерживать закрытым первый ключ в блоке 18, увеличивая этим время кратковременной помехи. Аналогично восемнадцатый разряд с единичным сигналом, поступивший на выход регистра 12 после прихода семнадцатого импульса из блока 7, не изменит состояние первого ключа блока 18, и помеха будет продолжаться. Только с приходом восемнадцатого импульса из блока 7 на выходе регистра 12 появится девятнадцатый разряд с нулевым сигналом, который поступит на второй вход элемента И 13. На выходе последнего в этом случае появится нулевой сигнал, который через элемент НЕ 16 поступит на второй вход элемента И 14, разрешая прохождение по первому входу элемента 14 единичного сигнала с первого выхода регистра 10 для открывания первого ключа блока 18. Первый ключ блока 18 открывается, и напряжение, поступающее на третий вход блока 18, полностью коммутируется через него на выход устройства 21, генерируя тем самым окончание действия кратковре30

35

40

45

50

21

меннон помехи. Таким образом, наличие 1 в шестнадцатом, семнадцатом и восемнадцатом разрядах первого слова блока 9 позволяет генерировать на выходе устройства кратковременную поме- ху длительностью 840 мкс (280 мксх3), амплитудой 50% от питающего напряжения, определяемой содержанием второго,

которого единичный сигнал по первому входу элемента ИЛИ 17 поступает на первый вход блока 18 для открывания первого ключа этого блока. Этим заканчивается цикл генерации помех в однократном режиме работы устройства.

Известные устройства генерируют (имитируют) равновеликие скачкообтретьего, четвертого и пятого разряда « разные помехи (провалы) ка фоне писоответствующего слова блока 8 (в данном случае 101-го).

С продвижением девятнадцатого и последующих разрядов на выход регистра 12 первый ключ блока 18 будет оставаться открытым, потому что в остальных разрядах отсутствуют 1. - Аналогичной будет работа устройства при генерации, помех в 102-ой, 103-ей

15

тающего напряжения, которые не идентичны реальным, изменяющимся по величине во времени провалам напряжения промышленной сети, возникающим при включении и отключении соединенных параллельно устройств. Они не генерируют (имитируют) помехи, которые могут возникать при последовательном во времени включении (отключении) усти 104-ой полуволнах питающего напряже-20 Р°йств в реально существующих промьппния. На фиг. 10 приведена диаграмма работы блоков 7, 12, 13, 14, 16, 17 и форма напряжения на выходе устройства в 101-ом полупериоде питающего наленных сетях. Кроме того, известные устройства не могут генерировать (имитировать) кратковременные помехи в питающем напряжении и во входных

пряжения, а на фиг. 11 и 12 - диаграм-25 цепях испытуемых устройств, которые

ма работы блоков 7, 12 и формы напряжения на выходе устройства в 102-ом, 103-ем и 104-ом полупериодах питающего напряжения.

Таким образом, меняя содержимое второго, третьего, четвертого и пятого разрядов слов блока 8 можно варьировать величиной амплитуды помех, а содержанием разрядов слов блока 9 можно изменять число, длительность и место помех в пределах полупериода питающего напряжения.

В полуволнах с 105-ой по 254-ую отсутствуют длительные и кратковременные помехи, работа устройства в таких полупериодах рассматривалась.

С приходом 255-й полуволны питающего напряжения наступит очередной цикл работы блока 4, но через один такт генератора 2 счетчик 32 увеличит свое содержание на единицу (во всех разрядах счетчика 1) и с выхода дешифратора 36 поступит нулевой сигнал на первый вход элемент 23, прчем на втором входе элемента 23 также нулевой сигнал, заданный с пульта устройства в однократном режиме работы отройства. С выхода элемента 23 нулевой сигнал выдает.запрет по первому входу элемента И 25 на прохождение следующего импульса из блока 1 на запуск блока 4, и этот же сигнал через второй вход элемента ИЛИ 28 взводит триггер 31, с выхода

которого единичный сигнал по первому входу элемента ИЛИ 17 поступает на первый вход блока 18 для открывания первого ключа этого блока. Этим заканчивается цикл генерации помех в однократном режиме работы устройства.

Известные устройства генерируют (имитируют) равновеликие скачкооб

тающего напряжения, которые не идентичны реальным, изменяющимся по величине во времени провалам напряжения промышленной сети, возникающим при включении и отключении соединенных параллельно устройств. Они не генерируют (имитируют) помехи, которые могут возникать при последовательном во времени включении (отключении) устР°йств в реально существующих промьппленных сетях. Кроме того, известные устройства не могут генерировать (имитировать) кратковременные помехи в питающем напряжении и во входных

0

5

0

5

0

5

реально существуют. Предлагаемое техническое решение позволяет генерировать изменяющиеся по величине помехи последовательно во времени (в каждой полуволне питающего напряжения или в каждом периоде синхронизирующего сигнала) в пределах цикла работы устройства, а также генерировать длительность и кратковременность помехи. Кроме того,предлагаемое решение позволяет генерировать разнообразные импульсы специальной формы путем преобразования входного сигнала синхронно с тактовыми сигналами.

Формула изобретения

второго элемента И, блок коммутации, первый и второй входы которого соединены соответственно с выходами элемента ИЛИ и дешифратора, третий вход соединен с второй входной шиной, а выход - с выходной шиной, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены первый и второй запоминающие блоки, блок управления считыванием, первый и второй блоки элементов ИЛИ и блок управления сдвигом, причем первый вход первого запоминающего блока соединен с первым выходом блока управления записью, первый и второй выходы соединены с первыми входами соответственно первого регистра и триггера, а второй вход со.единен с выходом первого блока элементов ИЛИ, первый вход которого соединен с вторым выходом блока управления записью, третий выход которого соединен с первым входом второго запоминающего блока, второй вход которого соединен с выходом второго блока элементов ИЛИ, а выход - с первым входом второго регистра, второй вход которого соединен с выходом блока управления сдвигом, первый выход блока управления считыванием соединен с вторым входом элемента ИЛИ, второй выход - с третьим входом второго регистра и вторыми входами первого регистра и триггера, выход которого соединен с вторым входом первого элемента И и первым входом блока управления считыванием, второй и третий входы которого соединены с выходами, соответственно формирователя импульсов и задающего генератора, третий выход соединен с вторым входом первого блока элементов ИЛИ, а четвертый выход - с третьим входом первого запоминающего блока, при этом четвертый выход 1 блока-управления записью соединен с первым входом второго блока элементов ИЛИ, второй вход которого соединен с пятым выходом блока управления считыванием, причем третий вход второго запоминающего блока соединен с шестым выходом блока управления считыванием, седьмой выход которого соединен с первым входом блока управления сдвигом, второй вход которого соединен с выходом задающего генератора, а третий вход - с вторым выходом блока управления считыванием, при этом пятый и шестой выходы блока управления записью соединены с четвертыми входами соответственно первого и второго запоминающих блоков.

Q счетчики импульсов, первый и второй дешифраторы, первый и второй члемен- ты ИЛИ и формирователь импульсов, причем первый вход второго элемента ИЛИ соединен с первой шиной управле-

5 ния, выход - с первым входом второго триггера, а второй вход - с выходом первого элемента ИЛИ и первым входом первого элемента И, первый вход первого элемента ИЛИ соединен с выходом второго дешифратора, второй вход - с второй шиной управления, третья шина управления соединена с вторым входом первого элемента И, третий вход которого является вторым входом блока управления считыванием, а выход соединен с первым входом первого триггера, выход которого соединен с первым входом второго элемента И, второй вход которого является третьим входом бло-

0

5

0

5

0

5

0

5

ка управления считыванием, а выход| соединен с первым входом первого счетчика импульсов, выход которого соединен с входом первого дешифратора, первый выход которого соединен с вторым входом второго триггера, первым входом второго счетчика импульсов и является вторым выходом блока управления считыванием, второй выход первого дешифратора является четвертым выходом блока управления считыванием, третий, четвертый и пятый выходы первого дешифратора соединены с первыми входами, соответственно, третьего, четвертого и пятого элементов И, а шестой выход через формирователь импульсов соединен с вторыми входами первого триггера и первого счетчика импульсов, при этом вторые входы третьего, четвертого и пятого элементов И соединены с первым входом блока управления считыванием, выход второго триггера является первым выходом блока управления считыванием, выход второго счет- чика импульсов соединен с входом второго дешифратора и является третьи выходом блока управления считыванием, выход третьего элемента И соединен с первым входом третьего счетчика

импульсов, выход которого является пятым выходом блока управления считыванием, выходы четвертого и пятого элементов И являются шестым и седьмым выходами блока управления считывани- , вторые входы второго и третьего

ем

счетчиков импульсов соединены с четвертой шиной управления.

СМ, 30

28

От Ил

ока, 7

сПУ.

23

Отбмка

39

W

с л у

Э

№

От 6м ка2

W

U

Б

27

Q

вторым входом блока управления сдвигом, а второй вход соединен с выходом триггера, второй вход которого является третьим входом блока управления сдвигом, счетчик импульсов, первый вход которого соединен с выходом первого элемента И, второй вход - с вторым входом триггера, а выход - с входом дешифратора, и второй элемент И, первый вход которого соединен с первым входом первого элемента И, второй вход - с выходом дешифратора, а выход является выходом блока управления, сдвигом.

3/

77 7Г J

32

35

К блоку Я

К блока 112, П, if

«

К блоку 5

сПУ

37

блоку f К блоку 6

W

35

К блоку 3

Кйюц/7

30

О

фиг. 2

U«J

фиеЛ

5J

5

Я

52

ъ

57

58

61

19,

Фат

фиг. В

к блоку 4

X блоку 5

КймкуЗ

К блоку 6

53

К блоку 8 -.-

60

ХЛю,

ку9

Фиг. 5

2/

62

гг

Фиг.1

Фиг.8

Ж

3 u к л

м

н

о

7

4Л 12

/J

„ 16

17

фаг 9

immmninmmiimnmim

5 Ю 15 20 25 10 35

18

/X

/N

/

Ю1-ая пмуёолна

фаг 9

.Ю

HinillllllllllllllllltinilMllll

ттптттщшшш

5 Ю (4 ±0 25 X

33

/

Выход Илока18

iinmiiiiMimmiintiinmm

5 Ю 15 го 25 30 35 TLJU

Выход блока 18

33

| Имитатор провалов напряжения сети | 1984 |

|

SU1211858A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ИМИТАТОР ПРОВАЛОВ НАПРЯЖЕНИЯ СЕТИ | 0 |

|

SU268493A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-15—Публикация

1988-05-30—Подача