1

Изобретение относит|Ся ж области радиотехники, В частности к импульсной технике.

Известны устройства для изменения периодов следования импульсов, Содержащие делитель вталон ной частоты, охемы совпадения и счетчик-регистр памяти, которые .позволяют получать сигнал ic периодом следования импульсов, изменяющимся то ступенчато.-пилообразному закону. Сигнал на выходе таких устройств представляет собой лоследовательность импульсов, каждый по1следук щий период которой отличается от Предыдущего «а время, рааное периоду ситнала, поступающего на вход устрой|ства. Периоды следования импульсов на выходе известных устройств изменяются от величины, равной периоду входных импульсов, до величины, равной произведению периода входных импульсов на емкость делителя эталонной частоты.

Недостатком известных устройств является то, что они формируют сигнал € несимметричным законом изменения периодов следования выходных импульсов.

Цель изобретения - создание устройства, позволяющего осуществлять изменение периодов .следования имюульсов по симметричному закону.

В предлагаемое устройство дополнительно введены схемы «И, «ИЛИ и трвлгер знака, вход которого соединен с выходом счетчи1ка-

регистра памяти, а выход каждого пз триггеров счетчика-регистра памяти подключен к первому входу соответствующей схемы «И, вторые входы схемы «И соединены с выходами триггера знака, причем схемы «И, подключенные к выходам одного и того же /-го триггера счетчика-регистра памяти, соединены с .разными выходами триггера знака, а выходы этих .схем |«И через схему «ИЛИ соединепы с установочным выходом /-го три ггера делителя эталонной частоты, где / 1, 2. 3,. . ., п.

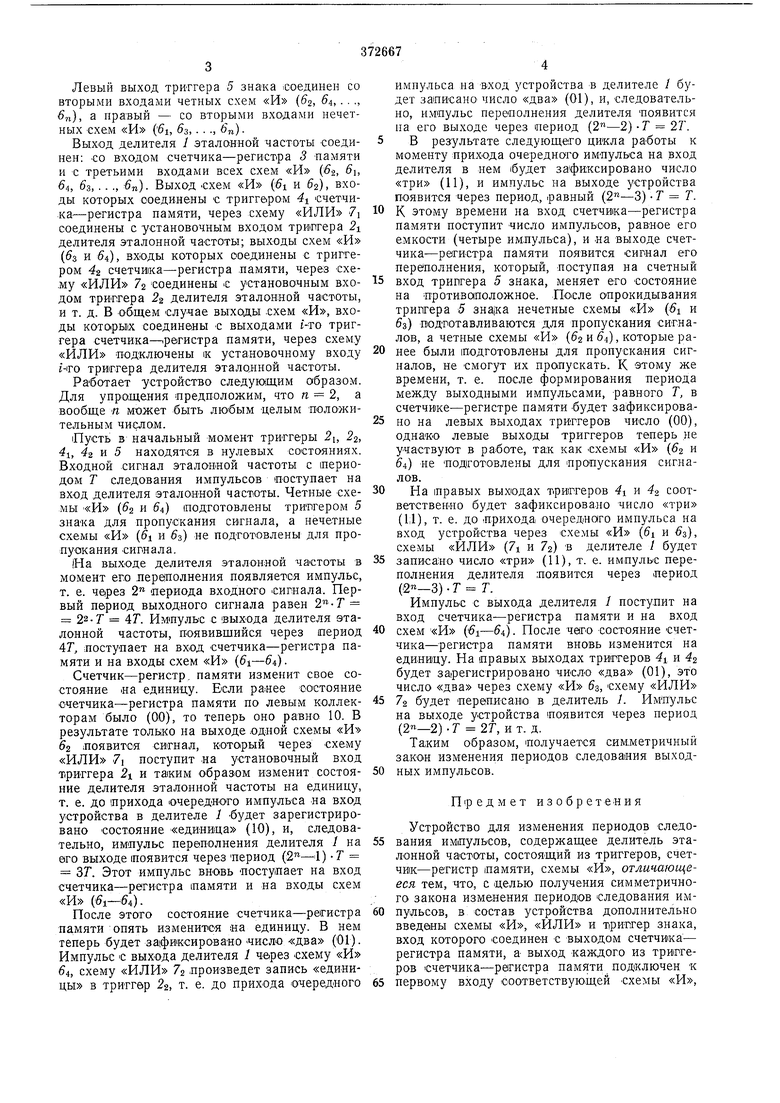

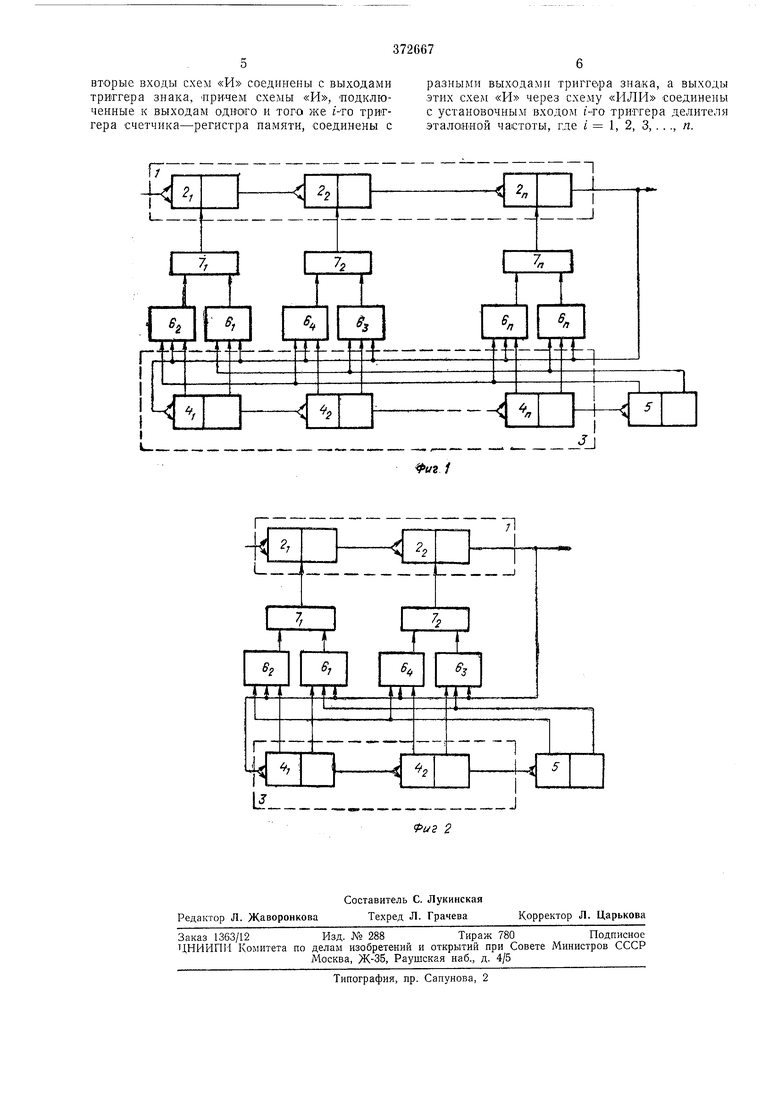

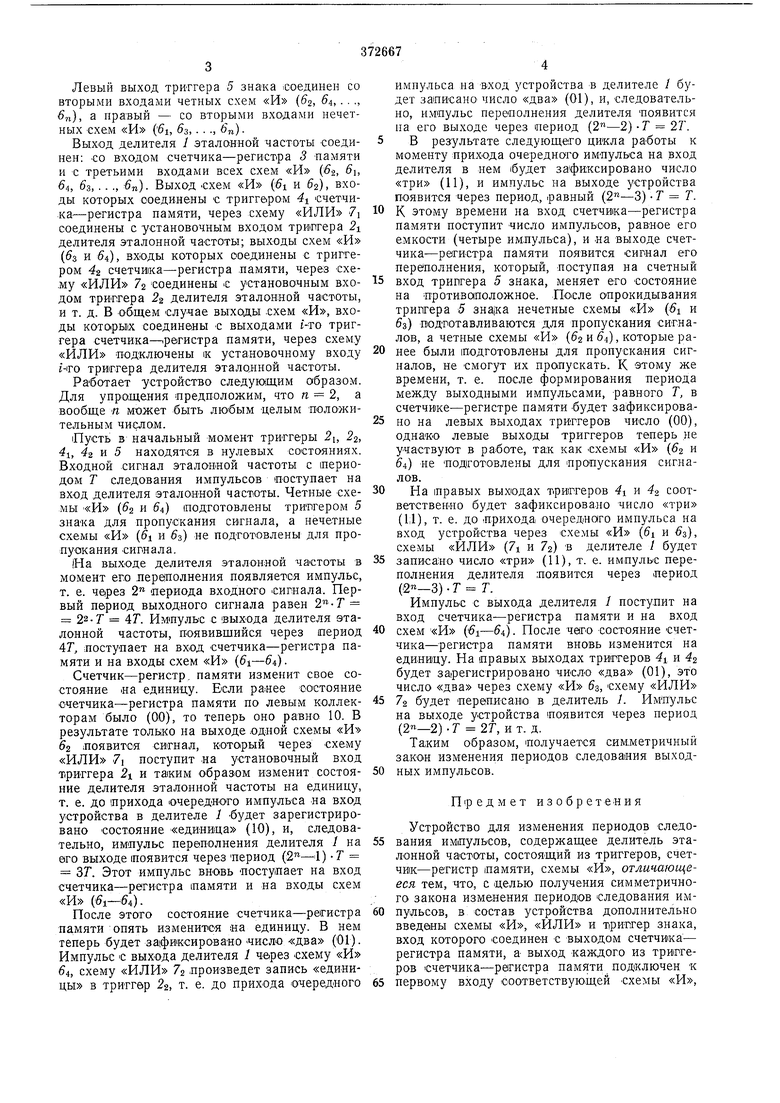

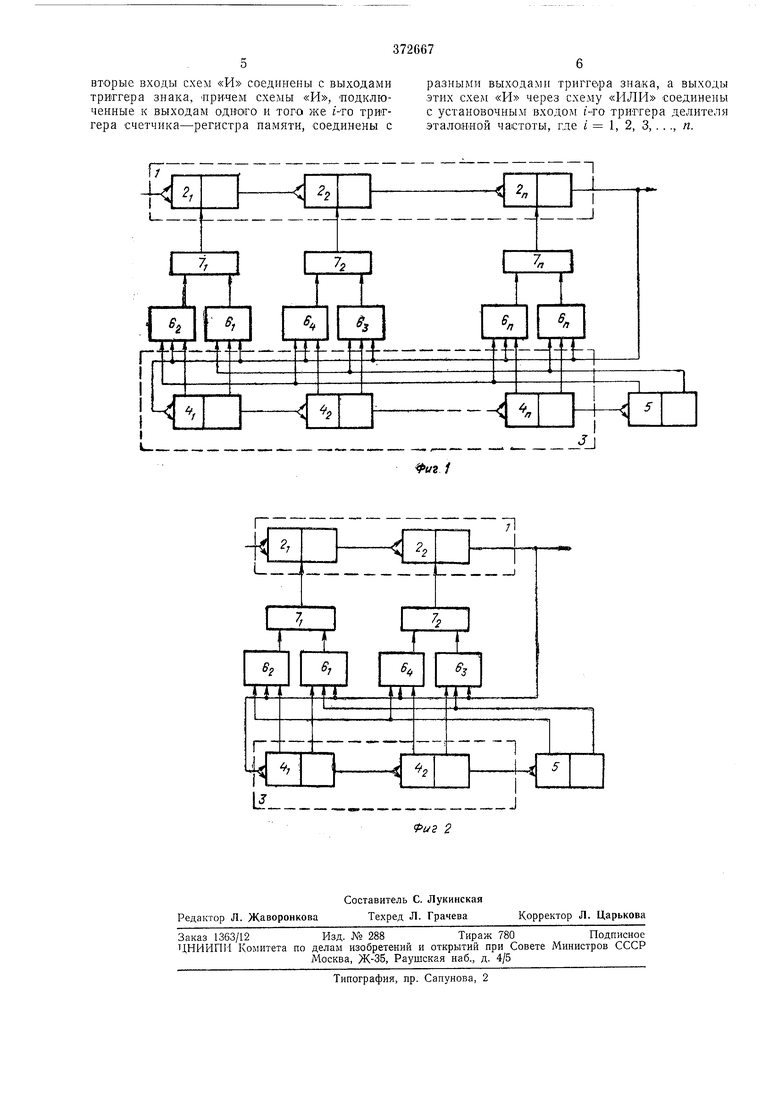

На фиг. 1 изображена схема описываемого устройства; на фиг. 2 - то же, при п 2.

Делитель / эталонной частоты содержит последовательно включенные триггеры 2i, 2, . . ., 2-п со счетными входами, а счетчик- регистр 3 памяти состоит и-з (последовательно включенных триггеров 4i, 4, .. ., 4п со счетными входами. Выход счетчика-регистра памяти соединен со счетным входом триггера 5 знака.

Каждый выход каждого триггера счетчика- регистра памяти подключен ко входу собственной схемы «И.

Левые выходы триггеров 4, 4, . . ., 4п соединены .со входами четных схем «И (6, б, .. ., 6п), правые выходы три пгеров 4i, 4,. . ., 4п соединены со выходами нечетных схем «И

(6,,6,,...,6г,).

Левый выход триггера 5 знака -соединен со вторыми входами четных схем «И (62, 6,.. ., 6п), а правый - со вторыми входами нечетных схем «И (5i, 63,. . ., 6п).

Выход делителя эталонной частоты соединен; со входом счетчика-регист.ра 3 -памяти и с третьими входами всех схем «И (6-2, 6i, 6ц, бз, ..., -бп). Выход схем «И (i и бг), входы которых соединены с триггером 4 счетчика-регистра памяти, через схему «ИЛИ 7 соединены с установочным входом триггера 2 делителя эталонной частоты; выходы схем «И (бз и 4), входы которых соединены с триггером 4z счетчика-регистра .памяти, через схему «ИЛИ 72 соединены с установочным входом триггера 2 делителя эталонной частоты, и т. д. В Общем случае выходы схем «И, входы кото.рЫ1Х соединены с выходами i-то триггера счетчика-.регистра памяти, через схему «ИЛИ подключены « установочному входу г-|го триггера делителя эталонной частоты.

Работает устройство следую|щим образом. Для упрощения предположим, что « 2, а вообще п может быть любым -целым положительным ЧИСЛО.М.

Пусть в начальный момент триггеры 2i, 2, 4-i, 2 и 5 находятся в нулевых состояниях. Входной сигнал эталонной частоты с периодом Т следования импульсов поступает на вход делителя эталонной частоты. Четные схемы «И (6 и 64) подготовлены триггером 5 знака для пропускания сигнала, а нечетные схемы «И (5i и 5з) не подготовлены для пропускания сигнала.

|На выходе делителя эталонной частоты в момент его .переполнения появляется импульс, т. е. че|рез 2 периода входного сигнала. Первый период выходного сигнала равен 22-7 47. Импульс с выхода делителя эталонной частоты, появившийся через оериод 4Г, поступает на вход счетчика-регистра памяти и на входы схем «И ().

Счетчик-регистр, памяти изменит свое состояние на единицу. Если ранее состояние счетчика--регистра памяти по левым коллекторам было (00), то теперь оно равно 10. В результате только на выходе одной схемы «И 62 появится сигнал, который через схему «ИЛИ 7i поступит .на установочный вход Тгриггера 2 и таким образом изменит состояние делителя эталонной частоты на единицу, т. е. до прихода очередного импульса на вход устройства в делителе 1 будет зарегистрировано состояние «единвца (10), и, следовательно, импульс переполнения делителя / на его выходе появится через период () -Т ЗГ. Этот импульс вновь поступает на вход счетчика-регистра памяти и на вхо-ды схем «И (6i-64).

После этого состояние счетчика-регистра памяти опять изменится на единицу. В нем теперь будет зафвксирова-но число «два (01). Импульс с выхода делителя 1 ч-ьрез схему «И 64, схему «ИЛИ /2 произведет запись «единицы в триггер 22, т. е. до прихода очередного

импульса на вход устройства в делителе / будет записано число «два (01), и, следовательно, импульс переполнения делителя появится на его выходе через период () -Т 27. В результате следующего цикла работы к моменту прихода очередного импульса на вход делителя в нем будет зафиксировано число «три (11), и импульс на выходе устройства появится через период, .равный () -1 1.

К этому времени на вход счетчика- регистра памяти поступит -число импульсов, равное его емкости (четыре импульса), и на выходе счетчика-регистра памяти появится сигнал его переполнения, который, поступая на счетный

вход триггера 5 знака, меняет его состояние на противоположное. После опрокидывания триггера 5 зна|ка нечетные схемы «И (5i и бз) подготавливаются для пропускания сигналов, а четные схемы «И (62 и 64), которые ранее были подготовлены для пропускания сигналов, не смогут их пропускать. К этому же времени, т. е. после формирования периода между выходными импульсами, -равного Т, в счетчике-регистре памяти -будет зафиксирова,но на левых выходах триггеров число (00), однако левые выходы триггеров теперь не участвуют в работе, так как схемы «И (6ч и 6) не подготовлены для пропускания сигналов.

На 1правых выходах триггеров 4 и 4 соответственно будет зафиксирова.но число «три (1,1), т. е. до прихода очередного импульса на вход устройства через схемы «И (6 и з), схемы «ИЛИ (7i и /2) в делителе / будет

записано число «три (11), т. е. импульс переполнения делителя появится через период (2«-3) -Т Т.

Импульс с выхода делителя / поступит на вход счетчика--регистра памяти и на вход

схем «И (). После чего -состояние счетчика-регистра памяти вновь изменится на единищу. На правых выходах триггеров 4 и 2 будет за|регистрировано число «два (01), это число «два через схему «И бз, схему «ИЛИ

/2 будет перенисано в делитель L Импульс на выходе устройства появится через период ().7 2Г, ит. д.

Таким образом, получается сим.метричный закон изменения периодов следования выходных импульсов.

Предмет изобретения

Устройство для изменения периодов следования импульсов, содержащее делитель эталонной частоты, состоящий из триггеров, счетчик-регистр памяти, схемы «И, отличающееся тем, что, с |Целью получения симметричного закона изменения .периодов следования импульсов, в СО-став устройства дополнительно введены схемы «И, «ИЛИ и триггер знака, вход которого соединен с выходом счетчика- регистра памяти, а выход каждого из триггеров счетчика-регистра памяти подключен к первому входу соответствую.щей схемы «И,

вторые входы схем «И соединены с выходами триггера знака, -ирнчем схемы «И, подключенные к выходам одного и того же г-то триггера счетчика-регистра иамяти, соединены с

разными выходами тригге.ра зна|Ка, а выходы этих схем «И через схему «ИЛИ соединены с установочным входом г-го триггера делителя эталойной частоты, где i I, 2, 3, . . ., п.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1986 |

|

SU1345305A1 |

| УСТРОЙСТВО для ИЗМЕНЕНИЯ ЧАСТОТЫ СЛЕДОВАНИЯ | 1973 |

|

SU381170A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Централизованная многоканальная счетная система | 1976 |

|

SU748425A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ | 1995 |

|

RU2118827C1 |

| Устройство для измерения частоты импульсов | 1979 |

|

SU922653A1 |

| Устройство для измерения частоты | 1988 |

|

SU1550434A1 |

| Устройство для регулировки тока луча записи электронно-лучевой трубки | 1985 |

|

SU1244806A2 |

| Частотный дискриминатор | 1984 |

|

SU1241142A1 |

| Аналого-цифровой функциональный преобразователь | 1976 |

|

SU567203A1 |

Даты

1973-01-01—Публикация