ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1987 |

|

SU1448394A2 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство для определения динамических характеристик объектов | 1986 |

|

SU1471098A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

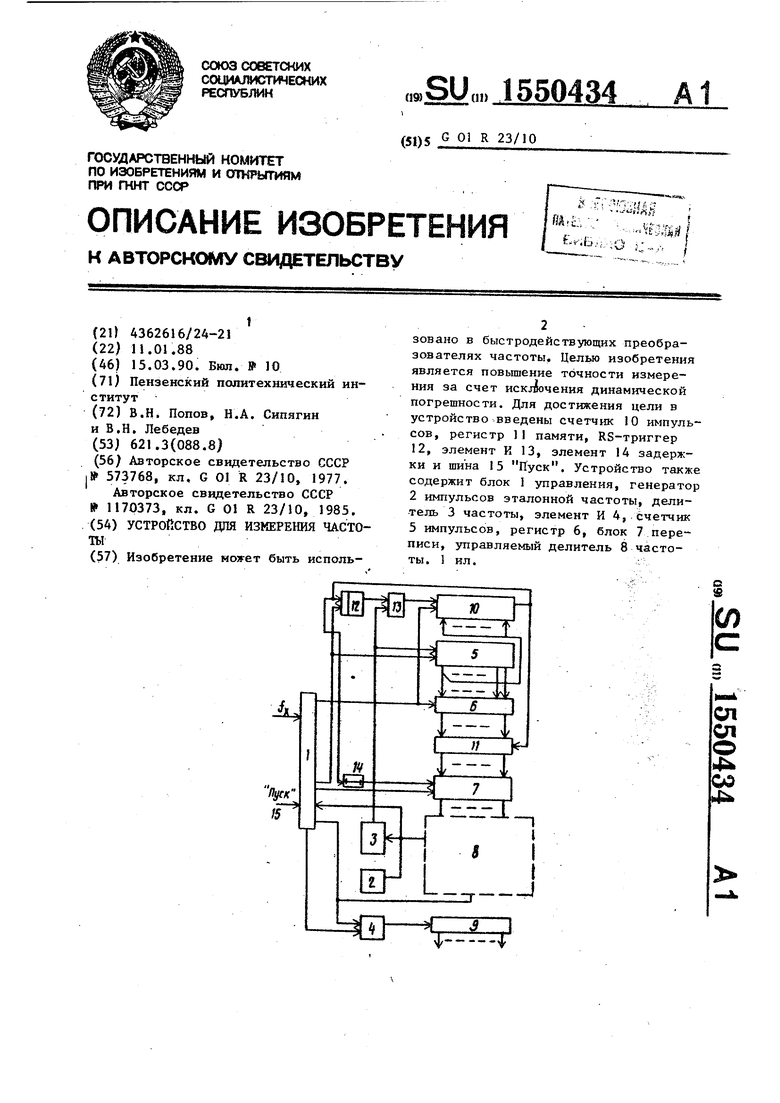

Изобретение может быть использовано в быстродействующих преобразователях частоты. Целью изобретения является повышение точности измерения за счет исключения динамической погрешности. Для достижения цели в устройство введены счетчик 10 импульсов, регистр 11 памяти, RS-триггер 12, элемент И 13, элемент 14 задержки и шина 15 "Пуск". Устройство также содержит блок 1 управления, генератор 2 импульсов эталонной частоты, делитель 3 частоты, элемент И 4, счетчик 5 импульсов, регистр 6, блок 7 переписи, управляемый делитель 8 частоты. 1 ил.

ел сп

4ь

СО Јь

Изобретение относится к цифровой технике измерения частоты следования импульсов,

Целью изобретения является повышение точности измерения за счет исключения динамической погрешности преобразования частоты в код.

На чертеже представлена функциональная схема предлагаемого устрой- с тв а.

Устройство для измерения частоты содержит блок 1 управления, генератор 2 импульсов эталонной частоты, делитель 3 частоты, первый элемент И 4, первый счетчик 5 импульсов, первый регистр 6 памяти, блок 7 переписи, управляемый делитель 8 частоты, второй счетчик 9 импульсов, третий счетчик 10 импульсов, второй регистр 11 памяти, RS-триггер 12, второй элемент И 13, элемент 14 задержки, шину Пуск 15„

Входом устройства является первый вход блока 1 управления, первый выхо которого соединен с вторым входом первого элемента И 4, первый вход которого объединен с выходом управляемого делителя 8 частоты и соединен с четвертым входом блока 1 управления, второй вход которого соединен с шиной 15 Пуск, третий вход соединен с выходом генератора 2 импульсов эталонной частоты, который соединен с входом делителя 3 частоты и счетным входом управляемого делителя 8 частоты, (п+1) информационных входов которого соединены с (п+1) информационными выходами блока 7 переписи п информационных входов которого соединены с п. информационными выходами

второго регистра 11 памяти, п информационных входов которого соединены с п информационными выходами первого регистра 6 памяти, п информационных входов которого соединены с п информационными выходами первого счетчика 5 импульсов, (п-1) информационных выходов которого соединены с (n-i) информационными входами третьего счетчика 10 импульсов., выход которого соединен с синхровходом второго регистра 11 памяти9 входом элемента 14 задержки и R-входом RS-триггера 12, выход которого соединен с первым входом второго элемента И 13, выход которого соединен со счетным входом третьего счетчика 10 импульсов, установочный вход, которого объединен

Q

5

0

5

с синхровходом первого регистра 6 памяти и соединен с вторым выходом блока I управления, третий выход которого соединен с установочным входом второго счетчика 5 импульсов и S-BXO- дом RS-триггера 12, Второй управляющий вход блока 7 переписи соединен с четвертым выходом блока 1 управления, первый управляющий вход блока 7 управления соединен с выходом элемента 14 задержки, при этом выход делителя 3 частоты соединен со счетным входом первого счетчика 5 импульсов и вторым входом второго элемента И 13, а информационные выходы счетчика 9 импульсов являются выходом устройства

Устройство работает следующим образом.

В момент поступления первого после сигнала Пуск импульса измеряемой частоты fx -по его переднему фронту на втором выходе блока 1 управления формируется импульс, обеспечивающий перепись содержимого счетчика 5 в регистр 6 памяти и в счетчик 10. По заднему фронту входного импульса f v на третьем выходе блока 1 управА

0

ления формируется сигнал, обеспечивающий установку счетчика 5 в,нулевое состояние, установку RS-триггера 12 в единичное состояние. Процесс кодирования начинается в момент прихода второго импульса входной последовательности. Кроме того, сигнал с первого выхода блока 1 управления открывает элемент И 4 на все время измерительного интервала , формируемого в блоке 1 управления путем пересчета импульсов эталонной частоты fb, поступающей на третий вход этого блока.

Импульсная последовательность с выхода генератора 2 опорной частоты

5 поступает на счетный вход управляемого делителя 8 частоты и на вход делителя 3 частоты, коэффициент деления которого равен М. Период следования управляющих импульсов с выходов блоQ ка 1 управления определяется периодом следования импульсов входной последовательности fx.

Импульсы с выхода делителя 3 частоты поступают на счетный вход счет- чика 5, счетный вход счетчика 10, работающего в режиме вычитания через элемент И 13 с частотой f0/M. Содержимое счетчика 5 переписывается в регистр 6 памяти и счетчик 10 в прямом коде. Причем емкость счетчика выбрана в два раза меньше, чем емкость счетчика 5, а разрядность счетчика 5 и частота опорных импульсов fc выбираются таким образом, чтобы периоду минимальной частоты Тмвкссо- ответствовал код 1000...О, т.е. единица в старшем разряде. Соответственно код периода максимальной частоты (ЧОО. . .0. Данное условие позволяет синхронизировать два одновременно протекающих процесса в устройстве: кодирование и развертку кода.

За период Тх; (текущего периода входной последовательности) входного сигнала fx(t) в счетчике 5 будет сформирован кодовый эквивалент данного периода

15 10

Ls.

М

Предположим, что сигнал на входе устройства скачком изменяется от

Тммн . Как указывалось, Т MOIKC

соответствует код 1000...0.

В момент времени, соответствующий окончанию TMOKC, блок 1 управления формирует управляющие сигналы, которые обеспечивают следующее продвижение информации. Код Nr ьесчет- чика 5 переписьюается в регистр 6 памяти и счетчик 10 будет в нулевом состоянии, затем счетчик 5 обнуляется, триггер 12 установится в единичное состояние и открывается элемент И 13. Первый же импульс последовательности fe/M, поступивший на счетный вход счетчика 10, вызовет установку всех его разрядов в единицу и сформирует на его выходе импульс, который осуществит сброс триггера 12, перепись содержимого регистра

6 памяти в регистр 1J памяти и с задержкой О,, которую обеспечивает элемент 14 задержки (причем . j/ где Јя- время распространения сигнала через элемент 14 задержки; Јjen время, необходимое для записи кода в регистр 11), произведет перепись содержимого регистра 11 памяти со .сдвигом на 1 разряд в сторону старших разрядов в инверсном коде через блок 7 переписи в управляемый делитель 8 частоты.

Частота следования импульсов на выходе управляемого делителя 8 частоты определяется выражением

0434

Leux

NМ««е

Тмдке

fo М

вх /чин

М,

0

т.е. в М раз выше входной.

Эта импульсная последовательность поступает на вход счетчика 9, где в течение времени ТИЛм будет сформирован код частоты входного сигнала

f т j-.i j. i

..„н-М

мин

сиг-|их -1- ИЗМ

Согласно предположению о скачке сигнала на входе устройства, в счетчике 5 производится кодирование Т В момент окончания периода TWMM 5 налами с блока 1 управления кодовый эквивалент периода Тмн переписывается в счетчик 10 и регистр 6 памяти. В счетчике 10 будет содержаться код 1000...0. соответствующий Т„„„. Затем

(И Н

о в счетчике 5 начинается процесс кодирования следующего периода. Импульсная последовательность f0/M поступает на счетные входы счетчиков 5 и 10t Содержимое счетчика 10 уменьшается

5 до нуля, а затем первый же импульс обеспечит формирование на выходе счетчика 10 импульса, который перепишет содержимое регистра 6 в регистр 1 1 и с задержкой t1 а через блок 7 пе0 реписи содержимое регистра 11 в счетчик управляемого делителя 8 частоты. К тому времени заканчивается процесс развертки кода максимального периода Тмс(кс , т.е. на выходе управ5 ляемого делителя 8 частоты сформировано М импульсов. В случае скачка входного сигнала от ТМнн к Тме(КС работа устройства происходит следующим образом.

40

В

момент окончания TMMM кодовый

эквивалент периода TMMff переписывается из счетчика 5 в регистр 6 и счетчик 10. Предположим, что следующий период также Тммн . Теперь в момент 5 окончания кодирования на выходе счетчика 10 формируется импульс, который4 переписывает содержимое регистра 6 в регистр 1 1, производит сброс триггера 12 и с задержкой C-j, через блок 7 переписи со сдвигом на один разрчд в сторону старших разрядов содержимое регистра 11 в управляемый делитель 8 частоты, где начинается очередной цикл процесса развер тки нового кода. Кроме того, содержимое счетчика 5 сигналом с блока 1 управления переписывается в регистр 6 и счетчик 10.

Период на входе устройства изменяется до TMeuc, так как содержимое

0

5

71550434

ка 10 соответствует TMUHs то время, соответствующее Тмин, оде счетчика 10 будет сформиимпульс, по которому информа™ регистра 6 перепишется в ре11. К этому времени закончится процесс развертки кода предыпериода, Начинается процесс тки кода второго периода Кодирование TMO(I Cпродолжается. нт окончания ТмС11,с содержимое ка 5 переписывается в регьстр етчик 10 Как указывалось выше9 же импульс последовательности

10

15

в в с т с в с

п с л в т с в ч п и в с р R в м н в д г г ч 45 с с п г н т д р д д к

Ј0/М сформирует на выходе счетчика

10импульс, который обеспечит перепись содержимого регистра 6 в регист

11и с задержкой Ј„, содержимого регистра 11 в управляемый депитель 8 частоты. Так как ThcjK 2T мин, что соответствует динамическому диапазону, то к моменту подачи кода максимального периода заканчивается и процесс развертки кода предыдущего периода

т мин

В предлагаемом устройстве реализован метод постоянной временной задержки на время, равное максимальному периоду Т а(сс входного сигнала, что обеспечивает исключение динамической погрешности и„ следовательно, увеличивает динамическую точность измерения.

Таким образом, предлагаемое устройство для измерения частоты обес« печивэет высокую точность и статическом и динамическом режимах измерений, погрешность квантования имеет значение, не превышающее ±0,5/N (максимально возможное для дискретных устройств)9 а динамическая погрешность исключается.

Формула изобретения Устройство для измерения частоты, содержащее блок управления, делитель частоты два счетчика импульсов, первый элемент И, первый регистр памяти управляемый делитель частоты,, блок переписи, шину Пуск и генератор импульсов эталонной частоть выход которого соединен с входом делителя частоты, счетным входом управляемого делителя частоты и тре

8

тьим входом блока управления, первый вход блока управления является входом устройства, второй вход соединен с шиной Пуск, а четвертый вход с выходом управляемого делителя частоты и первым входом первого элемента И, второй вход которого соединен с первым выходом блока управления, второй выход которого соединен с синхровходом первого регистра памяти, а третий - с входом установки

15

20

25

30

35

40

50

первого счетчика, выходы которого соединены соответственно с входами первого регистра памяти, второй управляющий вход блока переписи соединен с четвертым выходом блока управления, информационные выходы блока переписи соединены с информационными входами управляемого делителя частоты, выход первого элемента И соединен со счетным входбм второго счетчика, информационные выходы которого являются выходом устройства, выход делителя частоты соединен со счетным входом первого счетчика, отличающееся тем, что, с целью повышения точности измерения за счет исключения динамической погрешности, в него дополнительно введены третий счетчик, второй регистр памяти, второй элемент И, элемент задержки и RS-триггер, S-вход которого соединен с третьим выходом блока управления, а R-вход - с синхровходом второго регистра памяти, входом элемента задержки и выходом переполнения третьего счетчика, установочный вход которого соединен с вторым выходом блока управления, выход RS- триггера соединен с первым входом второго элемента И, выход которого соединен со счетным входом третьего счетчика, информационные входы которого 45 с первого по (п-1)-й соответственно соединены с информационными выходами первого счетчика, выходы первого регистра памяти соответственно соединены с входами второго регистра памяти, выходы которого соединены с входами блока переписи, второй вход второго элемента И соединен с выходом делителя частоты, выход элемента за- - держки соединен с первым входом блока переписи.

| Цифровой измеритель инфранизких и низких частот | 1976 |

|

SU573768A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-15—Публикация

1988-01-11—Подача