Изобретение относится к области цифровой вычислительной техники и может быть использовано в цифровых устройствах вычислительной и измерительной техники, автоматики и телемеханики.

Известные устройства для контроля последовательности импульсов, содержащие многовходовые схемы «ИЛИ и триггеры, выходы которых соединены со схемой сравнения, имеют недостаточную эффективность контроля.

Предлагаемое устройство отличается тем, что триггеры соединены между собой через введенные вентили переписи информации по схеме трехтактного кольцевого сдвигающего регистра, а к соответствующим входам вентилей переписи подключены выходы схем «ИЛИ. Это повышает эффективность контроля.

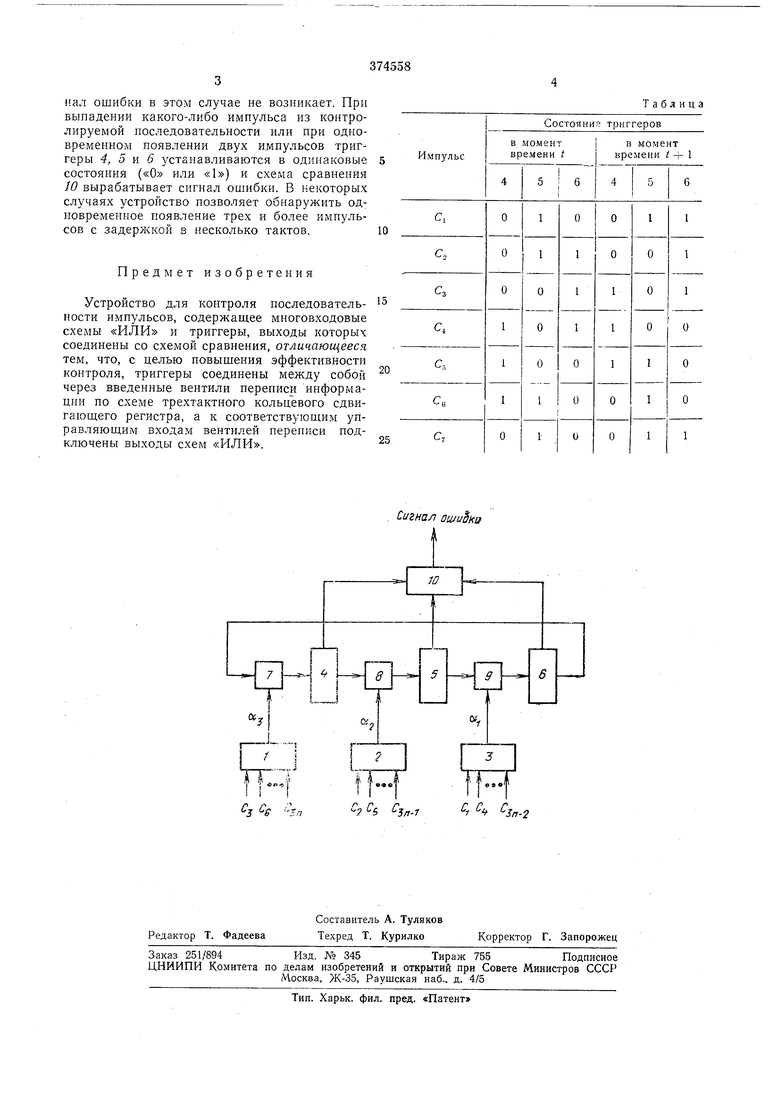

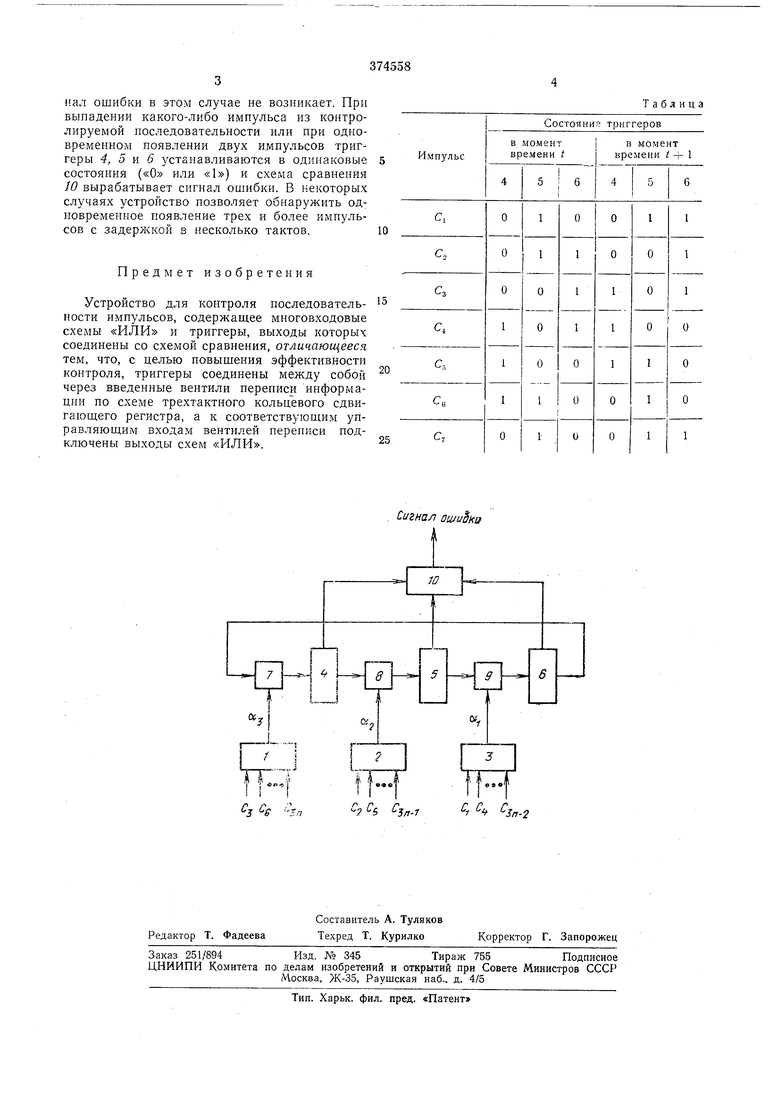

На чертеже изображена блок-схема предлагаемого устройства.

Устройство для контроля последовательности импульсов содержит многовходовые схемы «ИЛИ 1, 2 и 3 для сборки контролируемых импульсов, триггеры 4, 5 и 6 с раздельными входами, вентили 7, 8 и 9 переписи информации между триггерами и схему сравнения 10. Триггеры , 5 и б, а также вентили 7, 8 vi 9 образуют трехтактный кольцевой сдвигающий регистр.

Устройство работает следующим образом. На выходе схемы «ИЛИ 3 формируется сигнал сборки контролируемых импульсов первой группы ... УСз,1- На выходе схемы «ИЛИ 2 формируется сигнал сборки контролируемых импульсов второй группы a2 C2VC,:,V ... 1/Сз.7-|, а на выходе схемы

«ИЛИ 1 - сигнал сборки контролируемых импульсов третьей группы a ... , Сигналы а, 02, «3 подаются соответственно на стробирующие входы вентилей 9, 8 и 7. Вентили 7, 8 и 9 служат для переписи

информации триггерами 4, 5 }i 6.

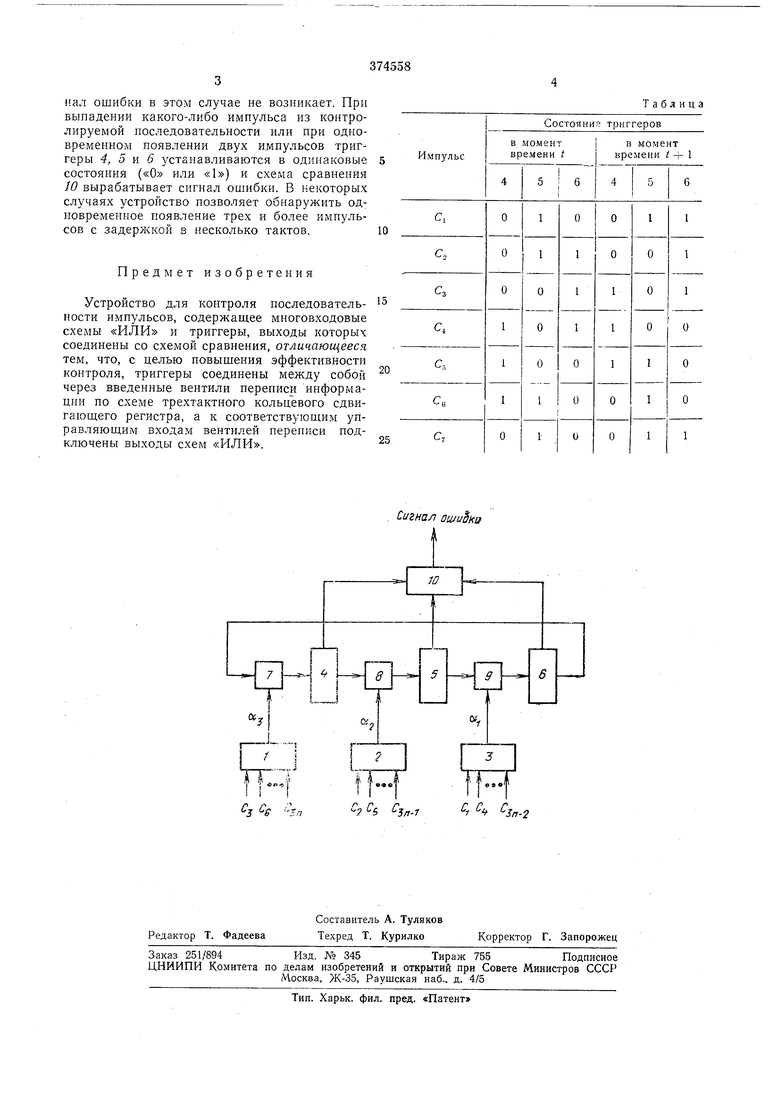

Единичные и нулевые входы триггеров 4, 5 и 6 подключены ко входам схемы сравнения 10. В исходном состоянии триггеры 4, 5 и 6 находятся соответственно в состояниях , «Ь, «О. При нормальном чередовании контролируемых импульсов состояние тригге,j ров 4, 5 и 6 изменяется (см. таблицу). Сигнал ошибки в этом случае не возникает. При выпадении какого-либо импульса из контролируемой последовательности или при одновременном появлении двух импульсов триггеры 4, 5 и 6 устанавливаются в одинаковые состояния («О или «1) и схема сравнения 10 вырабатывает сигнал ошибки. В некоторых случаях устройство позволяет обнаружить одновременное появление трех и более импульсов с задержкой в несколько тактов.

Предмет изобретения

Устройство для контроля последователькости импульсов, содержащее многовходовые схемы «ИЛИ и триггеры, выходы которых соединены со схемой сравнения, отличающееся тем, что, с целью повышения эффективности контроля, триггеры соединены между собой через введенные вентили переписи информации по схеме трехтактного кольцевого сдвигающего регистра, а к соответствующим управляющим входам вентилей переписи подключены выходы схем «ИЛИ.

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 1967 |

|

SU206155A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| УСТРОЙСТВО для ВВОДА ИНФОРМАЦИИ | 1972 |

|

SU326568A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК С ЕДИНИЧНЫМ КОДИРОВАНИЕМ | 1969 |

|

SU255646A1 |

| Устройство управляемой задержки импульсов | 1981 |

|

SU993457A1 |

| УСТРОЙСТВО для ГЕНЕРАЦИИ ТРОИЧНОГО КОДА С ПОСТОЯННЫМ КОЛИЧЕСТВОМ «НУЛЕЙ» | 1969 |

|

SU251931A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ РЕГИСТРАЦИИ | 1973 |

|

SU404112A1 |

| Счетное устройство с предварительной уставкой кода | 1982 |

|

SU1027832A1 |

| ВСЕСОЮЗНАЯ Iи1НТНО-ГЕ1йГ]Н;^?ДШE'-'!SJU^O':"tKA ^ | 1972 |

|

SU337782A1 |

Сигнал ошибка

Т

W

ftj

,L,

j е Зп

W

Г

TF-f

1 Зп-2

5 5/г-Г

Авторы

Даты

1973-01-01—Публикация