Изобретение относится к импульс- ной технике и может быть использовано в измерительной, приемной, передающей технике, в устройствах вычислительной техники для формирования сдвига или задержки.

Известно устройство управляемой задержки импульсов-, содержащее генератор счетных импульсов, четыре вентиля, два реверсивных счетчика, два дешифратора, два триггера и две входные клеммы ClJ.

Недостатком данного устройства является необходимость предварительной установки перед каждьам импульсом требуемой величины задержки. Кроме того, в устройстве отсутствует возможность управления задержкой цифровым кодом и восстановления импупъ;сов при сбоях.

Наиболее близким по технической сущности является цифровой фазосдвигатель, стоящий из формирователя одиночных импульсов, h -разрядных сдвигакицего регистра, буферного регистра и дешифратора, а также О-триггера и сумматора по модулю два, причем тактовые входы формирователя .одиночных импульсов, сдвигакицего регистра и D-триггера соединены вместе и подключены к генератору тактовых импульсов, выхоф буферного регистра подключены к входам параллельной записи сдвигающего регистра, выходы которого соединешл с входами дешифратора, выход дешифратора подключен к D -входу триггера, выход которого подключен к одному из сумматора по модулю два, два дру10гих входа которого соединены с двумя выходами сдвигающего регистра, а выход соединен с входсм последовательной записи сдвигающего регистра 2 J.

15

Недостатком известного цифрового фазосдвигателя является существенно нелинейная и немонотонная зависимость между управляющим цифровым кодом и

24 величиной сдвига фазы, приводящая к нелинейности зависимости времени

задержки от управляющего кода.

t.

Цель изобретения - обеспечение

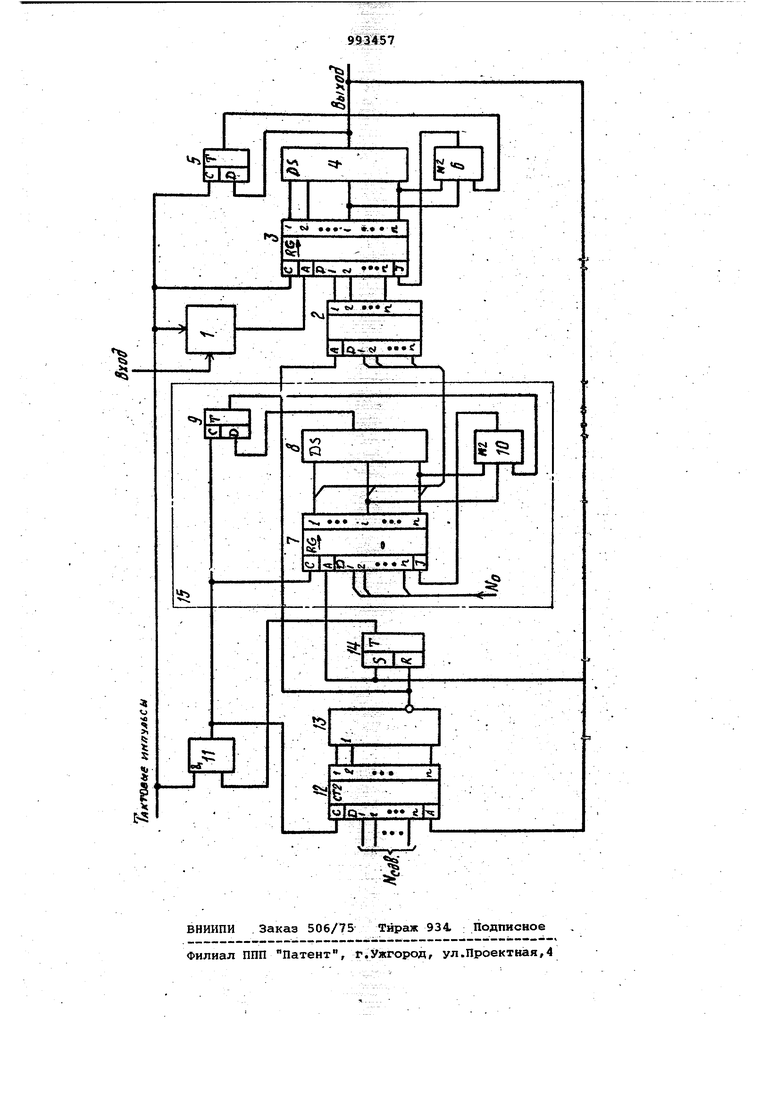

25 линейности управления задержкой импульсов. . Поставленная цель достигается тем, что в устройство, содержащее фазосдвигатель, состоящий из форми30рователя одиночных импульсов, ti -раа-( рядных сдвигающего регистра, буферного регистра и дешифратора, а также D -триггера и сумматора по модулю два, в котором тактовые входы формирователя одиночных импульсов, сдвигающего регистра и D-триггера соединены вместе и подключены к генератору тактовых импульсов, выходы буферного регистра подключены к входам параллельной записи сдвигающего регистра, выходы которого соединены с входами дешифратора, выход дешифратора подключен к JD -входу триггера, выход которого подключен одному из входов сумматора по модул два, два других входа которого соед нены с соответствующими выходами сдвигающего регистра, а выход соединен с входом последовательной записи сдвигающего регистра, введены кольцевой регистр, состоящий из второго п -разрядного сдвигающего регистра, второго п-разрядного .дешифратора, второго сумматора по модулю два и второго D -триггера а также вентиль, п -разрядный вычитающий счетчик, элемент ИЛИ-НЕ и R5 -триггер, причем первый вход вен тиля соединен с тактовыми входами формирователя одиночных импульсов, первого сдвигающего регистра и первого О-триггера, второй вход венти ля соединен с выходом .Rs- триггера, выход ве.нтиля соединен с тактовыми входами вычитающего с1етчика, второ го сдвигающего регистра и второго D -триггера, выходы вычитающего сче чика соединены с входами элемента ИЛИ-НЕ, выход которого подключен к 1 -входу R5-триггера и входу разреш ния переписи буферного регистра, вы ходы второго сдвигающего регистра соединены с входами второго дешифра ,тора и с входами параллельной запис буферного регистра, выход второго дешифратора соединен с О -входсяи вт рого D-триггера, выход которого по ключен к одному из входов сумматора по модулю два, два других входа которого соединены с двумя выходами второго сдвигающего регист ра, а Выход соединен с входом после довательной записи второго сдвигающ го регистра, выход первого дешифратора подключен к S-входу Й5 -триг Тера и к входам разрешения параллел ной записи вычитающего счетчика и второго сдвигающего регистра. На чертеже представлена принципиальная электрическая схема предла гаемого устройства. ; Устройство управляемой задержки .импульсов содержит фазосдвигатель, состоящий из формирователя 1 одиноч ных импульсов, буферного регистра 2, сдвигающего регистра 3 дешйфрат ра 4., D -1:ригге| а 5 и сумматора 6 ро модулю два, кольцевой регистр состоящий из сдвигающего регистра 7, дешифратора 8, D -триггера 9 и сумматора 10 по модул два, а также вентиль 11, вычитающий счетчик 12, элемент ИЛИ-НЕ 13 и R5-триггер 14, причем тактовые входы формирователя 1одиночных импульсов, сдвигающего регистра 3 и О -триггера 5, а также первый вход вентиля 11 соединены вместе, выходы буферного регистра 2подключены к входам параллельной записи сдвигающего регистра 3, выходы которого соединены с входами дешифратора 4, выход дешифратора 4 подключен к О -входу триггера 5, к 5 -входу триггера 14 и к входам разр1ешения параллельной записи сдвигающего регистра 7 и вычитающего счетчика 12, выход триггера 5, а также два входа сдвигающего регистра 3подключены к входам сумматора б, выход которого соединен с входом последовательной записи сдвигающего регистра 3, второй вход вентиля 11 соединен с выходом RS -триггера 14, выход вентиля 11 соединен с тактовыми входами вычитающего, счетчика 12, сдвигающего регистра 7 и D -триггера 9, выходы вычитающего счетчика 12 соединены -с входами элемента ИЛИ-НЕ 13, выход которого подключен к входу триггера 14 и входу разрешения переписи буферного регистра 2, выходы сдвигающего регистра 7 сое-. динены с входами дешифратора 8, выход дешифратора соединен с D -входом триггера 9, выходкоторого, а также два выхода сдвигающего регистра 7 соединены с входами сумматора 10, выход которого соединен с входом последовательной записи сдвигающего регистра 7. Входной сигнал подается на вход формирователя одиночных импульсов, на входы параллельной записи вычитающего счетчика подается код, управляющий задержкой импульсов входного сигнала, выход первого.дешифра тора является выходом устройства. Устройство работает следующим образом. Входной сигнал (импульс или видеосигнал) поступает на формирователь 1, импульс с выхода которого разрешает параллельную запись в сдвигающий регистр 3 кода, храняющегося в буферном регистре 2. Таким образе, при поступлении входного сигнала сдвигающий регистр 3 из любого состояния переходит в состояние К , onpefделяемое кодом, храняыщмся в буферном регистре 2. Сдвигающий регистр 3, дешифратор 4, 1 -триггер 5 и сумматор б по модулю два образуют замкнутую дискретную систему с Р состояниями, циклическй переходящими из одного в другое при поступлении очередного импульса на тактовые входы сдвигающего регистра 3, деишфратора 4 и триггера 5 Лпод cocTo ffHeM понимается совокупность п двоичных сигна- лов на выходе сдвигающего регистра 3 }. Количество состояний Р всегда меньше или равно 2 и определяется структурой (логикой) дешифратора 4 и номерами разрядов, сдвигаикцего регистра 3, подключенных к сумматору 6 Дешифратор 4 одно из состояний (обозначим его нсямер услов но через Р). Выходной импульс устройства. (импульс с выхода дешифратора 4) вырабатывается через Р-К TaKToJB после поступления входного .сигнала, что эквивалентно сдвигу или задержке входной импульсной последовательности при Р-К тактов. Значение К определяется работой остальной части устройства следующим образом. Импульс с выхода дешифратора 4 производит параллельную запись входного кода N(...g в вычитающий счетчик 12, кода NO в сдвигающий регистр 7 и взводит триггер 14, открывающий вентиль- 11. Совокупносз:ь регистра 7, детоифра ора 8,D -триггера 9, образующая кольцевой регистр 15, полностью идентичная совокупности регистра 3, дешифратора 4, D -триггера 5 и сумматора 6, следовательно, также имеет Р возможных СОСТОЯНИЙ, циклически переходящих из одного в другое в той же последовательности, что и в основном фазосдвигателе. Поскольку код NO соответствует логике дешифратора 8 (и, следовательно, дешифратора 4}, то под действием выходного импульса кольцевой регистр 15 всегда переходит в состояние, обозначенное нами через Р. Под действием этого же импульса в вычитагаций счетчик 12 записывается код управления задержкой , а сигнал с выхода триггера 14 открывает вентиль 11, начинает пропускать тактовые импульсы на тактовые входы вычитающего счетчика 12 и кольцевого регистра 15 Каждый тактовый импульс, прошедший через вентиль 11, уменьшает на едщницу содержимое счетчика 12 и увеличивает на единицу состояния кольцевого регистра 15, начиная с номера 1. Содержимое счетчика 12 уменьшится до нуля после того, как через вентиль 11 пройдет число такто вых импульсов, равное десятичному эквиваленту двоичного управляющего кода NCA, при этом на всех выхсщах счетчика 12 окажутся нулевые потенциалы и на выходе элемента ИЛИ-НЕ 13 образуется высокий потенциал, который опрокинет триггер 14. Выходной сигнал триггера 14 зак1Х)ет вентиль 11, после чего поступление тактовых импульсов на счетчик 12, а также на регистр 7 и .D -триггер 9 кольцевого регистра 15 прекратится. Кольцевой регистр 15 останется в состоянии, номер которого равен N(.. . Цифровой код на выходах сдвига1бщего регистра 7, соответствующий этому состоянию, импульсом с выхода элемента ИЛИ-НЁ 13 перепишется в буферный регистр 2. Теперь оря по-т ступлении очередного входного ямпуль са на вход формирователя 1 сщиночных импульсов в сдвигаюидай регистр 3 запишется код, соответствующей состоянию с номером K-N(iAB, а выходнойимпульс устройства на выходе дешифратора 4 появится через (Р-Исдв) тактов ., Таким образом, устройство сформирует выходной импульс с задержке на ( тактов относительно входного импульса. Зависимость величины задержки Т от управляющего кода является линейной (Р-Мсдб), где TQ - период тактовых импульсов. Выходной импульс с выхода дешифратора 4 произведет запись ксцда N в сдвигаккций регистр 7, взведет триггер 14 и запишет в счетчик 12 новое или прежнее значение (если оно не изменилось) управляющего кода Нсдв после чего весь процесс повторяется. Таким образом, предлагаемое устройство обеспечивает линейное управление задержкой импульсов при сохранении всех функций, присущих прототипу. При отсутствии одного или нескольких количеств импульсов по входной последовательности устройство обеспечивает восстановление пропущенных импульсов с задержкой, определяемой управляющим кодом. Устройство блокирует последовательность импульсов с периодом повторения меньшим, чем P-Ng.g) тактов, или блокирует любой люжный импульс, расположенный к преа:№1дущему ближе, чем на () тактов. При отсутствии входной импульсной последовательности устройство фо1М)Шрует импульсную последовательность с периодом Р тактов, т.е. произваш1Т деление частоты тактовых импульсов на Р. При выполнении всех этих функций значение Р ьюжет быть задано произвольным в предф1ах от 2 до 2 , а значение СА& может изменяться от О до Р. Формула изобретения Устройство управляемой задержки импульсов, содержащее фазосдвига-таль, состоящий из формирователя одиночных импульсов, Л -разрядных сдвигающего регистра, буферного регистра и дешифратора, а также D -триггера и сумматора по модулю два, в котором тактовые входы формирователя одиночных импульсов, сдвигающего регистра и D -триггера соединены вместе и подключены к входной шине тактовых импульсов, выходы буферного регистра подключены к входам параллельной записи сдвигающего регистра, ЁЫХОДЫ которого соединены с входами дешифратора, выход дешифратора подключен к D -входу триггера, выход которого подключен одному из входов сумматора по модулю два, два других входа которого соединены с соответствующими выходами сдвигающего регистра, а выход соединен с входом последовательной записи сдвигающего регистра, отличающееся тем, что, с целью обеспечения линейности управления задержкой импульсов, в него введены кольцевой регистр, состоящи из второго п-разрядного сдвигающег регистра, второго h -разрядного дешифратора, второго сумматора по модулю два, второго .О -триггера, а также вентиль, п .-разрядный вычитающий счетчик, элемент ИЛН-НЕ и 6s -триггер, причем первый вход вентиля соединен с тактовыми входами .формирователя одиночных импульсов.

первого сдвигающего регистра и пер- i вого D -триггера, второй вход вентиля соединен с выходом RS -триггера, выход вентиля соединен с тактовыми входами вычитающего счетчика, второго сдвигающего регистра и второго D -триггера, выходы вычитающего счетчика соединены с входами элемента ИЛИ-НЕ, выход которого подклй-г- чен к R -входу PS -триггера и входу

разрешения переписи буферного регистра, выходы второго сдвиганвдего регистра соединены с входами второго дешифратора и с входами параллельной записи буферного регистра, выход

второго дешифратора соединен с D-входом второго D -триггера, выход которого подключен к одному из входов второго сумматора по модулю два, два других входа которого соединены

с двумя выходами второго сдвигающего регистра, а выход соединен с вхо-i дом последювательной записи второго сдвигающего регистра, выход первого дешифратора подключен к З -входу

RS -триггера и к входам разрешения параллельной записи вычитающего счетчика,, и второго сдвигающего регистра.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 573865, кл. Н 03 К 5/153, 1976.

2.Авторское свидетельство СССР по заявке № 2968827/18-21

кл. Н 03 К 5/13, 19«0,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазосдвигатель | 1980 |

|

SU919070A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Частотный модулятор | 1989 |

|

SU1626320A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛА | 1986 |

|

SU1840550A1 |

| Параллельный анализатор спектра | 1981 |

|

SU1068835A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Устройство для сопряжения электронной вычислительной машины с абонентом | 1983 |

|

SU1137474A1 |

| Дискретный согласованный фильтр | 1978 |

|

SU771891A2 |

Авторы

Даты

1983-01-30—Публикация

1981-08-03—Подача