1

Изобретение относится к области цифровой вычислительной техники и может являться составной частью цифровой вычислительной машины.

Известны арифметические устройства (АУ) с сумматором накапливающего типа, в которых при выполнений операции умножения совмещаются по времени элементарные операции (ЭО): сдвиг кода множимого и формирование результата частичного произведения.

Недостатком таких устройств является необходимость использования нескольких дополнительных разрядов в сумматоре и в приемном регистре.

Целью изобретения является разработка арифметического устройства параллельного действия с сумматором накапливающего типа, в котором операция умножения выполняется за два такта и обеспечивается точность трехтактного накапливающего сумматора с использованием одного дополнительного разряда, т. е. повышение быстродействия устройства.

Для достижения этого вход первого элемента «И схемы определения несовпадения кодов i-ro разряда подключен к выходу элемента «ИЛИ схемы парафазного приема кода (/-1)-го разряда приемного регистра, выход элемента «НЕ которого подключен ко входу второго элемента «И схемы определения несовпадения кодов t-ro разряда, выход элемента «ИЛИ схемы определения несовпадения кодов i-ro разряда подключен ко входам третьего, второго и первого элементов

«И схем парафазного приема кодов соответственно (i+l)-ro, i-ro и (i-1)-го разрядов накапливающего регистра, вторые входы элементов «И соединены соответственно с шинами «Сдвига влево, «Сложения и «Сдвига

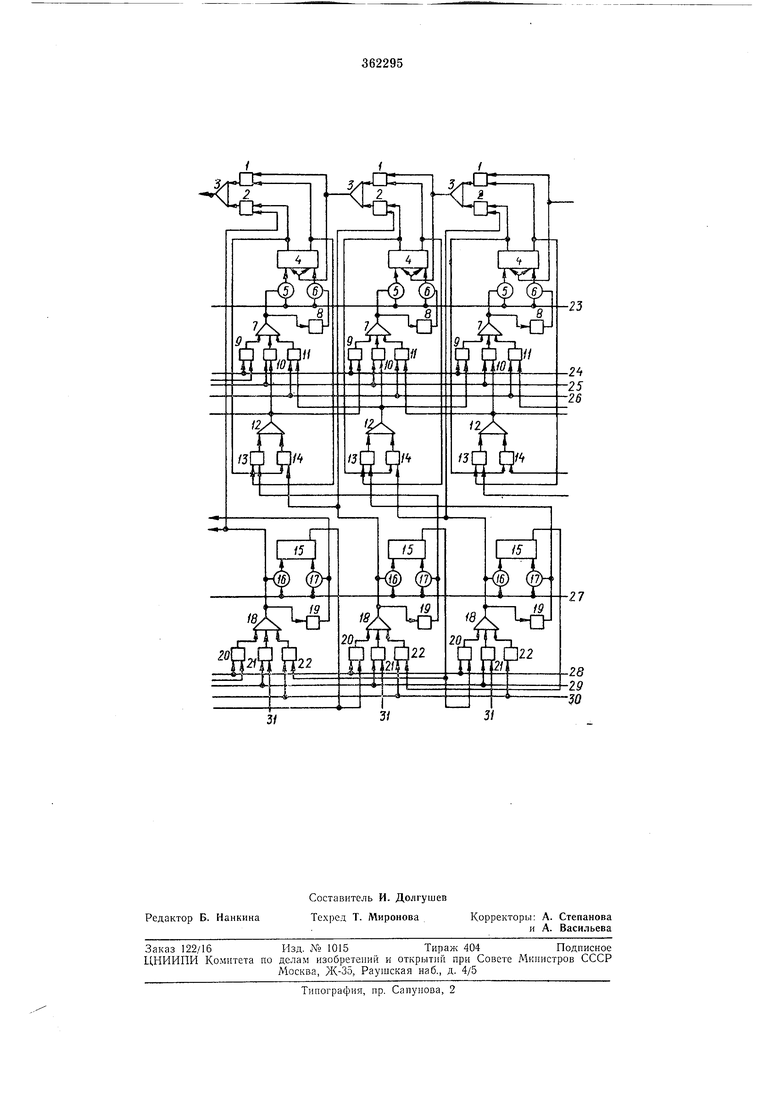

вправо, выход элемента «ИЛИ схемы парафазного приема кода /-го разряда приемного регистра соединен со входом первого элемента «И схемы сквозного переноса. Сущность изобретения поясняется чертежом, где приняты следующие обозначения: 1, 2 - с.хемы совпадения («И); 3 - схема сборки («или); 4 - триггер (Тг); 5-6 - установочные вентили (Вн); 7 - схема сборки («ИЛИ); 5 - инвертор («НЕ); 9-11-

схемы совпадения; 12 - схема сборки («ИЛИ); 13, 14 - схемы совпадения («И); 15 - триггер (Тг); 16, 17 - установочные вентили (Вн); 18 - схема сборки («ИЛИ); 19 - инвертор («НЕ); 20-22 - схемы совпадения («И); 23 - шина приема кода в накапливающий регистр (импульсное управление); 24 - шина разрешения сдвига кода накапливающего регистра вправо; 25 - шина разрешения сложения (вычитания); 26 -

шина разрешения сдвига кода накапливающего регистра влево; 27 - шина приема кода в приемный регистр (импульсное управление); 28 - шина разрешения сдвига кода приемного регистра вправо; 29 - шина разрешения приема кода в регистр; 30 - шина разрешения сдвига кода приемного регистра влево; 31 - числовая шина i-ro разряда.

Для упрощения чертежа здесь не приводится регистр множителя, показаны цепи сдвига кода в приемном и накапливаюшем регистрах только на один разряд влево и вправо, упрош,енно представлены схемы счетных входов триггеров накапливаюшего регистра.

Как видно по чертежу, единичный выход триггера 4 соединен со входами схем «И 1, «И 13. Нулевой выход этого триггера соединен со входами схем «И 2, «И 14. Единичный выход триггера 15 подключен к схеме «И 20 младшего разряда и к «И 22 старшего разряда.

Входы схем совпадения (-го разряда «И 13, «И 14 соединены соответственно с выходами инвертора «НЕ 19 и схемой «ИЛИ 18 (1-1)-го разряда. Выходы схем «И 13, «И 14 подключены ко входу схемы «ИЛИ 12, а выход последней соединен со схемами «И 11, «И 10, «И 9. Вторые входы «И 11, «И 10, «И 9 подключены к шинам 26, 25 и 24 соответственно.

Выходы этих схем совпадения подключены ко входу схемы «ИЛИ 7. Выход «ИЛИ 7 соединен с вентилем 5 и инвертором «НЕ «5, последний подключен к потенциальному входу вентиля 6. Импульсные входы вентилей 5 и 6 подключены к шине 23, а выходы - к нулевому и единичному входам триггера 4.

Выходы схем совпадения «И 20, «И 21, «И 22 подключены ко входу схемы «ИЛИ 18, а выход этой схемы сборки соединен со входом инвертора 19, с потенциальным входом вентиля 16 к с входами схем «И 14 и «И 2.

Импульсные входы вентилей 16 и 17 подключены к шине 27. Выходы этих вентилей подсоединены к нулевому и единичному входам триггера 15 соответственно.

Выходы схем «И 1, «И 2 подключены ко входу схемы «ИЛИ 3, а ее выход соединен со счетным входом триггера 4 и входом «И 1 старшего разряда. Здесь расслютрены соединения логических элементов в г-м разряде. В других разрядах АУ соединения аналогичны.

Рассмотрим работу АУ при выполнении операции умножения.

Как известно, выполнение операции умножения в простейшем случае сводится к многократным сложениям частичных произведений с множимым и сдвига полученных частичных произведений вправо или сдвига вправо множимого.

Будем считать, что перед началом выполнения операции умножения множитель хранится в регистре множителя {на чертеже не

показан), а множимое хранится в приемном регистре (триггеры 15). Накапливающий регистр (триггеры 4) установлен в нулевое состояние. Если в младшем разряде множителя

хранится код единицы, то необходимо выполнить сложение множимого с кодом, хранящимся в накапливающем регистре, и сдвинуть частичное произведение вправо.

В устройстве сложение кодов выполняется

за два временных такта, как и в известных АУ. Отличие состоит в том, что по первому временному такту выполняется сложение кодов по модулю 2 и одновременно производится сдвиг результата на один разряд вправо.

Выполнение этих ЭО (элементарных операций) осуществляется следующим образом.

На шины 28 и 24 подаются потенциалы, разрешающие сдвиг кодов в приемном и накапливающем регистрах вправо. В i-м разряД ; приемного и накапливающего регистров могут быть четыре возможных комбинации кодов: 00, 11, 10 и 01. Результат сложения по модулю 2 будет равен единице, тогда, когда значения кодов в рассматриваемом разряде

чк совпадают. Если в приемном регистре /-ГО разряда хранится код единицы, а в триггере 4 накапливающего регистра записан нуль, то со схемы совпадения «И 14 на вход схемы сборки «ИЛИ 12 и далее на «И

9 поступит сигнал. Этот сигнал закроет вентиль 5 и откроет вентиль 6, т. е. подготовит вентили триггера младшего разряда для записи единицы. Исполнительный импульс, поданный на шину 23, выполнит одновременпо ЭО сложения по модулю 2 и сдвиг результата сложения на однн разряд вправо.

По второму временному такту вырабатываЮ1СЯ сигналы нереноса и формируется результат частичного произведения.

Перенос из г-го разряда в (/+1)-й разряд может быть выработан только в том случае, когда после первого временного такта триггер 4 установлен в нулевое состояние, а в триггере 15 ()-ro разряда хранится код

единицы. Потенциал единицы триггера 15 по цепи: «И 20, «ИЛИ 18; «И 2, «ИЛИ 3 поступает на вентили счетного входа триггера 4, формируя тем самым результат частичного произведения.

Одновременно с формированием частичного ироизведения выполняется сдвиг множителя и анализируется младший разряд регистра множителя. При наличии в нем едииицы снова повторяется сложение и сдвиг частичиого произведения. В этом случае, если в младшем разряде хранится нуль, то сложение не выполняется, а производится только сдвиг кода иакапливаюшего регистра. При этом с шины 28 снимается управляющий потенциал, т. е. работой схемы определения несовпадения кодов будут управлять только единичные выходы триггеров накапливающего регистра. Первый временной такт, поступивщий на шину 23, сдвинет код накапливающего регистра вправо на один разряд, т. к.

потенциал единицы триггера 4 по цепи: «И 13, «ИЛИ 12, «И 9, «ИЛИ 7 закроет вентиль 5 и откроет вентиль 6 триггера младшего разряда.

Если в триггере 4 (i-1)-го разряда хранился нуль, то вентиль 5 нулевого входа триггера 4 г-го разряда будет открыт, а вентиль 6 закрыт, т. е. код нуля будет сдвинут вправо на один разряд.

Таким образом, путем многократных еложенйй и сдвигов частичных произведений выполняется операция умножения. За счет того, что во время умножения код множимого не сдвигается, можно получить 2 п-разрядное произведение, сдвигая код частичных произведений в старшие разряды регистра множителя.

Аналогичным способом выполняется операция деления чисел. Отличие состоит только в том, что результат сложения по модулю два сдвигается влево, а во время формирования переноса снимается управляющий потенциал с шины 28 и подается на шину 30.

Операция сложения (вычитания) выполняется следуюпдим образом.

По первому временному такту на шины 28 и 25 подается разрешающий потенциал. Если Б рассматриваемом разряде имеет место сочетание кодов в приемном и накапливающем регистрах 10 или 01, то с выхода логического элемента «ИЛИ 12 на вход схемы совпадения «И 10 поступит сигнал, этот сигнал по цепи: «И 10, «ИЛИ 7 закроет вентиль 5 и за счет инвертора «НЕ 8 откроет вентиль 6.

Исполнительный импульс, поступивщий на шину 23, сформирует в накапливающем регистре результат сложения двух чисел по модулю 2.

Исполнительный импульс подается также на щину 27, за счет чего код приемного регистра сдвигается на один разряд вправо. Это необходимо для формирования переноса.

По второму временному такту на щину 30 подается разрешающий потенциал. Сигнал переноса из любого разряда в старщий разряд может быть сформирован в том случае, если триггер накапливающего регистра находится в нулевом состоянии, а триггер приемного регистра - в единичном. Так как во время первого такта был произведен сдвиг кода приемного регистра на один разряд вправо, то в формировании сигнала переноса г-го разряда будет принимать участие триггер (t-1)-го разряда приемного регистра.

Единичный потенциал триггера (i-1)-го разряда по цепи: «И 22, «ИЛИ 18 поступает на вход логического элемента «И 2, второй вход которого подключен к нулевому выходу триггера г-го разряда накапливающего регистра. Если этот триггер находится в нулевом состоянии, то сигнал переноса из f-ro разряда через схему «ИЛИ 3 поступит на счетный вход триггера (г+1)-го разряда. Кроме того, выработанный сигнал переноса через «И 1, «ИЛИ 3 поступит в следующий старший разряд, если триггер (r-f 1)-го разряда находится в единичном состоянии.

Таким образо.м, в накапливающем регистре будет сформирован результат сложения кодов двух чисел.

Предмет изобретения

Арифметическое устройство параллельного действия, содержащее приемный и накапливающий триггерные регистры, схемы парафазного приема и сдвига кодов, каждая из которых состоит из трех элементов «И, выходы которых соединены со входами элемента «ИЛИ, выход элемента «ИЛИ соединен со входом элемента «НЕ, поразрядные схемы определения несовпадения кодов в приемном и накапливающем регистрах, содержащих два элемента «И, выходы которых соединены со входами элемента «ИЛИ, схемы сквозного переноса, каждая из которых содержит два элемента «И, выходы которых соединены со входами элемента «ИЛИ, отличающееся тем, что, с целью повышения быстродействия устройства, вход первого элемента «И схемы определения несовпадения кодов г-го разряда подключен к выходу элемента «ИЛИ схемы парафазного приема кода (i-1)-го разряда приемного регистра, выход элемента «НЕ которого подключен ко входу второго элемента «И схемы определения несовпадения кодов г-го разряда, выход элемента «ИЛИ с.хемы определения несовпадения кодов i-ro разряда подключен ко входам третьего, второго и первого элементов «И с.хем парафазного приема кодов соответственно (f-fl)-ro, г-го и (i-1)-го разрядов накапливающего регистра, вторые входы элементов «И соединены соответственно с шинами «Сдвига влево, «Сложения и «Сдвига вправо, выход элемента «ИЛИ схемы парафазного приема кода г-го разряда приемного регистра соединен со входом первого элемента «И схемы сквозного переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1971 |

|

SU318941A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| УЗЕЛ СДВИГА АРИФМЕТИЧЕСКОГО УСТРОЙСТВА | 1970 |

|

SU279170A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1969 |

|

SU248778A1 |

| Устройство для умножения | 1985 |

|

SU1252774A1 |

Авторы

Даты

1973-01-01—Публикация