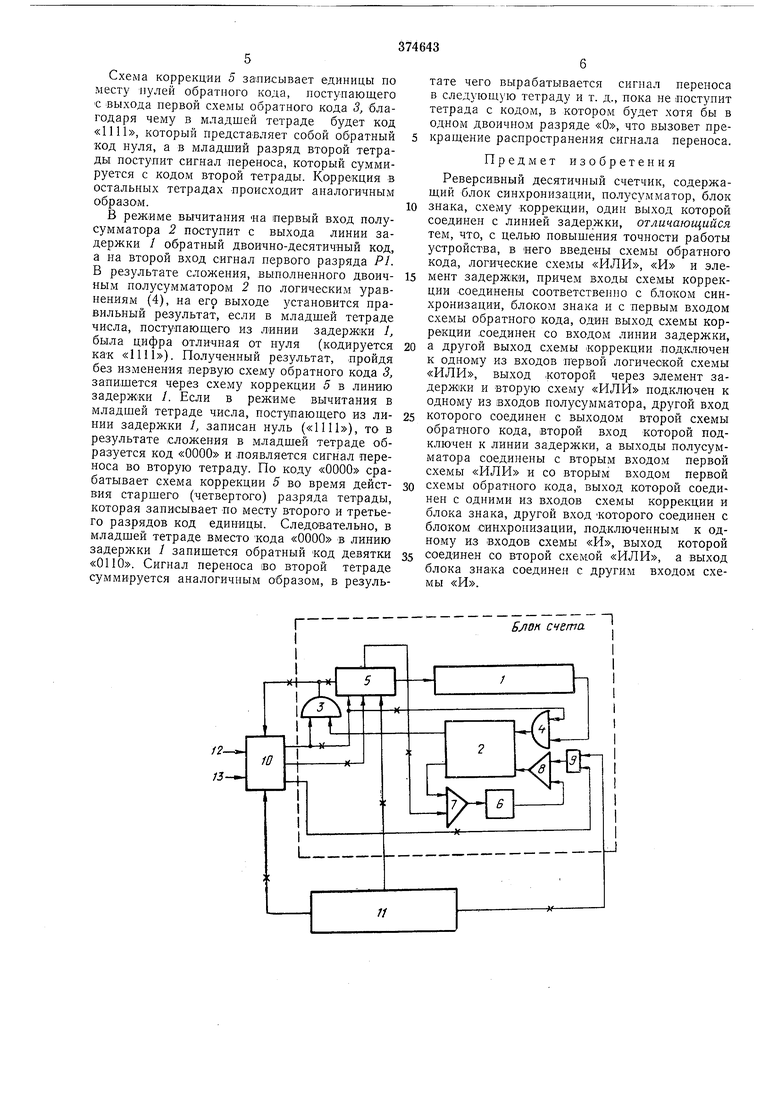

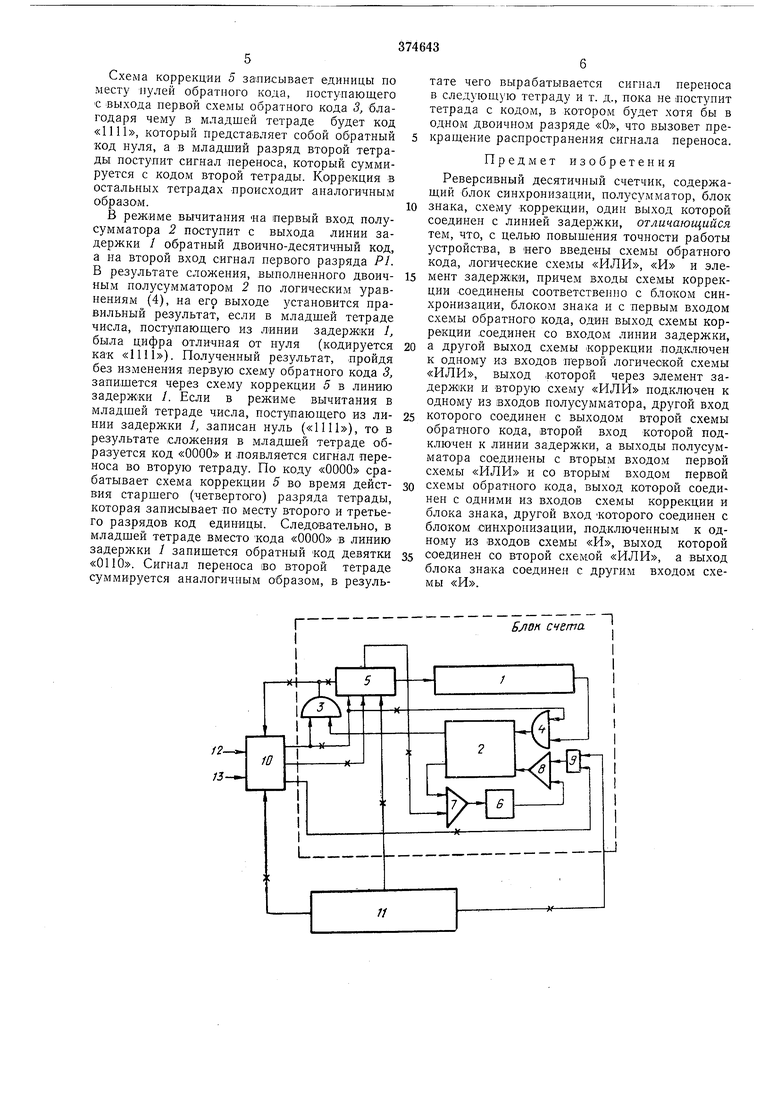

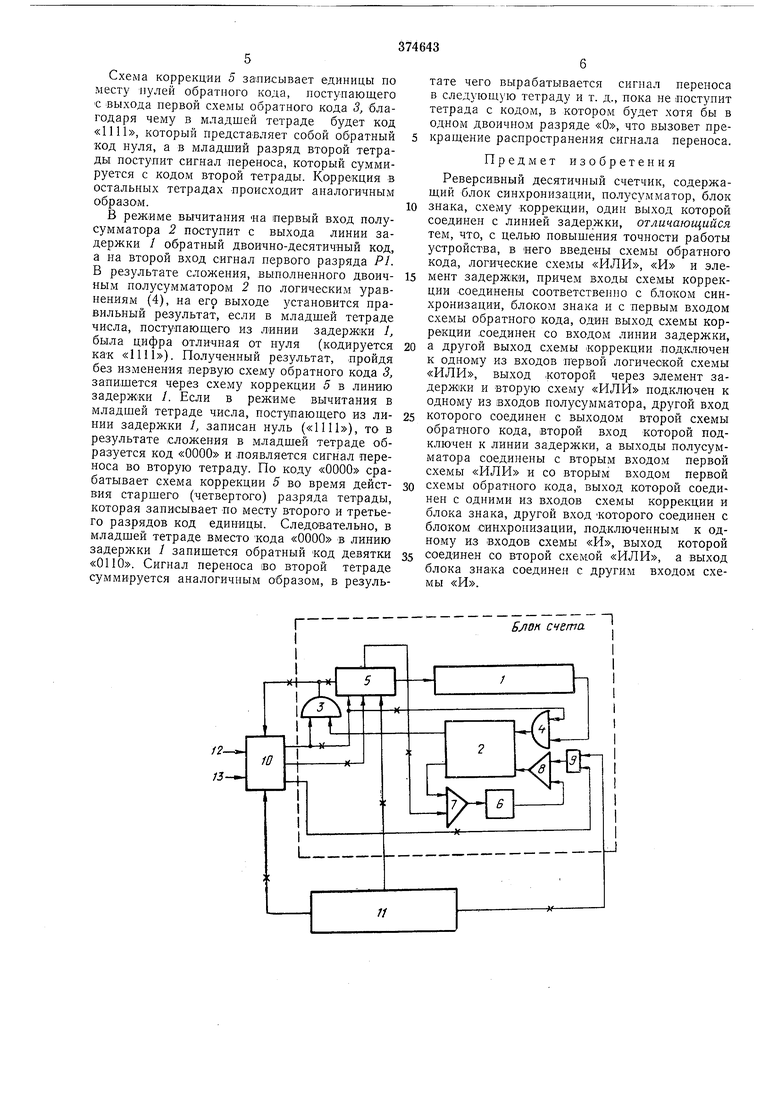

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для построения различных автоматических iH вычислительных устройств (подсчет количества производимой продукции за вычетом брака; сравнение количества двух входных воздействий, поступающих последовательно во времени; построение цифровых интегрирующих машин и т. п.). В известных схемах реверсивных десятичных счетчиков большой емкости (коэффициент пересчета ) оборудование растет пропорционально количеству разрядов счетчика. Помимо того известные схемы реверсивных счетчиков последовательного действия строятся, как правило, В двоичной системе счисления, что требует применения преобразователя кодов чисел. Цель изобретения состоит в построении простой схемы реверсивного десятичного счетчика большой ем:кости, оборудование которого практически не зависит от требуемого коэффициента пересчета, а результат фиксируется в десятичном виде как для отрицательных, так и для положительных чисел. В предлагаемом устройстве эта цель достигается путем выполнения схемы реверсивного десятичного счетчика большой емкости на базе линии задержки последовательного двоичного полусумматора, схемы коррекции, двух схем обратного кода и блока знака. На чертеже изображен реверсивный десятичный счетчик большой емкости. Он состоит из линии задержки 1, последовательного двоичного полусумматора 2, двух схем обратного кода 3 я 4, схемы коррекции 5, элемента задержки на один период тактовой частоты 6, схем «ИЛИ 7, 8, схемы «И 9, блока знака 10 и блока синхронизации //. Блок знака 10 определяет режим работы реверсивного счетчика (сложение или вычитание положительных 12 или отрицательных 13 входных сигналов) и фиксирует знак результата. В случае суммирования выдается сигнал по первому выходу блока знака, соединенному со входом схемы коррекции 5 и входами схем обратного кода 3 и 4, Е случае вычитания .выдается сигнал по второму выходу блока знака, соединенному со вторым входом схемы коррекции 5. И ъ том и в другом случае выдается выходной сигнал блока знака 10 по третьему выходу, который соединен со входом схемы «И 9, на второй вход которой поступают выходные сигналы блока синхронизации //. Выходные сигналы с других двух выходов блока синхронизации 11 поступают на вход блока знака и на вход блока коррекции. Помимо этого четвертый (Вход схемы коррекции 5 соединен с выходом первой схемы обратного кода 3. Результат коррекции поступает на первый выход схемы 5 который соединен со входом линии задержали /. Кроме этого в режиме сложения выдается сигнал по второму выходу схемы коррекции 5, соединенному с первым входом схемы «ИЛИ 7. Выход линии задержки 1 соединен с первым входом второй схемы обратного кода 4, второй вход которой Соединяется с первым выходом блока знака 10. Выход схемы обратного кода 4 поступает на первый вход последовательного двоичного полусумматора 2, выход сигнала суммы которого соединен с первым входом схемы обратного кода 3. На второй вход первой схемы обратного кода 3 поступает сигнал с первого выхода блока знака 10. Выход сигнала переноса сумматора 2 соединен со вторым входом схемы «ИЛИ 7, выход которой через элемент задержки 6 соединен с первым входом схемы «ИЛИ 8. Второй вход схемы «ИЛИ 8 соединен с выходом схемы «И 9, первый вход которой соединен с третьим выходом блока знака 10, а второй - с блоком синхронизации 11. Выход схемы «ИЛИ 8 поступает на второй вход сумматора 2. Линия задержки предназначена для получения и запоминания результата счета в двоично-десятичном коде. Величина задержки TI между входом схемы коррекции 5 и выходом линии задержки 1 определяется по формуле - 0) где п - количество десятичных разрядов; f - частота тактовых сигналов. Величина задержки TI должна удовлетворять неравенству р -± макс где макс - максимально возмояшая частота Поступления входных счетных сигналов. Так, для я 8 и / 250 кгц величина задержки TI согласно формуле (1) равна 1:1 1,28-10-4 се«: 128 жксек. При таком значении TI максимально возможная частота поступления входных счетных сигналов в соответствии с неравенством (2) не должна превышать 7,8125 кгц. Величина задержки Та между входом и выходом линии задержки / определяется по формуле4.(-2) 7 и для тех же значений f и я равняется Та 1,2-10-4 мксек. Последовательный двоичный полусумматор 2 собран согласно известным логическим соотношениямS XyyXY, Z XY. где S, Z, X, Y, X и Y - двоичные переменные сигнала суммы, сигнала переноса, прямые и инвертированные сигналы по первому и второму входам полусумматора соответственно. Блок знака фиксирует знак результата, задает режимы работы устройства (сложение, вычитан.ие, отсутствие счета, установка в исходное состояние). Блок синхронизации предназначен для выработки сигналов, синхронизирующих работу всего устройства. В предлагаемой схеме реверсивного десятичного счетчика абсолютная величина результата хранится в обратном коде в двоичнодесятичной системе счисления 8421. Рассмотрим работу блока счета в режиме сложения. В исходном состоянии или в режиме запоминания, которые могут предшествовать режиму сложения, двоично-десятичный обратный код абсолютной величины циркулирует без изменения по цепи: выход линии задержки /-вторая схема обратного кода 4- полусумматор 2-первая схема обратного кода 3 -схема коррекции 5 - вход линии задержки 1. Первый же входной сигнал, устанавливающий в блоке знака режим сложения, приводит к тому, что на первом и третьем выходах блока знака 10 установятся сигналы, которые нереключат схемы обратного кода 3 н 4 ъ режим инвертирования. Поскольку с выхода линии задержки / поступает обратный код, то на выходе второй схемы обратного кода 4 установится прямой двоично-десятичный код, который поступит на первый вход полусумматора 2. Так как с третьего выхода блока знака поступает -разрешение на схему «И 9, то сигнал младшего первого разряда Р1 проходит через схему «И 9, «ИЛИ 8 на второй вход полусумматора. Если во время действия первого разряда по первому входу полусумматора 2 также поступает код единицы, то согласно логическим выражениям .(4) 5 0, а сигнал переноса Z 1 через схему «ИЛИ 7, элемент задержки 6 и схему «ИЛИ 8 поступит на второй вход полусумматора 2 уже во время действия сигнала второго разряда. Таким образом, двоичный код младшей тетрады увеличится на одну единицу. В результате на выходе полусумматора установится правильный результат в прямом двоично-десятичном виде, если число в младшей тетраде не превышает «9. Этот код первой схемой обратного кода 3 опять превращается в обратный двоично-десятичный код, который через схему коррекции 5 заносится в линию задержки 1. Как только в младшей тетраде установится код десяти «1010, срабатывает схема коррекции 5 во время действия последнего (четвертого) разряда тетрады и на втором выходе схемы коррекции 5 появляется сигнал, который через схему «ИЛИ 7 поступает по цепи переноса полусумматора 2 в младший разряд следующей (второй) тетрады.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный десятичный счетчик | 1979 |

|

SU822381A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ КОЛИЧЕСТВА ГРАВИТАЦИОННЫХ МОРСКИХ ВОЛН | 1973 |

|

SU430408A1 |

| УСТРОЙСТВО для РЕГИСТРАЦИИ КОЛИЧЕСТВА ГРАВИТАЦИОННЫХ МОРСКИХ ВОЛН | 1972 |

|

SU337795A1 |

| ЙС^ЮОЮЗНАЯ I | 1973 |

|

SU372568A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Десятичный вычитающий счетчик | 1979 |

|

SU809584A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Счетчик импульсов | 1979 |

|

SU790346A1 |

| ПОКАЗАНИЙ ПРИБОРОВ УЧЕТА РАСХОДА | 1971 |

|

SU291097A1 |

Авторы

Даты

1973-01-01—Публикация