f

Изобретение относится .к области автоматики и вычислительной техники и может найти применение в различных областях техники промышленности для счета однотипных входных воздействий любой физической природы, например для подсчета количества производимой продукции и его расхода, сравнения двух последовательностей импульсов и т. п. ;

Известны Десятичные реверсивные счетчики, содержащие регистр сдвига, блок знака, блок коррекции, блок синхронизации и два трехвходовых двоичных сумматора 1.

Известен также реверсивный дес 1тичный счетчик, содержащий блок синхронизации, блок знака, блок коррекции, первый и второй блоки обращения кода, элемент ИЛИ и регистр сдвига, первый выход блока синхронизации соединен с первым входом блока знака, второй и третий входы которого соединены соответственно с суммирующим я вычитающим входами реверсивного десятичного счетчика, первый выход блока коррекции соединен с входом регистра сдвига, первый вход элемента ИЛИ соединен с вторым выходом блока коррекции, первый вход которого соединен с выходом первого блока обращения кода и с четвертым входом блока знака, первый выход которого сое- . динен с первым входом второго блока обращения кода и вторым входом блока коррекции,третий вход которого соединен с вторым выходом блока синхронизации а первый вход первого блока обращения кода соединен с.выходом

0 регистра сдвига 2.

Недостатком этих реверсивных десятичных счетчиков является относительно низкое быстродействие.

Целью изобретения является повышение быстродействия.

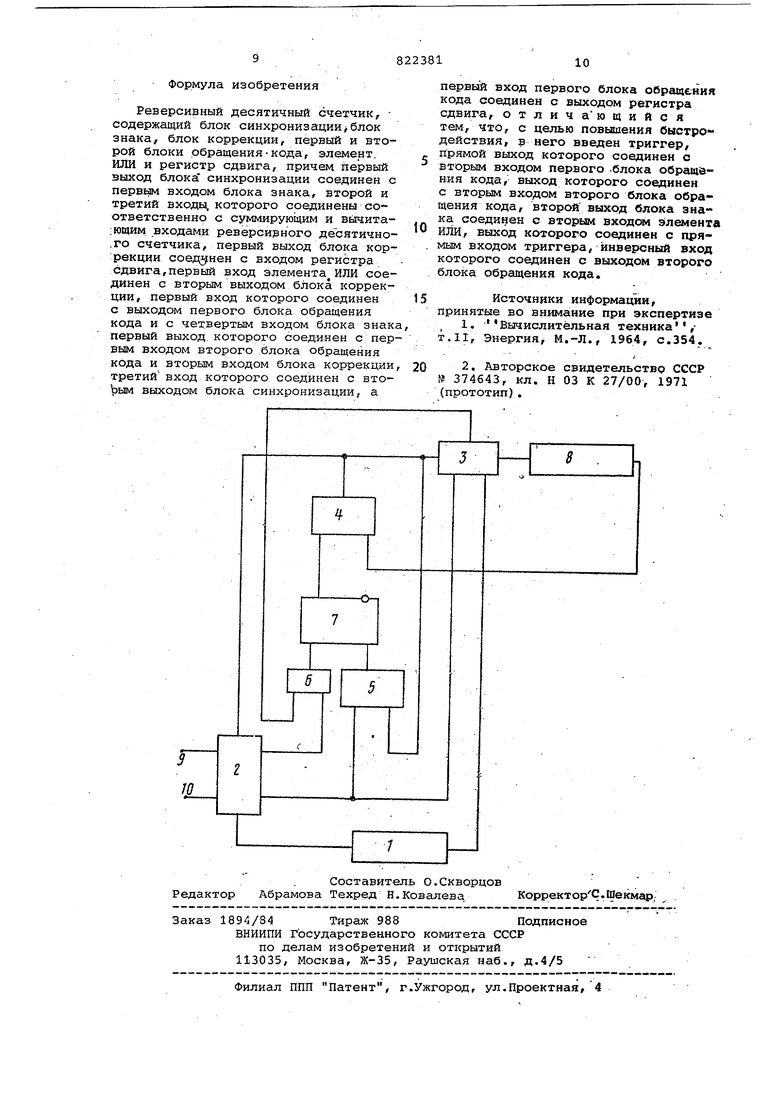

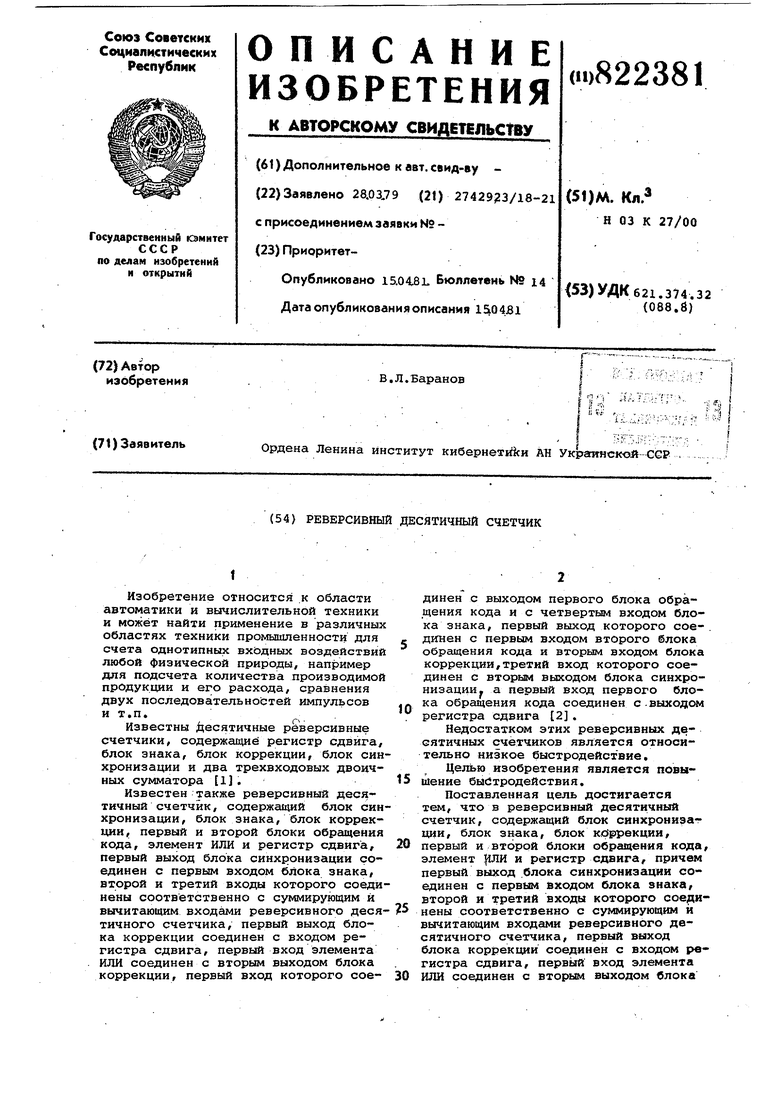

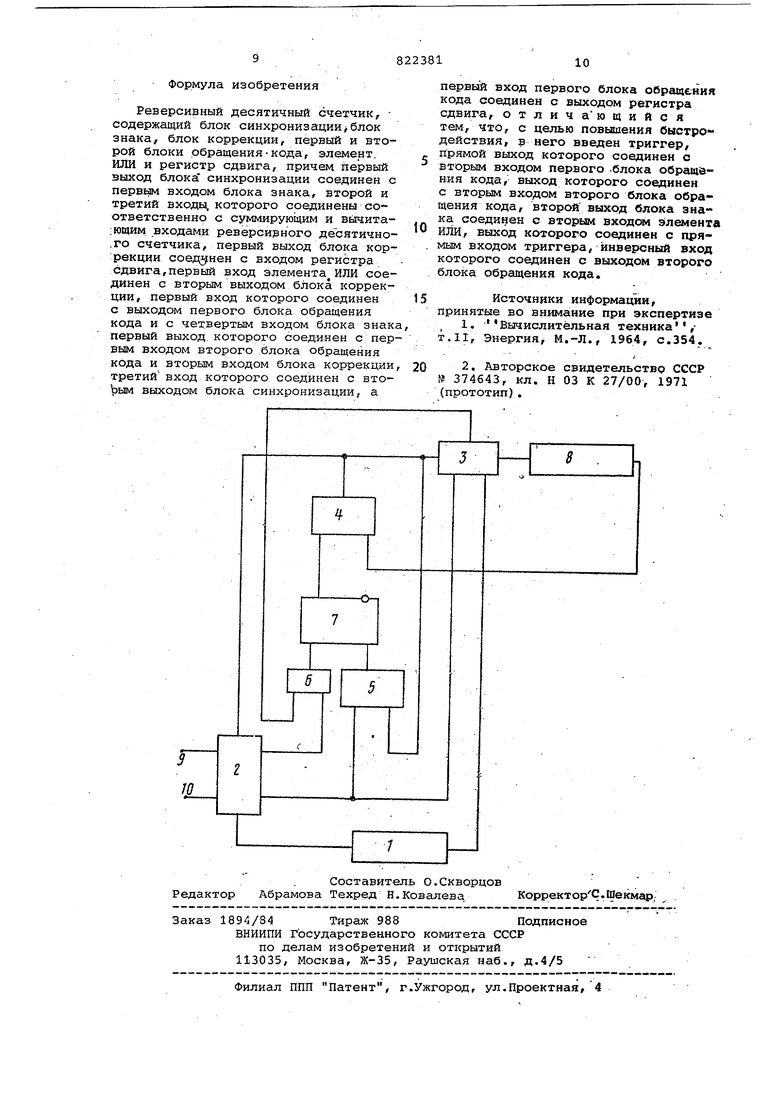

Поставленная цель достигается тем, что в реверсивный десятичный счетчик, содержащий блок синхронизации, блок знака, блок коррекции,

0 первый и второй блоки обращения кода, элемент |1ЛИ и регистр сдвига, причем первый выход блока синхронизации соединен с первым бходом блока знака, второй и третий входы которого соеди5нены соответственно с суммирующим и вычитающим входами реверсивного десятичного счетчика, первый выход блока коррекции соединен с входом регистра сдвига, первый вход элемента

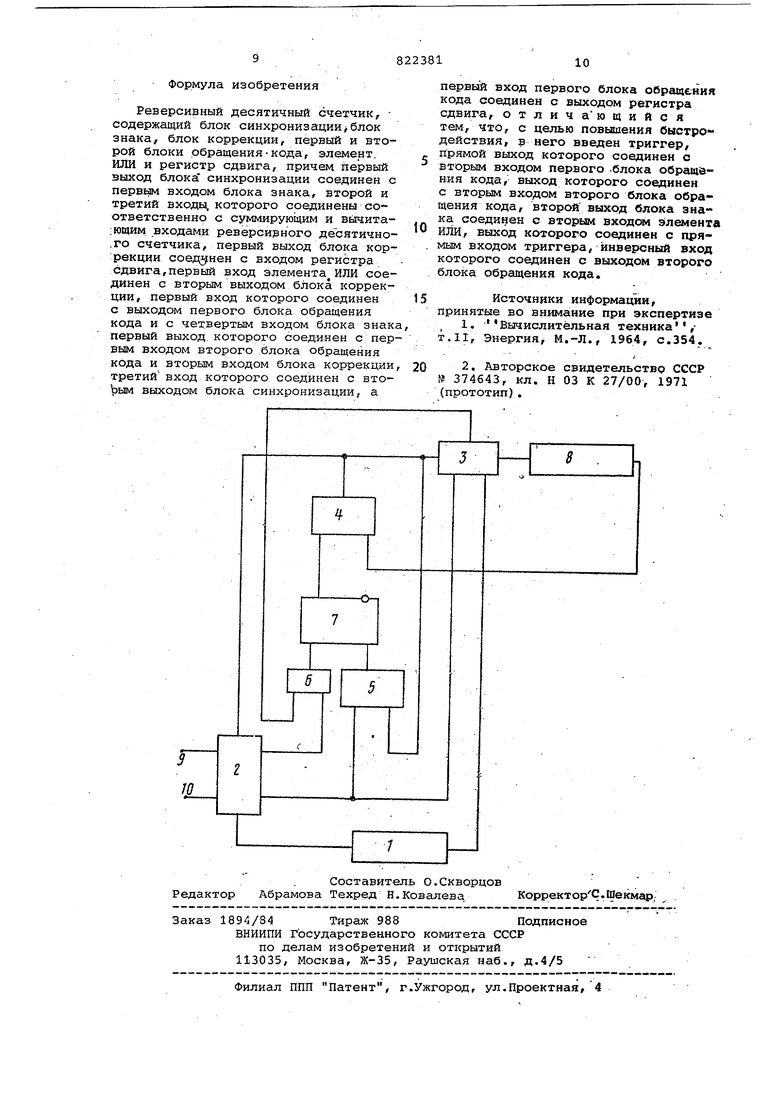

0 ИЛИ соединен с вторым выходом блока коррекции, первый вход которого соединен с выходом первого блока обраще ния кода и с четвертым входом блока знака, первый выход которого соединен с первым входом второго блока обращени кода и .вторым входом блока коррекции, третий вход которого соединен с вторым выходом блока син хройизации, а первый вход первого блока обращения кода соединен с выходом регистра сдвига, введен триг гер, прямой выход, которого соединен с вторым входом первого блока обращения кода, выход которого соединен с вторым входом второго блока обращения кода, второй выход блока знак соединен с вторым входом элемента ИЛИ, выход которого соединен с прямым входом триггера, инверсный вход которого соединен с выходом второго блока обращения кода. Структурная схема реверсивного десятичного счетчика показана на чертеже. Реверсивный десятичный счетчик содержит блок синхронизации 1, блок знака 2, блок коррекции 3, первый 4 и второй 5 блоки обращения кода, элемент ИЛИ б и триггер 7, и регистр сдвига 8. Первый выход блока синхронизации 1 соединен с первым входом блока знака 2, второй и третий входы которого соединены соответственно с суммирукндим 9 и вычитающим 10 входами реверсивного десятичного счетчи ка, первый выход блока коррекции 3 соединен с входом регистра сдвига 8 первый вход элемента ИЛИ б .соединен с вторым выходом блока коррекции 3, первый вход которого соединен с выходом первого блока обращения кода 4 и с четвертым входом блока знака 2, первый выход которого соединен с пер вым входом второго блока обращения кода 5 и вторым входом блока коррекции 3, третий вход которого соединен с вторым выходом блока синхронизации 1, а первый код первого блока обращения кода 4 соединен с выходом регистра сдвига 8, прямой выход тригге ра. 7 соединен с вторым входом первог блока обращения кода 4, выход которо го соединен с вторым входом блока об ращения кода 5, второй выход блока знака 2 соединен с вторым, входом элемента ИЛИ 6, выход которого соеди нен с прямым входом триггера 7 инверсный вход которого соединен с выходом второго блока обращения кода 5. Реверсивный десятичный счетчик ра ботает следующим образом. Блок синхронизации 1 вырабатывает тактовые импульсы, которые используются в качестве сдвиговых импульсов регистра сдвига 8, причем блок синхронизации 1 вырабатывает по первому выходу синхронизирующие сигналы с частотой 4 - f -t J где f - частота тактовых сигналов/ п - количество двоичных разрядов регистра сдвига 8, и по второму выходу - синхронизирующие сигналы с частотой Ч 4 Количество двоичных разрядов регистра сдвига 4 выбирается согласно соотношению , где m - количество десятичных разрядов (тетрад) счетчика. Блок коррекции 3 представляет собой регистр сдвига на два разряда и совместно с регистром сдвига 8 образует последовательный регистр на 4т двоичных разрядов. Блок знака 2 вырабатывает по первому выходу сигнал, определяющий режим работы реверсивного счеагчика ., (сложение или вычитание), фиксирует знак результата и обеспечивает синхронизацию поступления счетных импульсов по второму выходу в моменты считывания с выхода регистра 8 первого (младшего) разряда двоично-десятичного кода 8-4-2-1. В исходном состоянии триггер 7 находится в нулевом состоянии и на его прямом выходе действует нулевой логический сигнал, при котором блок обращения кода 4 пропускает без изменения последовательный двоично-десятичный код с выхода регистра сдвига 8 на первый вход блока коррекции 3. Таким образом, цепь циркуляции двоично-десятичного кода в последовательном регистре, состоящем из блока коррекции 3 и регистра сдвига 8, Зс1мкнута. Исходное состояние счетчика сохраняется до прихода на суммирующий 9 либо вычитающий 10 входы последовательности входных импульсов. В режиме сложения счетчик работа ет следующим образом. Блок знака 2 в режиме сложения вырабатывает на первом выходе нулевой лргический сигнал, по которому блок обращения кода 5 переходит в состояние передачи в прямом коде сигнсшов с его второго входа на выход, а блок коррекции 3 переходит в состояние, положительной коррекции по запрещенному коду 1010. Первый импульс счетчика, посту- пающий по суммирующему В24оду 9,синхронизируется импульсом первого выхода блока синхронизации 1 и выдается по второму выходу блока знака 2. Этот импульс проходит через элемент ИЛИ 6 на вход установки триггера 7

и переводит его в единичное логическое состояние к моменту считывания младшего разряда двоично-десятичного кода с выхода регистра сдвига 8. Переход триггера 7 в единичное логическое состояние приводит к переключению блока обращения кода 4 в режим инвертирования последовательного кода, поступающего на его первый вход с выхода регистра.сдвига 8.

Инвертированный двоично-десятичный код последовательно, начиная с , младшего разряда,, записывается с выхода регисч- за сдвига 8 на его вход через блок обращения кода 4 и блок коррекции 3 до тех пор, пока триггер 7 не возвратится в нулевое логическое состояние и не переведет блок обращения кода 4 в режим передачи прямого кода, поступающего с выхода регистра сдвига 8.

Триггер 7 возвратит в нулевое состояние первая единица инвертированного двоично-десятичного кода, начиная с младшего разряда младшей тетрады, которая с выхода блока обращения .кода 4 проходит без изменения через блок обращения кода 5 на инверсный вход триггера 7, а также записывается в блок коррекции 3.

Триггер 7 устанавливается в нулевое логическое состояние после первой единицы инвертированного двоично-десятичного кода и переЕ одит блок обращения кода 4 в режим передачи прямого кода.

Таким образом, после первой единицы в инвертированном двоично-десятичном коде остальные разряды кода с выхода регистра сдвига 8 передаются блоком обращения кода 4 в прямей коде, что приводит к увелиЧению двоичного кода младшей тетрады на одну единицу. .

Действительно, , например, начальный двухтетрадный код был нулевым ОООО.ОООО., то в его инвертированном коде единица сформируется в первом же разряде младшей тетрады, которая записывается в регистр, образованный блоком коррекции 3 и регистром сдвига 8. Остальные же разряды начального двоично-десятиЗДого кода,- начиная с второго разряда младшей тетрады, переписываются без изменения, .что дает в результате код 0000.0001 (один).

Если, например, с выхода регистра сдвига 4 считывается двоично-десятичный код 0000.0111 (семь), то в его инвертированном коде первая единица сфЬрмируется в четвертом разряде младшей тетрады, после которой двоичный код второй тетрады переписывается в прямом коде. В результате сформируется двоично-десятичный код ОООО.ЮОО (восемь).

Следовательно, в младшей тетраде двоично-десятичного кода осуществляется двоичный счет благодаря управлению блоком обраще.ния кода 4 сигналами прямого выхода триггера 7.

Блок коррекции 3 в режиме двоичного счета от О до 9 выполняет функцию регистра сдвига на два разряда, дополняя регистр сдвига 8 до 4т двоичных разрядов.

Десятый входной импульс, действующий на суммирующем входе- 9, изменит состояние младшей тетрады на за0прещенный код lOlO, по которому срабатывает блок, коррекции 3 по синхронизирующему сигналу четвертого разряда, поступающему с второго выхода блока синхронизации 1 на третий

5 вход блока коррекции З.Блок коррек- ции 3 в режиме суммирования формц- рует по коду 1010 на его втором выходе сигнал, который закрывает на один такт цепи сдвига в блоке коррек0- ции 3, стирая единицы во втором и

четвертом разрядах младшей тетрады, Сигнал коррекции со второго выхода блока коррекции 3 поступает через элемент ИЛИ б на прямой -вход триггера 7, устанавливая его в единичное

5 состояние, что приводит к переходу блока обращения кода 4 в режим инвертирования к моменту считывания младшего разряда второй тетрады с выхода регистра сдвига 8.Таким образом

0

осуществляется переход двоичного счета во вторую тетраду, в которой пре-. образование кодов осуществляется аналогично описанному выше преобразованию кодов в первой тетраде.

5 в результате после десяти входных импульсов в режиме суммирования образуется двоично-десятичный код . 0001.0000 (десять).

Дальнейший двоичный счет в тетраQ дах и десятичный переход счета из младшей тетрады в старшую в режиме суммирования осуществляется аналогичным образом.

В режиме вычитания счетчик работает следующим образом. .

Блок знака 2 в режиме вычитания вырабатывает на первом выходе единичный логический сигнал, по которому блок обращения кода 5 переходит в состояние инвертирования сигналов,

0 поступающих на его второй вход с

выхода блока обращения кода 4. Кроме того, единичный логический сигнал первого выхода блока знака 2 посту- I пает на второй вход блока коррекции

5 3 и переводит его в состояние отрицательной коррекции по запрещенному коду 1111.

Входной импульс счетчика, поступающий по вычитающему входу 10, синхронизируется импульсом первого выхода блока синхронизации 1 и выдается к второму выходу блока знака 2. Этот импульс проходит через элемент ИЛИ б на установочный вход триггера

5 7 и переводит его в единичное логическое состояние к моменту считывания младшего разряда дврично-десятичного кода с выхода регистра сдвига 8 Переход триггера 7 в единичное логическое состояние приводит к переключению обращения кода 4 в режим инвертирования последовательного кода поступающего на его первый вхой G выхода регистра сдвига 8.

Инвертированный двоично-десятичны код последовательно, начиная с младшего разряда, записывается с выхода регистра сдвига 8 на его вход через блок обращения кода 4 и блок коррекции 3 до тех пор, пока триггер 7 не возв1эатится в нулевое логическое состояние и не переведет блок обраще ния кода 4 в режим передачи прямого кода, поступающего с выхода регистра сдвига 8. ,

Триггер 7 возвратит в нулевое логическое состояние первый нуль инвертированного двоично-десятичного кода, начиная с младшего разряда младдаей тетрады, который с выхода блока обращения кода 4 поступает на второй вход блока обращения кода 5, где инвертируется в единичный логический сигнал, поступающий на вход сброса триггера7.

Триггер 7 устанавливается в нулевое логическое состояние после первого нуля инвертированного двоичнодесятичного кода и переводит блок обращения кода в режим передачи прямого кода.

Таким образом, после первого нуля в инвертированном двоично-десятичном коде остальные его разряды передаются блокам обратного кода 5 в пря мсм коде, что приводит к уменьшению младшей тетрады на одну единицу.

Действительно, если, например, с выхода регистра сдвига 8 считывается двоично-десятичный код 0000.1000 (восемь), то в его инвертированном коде первый нуль сформируется в четвертом разряде младшей тетрады, после ко.торого двоичный -код второй тетрады переписывается в прямом коде. В результате сформируется двоичнодесятичный код 000.0111 (семь).

Следовательно, в младшей тетраде двоично-десятичного кода выполняется двоичное вычитание посредством управления блоком обращения кода 4 со стороны триггера 7.

Блок коррекции 3 в режиме двоичного вычитания от 9 до О выполняет Функции регистра сдвига на два разряда, дополняя регистр сдвига до 4 двоичных разрядов.

Десятичный переход счета из тетра ды в тетраду в режиме вычитания осуществляется следующим образом. Если, например, с выхода регистра сдвига 8 считывается двоично-дес,личный код 0001.0000 (десять) и на вычитающем входе 10 действует входной импульс

который установит триггер 7 в единичное состояние, то триггер 7 сохранит это состояние во время инвертирования блоком обращения кода 4 всех разрядов млгщ-; шей тетрады, в которой образуется запрещенный код 1111.

Блок коррекции 3 в режиме вычитания срабатывает по запрещенному коду 1111 и затсрываёт на один такт цепи сдвига в блоке коррекции 3, стирая единицы во втором и третьем разрядах младшей тетрады. Этим осуществляется преобразование запрещенного кода 1111 младшей тетрады в двоичный код 1001 (девять).

Так как первый нуль в инвертированном двоично-десятичном коде 1110.1111 формируется блоком обращения кода 4 только в первом разряде второй тетрады, триггер 7 вернется в нулевое логическое состояние после первого разряда второй тетрадыи переключит блок обращения кода 4 в режим передачи прямого кода.

В результате вместо исходного кода 0001.0000 (десять) в регистр сдвига 8 с выхода блока коррекции 3 записывается новый двоично-десятичный код 0000.100Q1 (девять).

Дальнейшее двоичное вычитание в тетрадах и десятичный переход счета из младшей тетрады в старшую в режим вычитания осуществляется аналогичным образом-.

Если в режиме вычитания во всех тетрадах двоично-десятичного кода на рыходе блока обращение кода 4 сфор)1ируется нулевой коди на вычитающий вход 10 поступает входной импульс, то блок знака 2 срабатывает по сигналам, поступающим с выхода блока обращения кода 4 на его четвертый вход, что приведет к изменению знака результата на отрицательный и переведет счетчикив режим суммирования.

Если знак результата отрицательный и на суммирующий вход 9 поступает входной импульс, то блок знака 2 переводит счетчик в режим вычитания

Если знак результата отрицательный во всех тетрадах двоично-десятичного кода на выходе блока обращения кода 5 сформируется нулевой код, и на суммирующий вход 9 поступает входной импульс, а блок знака 2 изменяет знак результата на положительный и переводит счетчик в режим суммирования.

Таким образом осуществляется десятичный счет как с положительным, так и отрицательными числами.

Абсолютная величина результата счета фиксируется в двоично-десятичном коде 8-4-2-1 в последовательном регистре, который образован соединением блока коррекции 3 и регистра сдвига 8.Знак результата счета фикси руется блоком знака 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный вычитающий счетчик | 1979 |

|

SU809584A1 |

| РЕВЕРСИВНЫЙ ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1973 |

|

SU374643A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Многоканальный десятичный счетчик | 1979 |

|

SU824443A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Счетчик для вычитания | 1984 |

|

SU1228276A1 |

Авторы

Даты

1981-04-15—Публикация

1979-03-28—Подача