Изобретение относится к области вычислительной техники и может применяться в арифметинеских устройствах, обрабатывающих как двоичную, так и десятичную информацию.

Известно десятичное вычислительное устройство последовательного действия, состоящее из преобразователей фазоимпульсного представления чисел в пространственно-импульсное, преобразователей пространственно-импульсного представления чисел в фазоимпульсное представление чисел суммирующего и множительного блоков, логической схемы и блока микропрограммного управления, причем выходы входного преобразователя фазоимпульсного представления чисел в пространственноимпульсное подключены к входам преобразователей пространственно-импульсного представления чисел в фазоимпульсное представление чисел суммирующего и множительного блоков и через схемы И к входу декодирующей схемы блока микропрограммного управления 1.

Недостатком такого устройства является то, что при значительной сложности устройства оно выполняет лишь операции сложения и умножения десяти-чных чисел.

Наиболее близким к предлагаемому по технической сущности является устройство

для деления л-разрядных десятичных чисел, содержащее (2n-f 1)-разрядные десятичный сумматор и регистр делителя, информационные выходы которого подключены к информационным входам сумматора, регистр частного и блок управления, содержащий генератор импульсов, выход которого подключен к счетному входу двухразрядного двоичного счетчика, элементы

10 И, элементы НЕ, элементы задержки и триггер, причем выход генератора импульсов подключен к первым входам первого, второго, третьего, четвертого и пятого элементов И, второй вход которого подклю15чен к первому выходу двухразрядного двоичного счетчика, второму входу первого элемента И, выход которого через щестой элемент И и первый элемент задержки подключен к первому входу триггера, второй

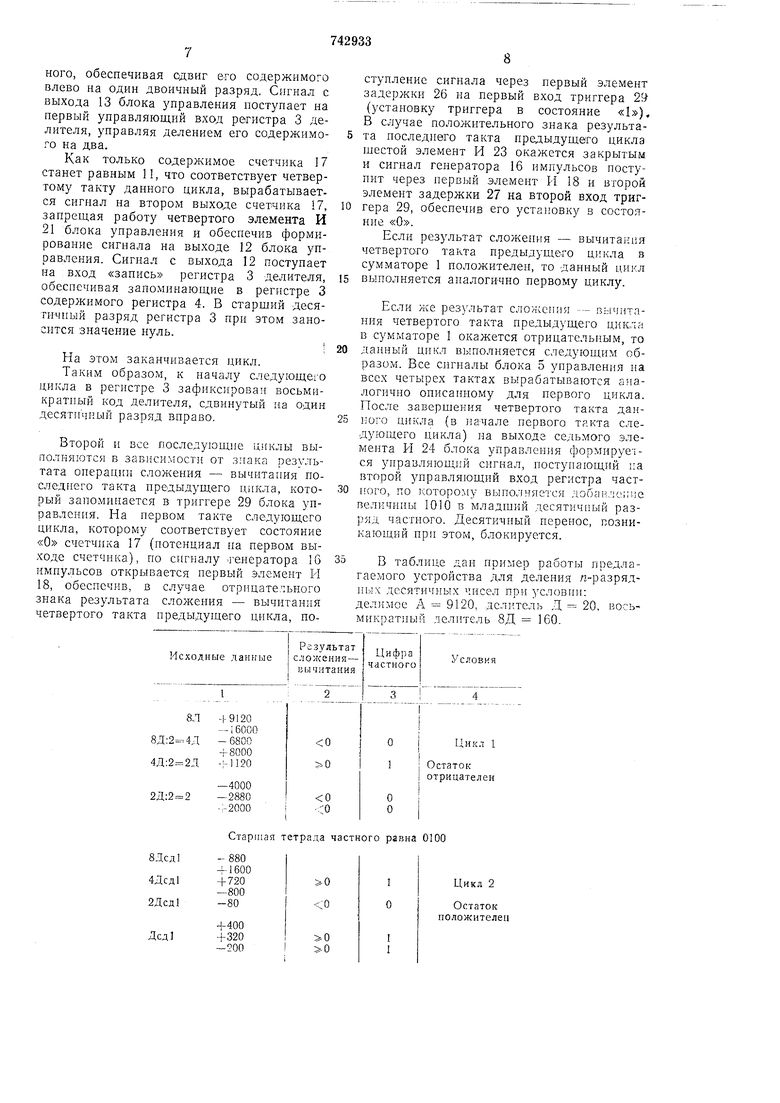

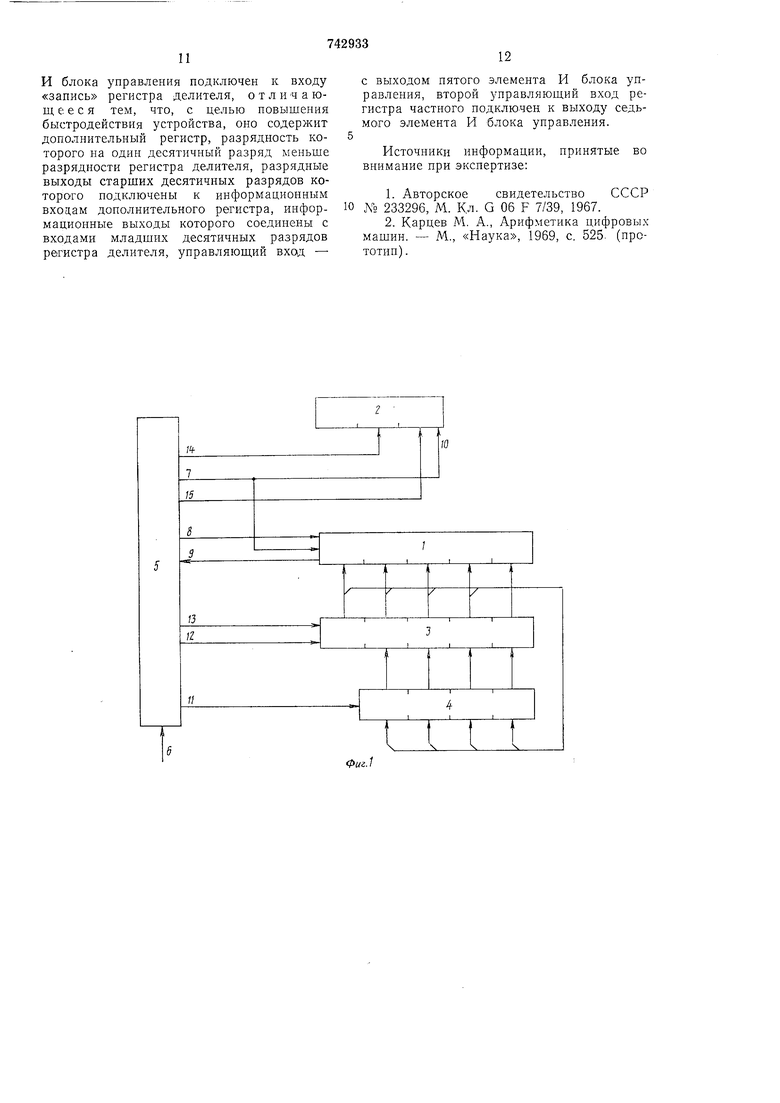

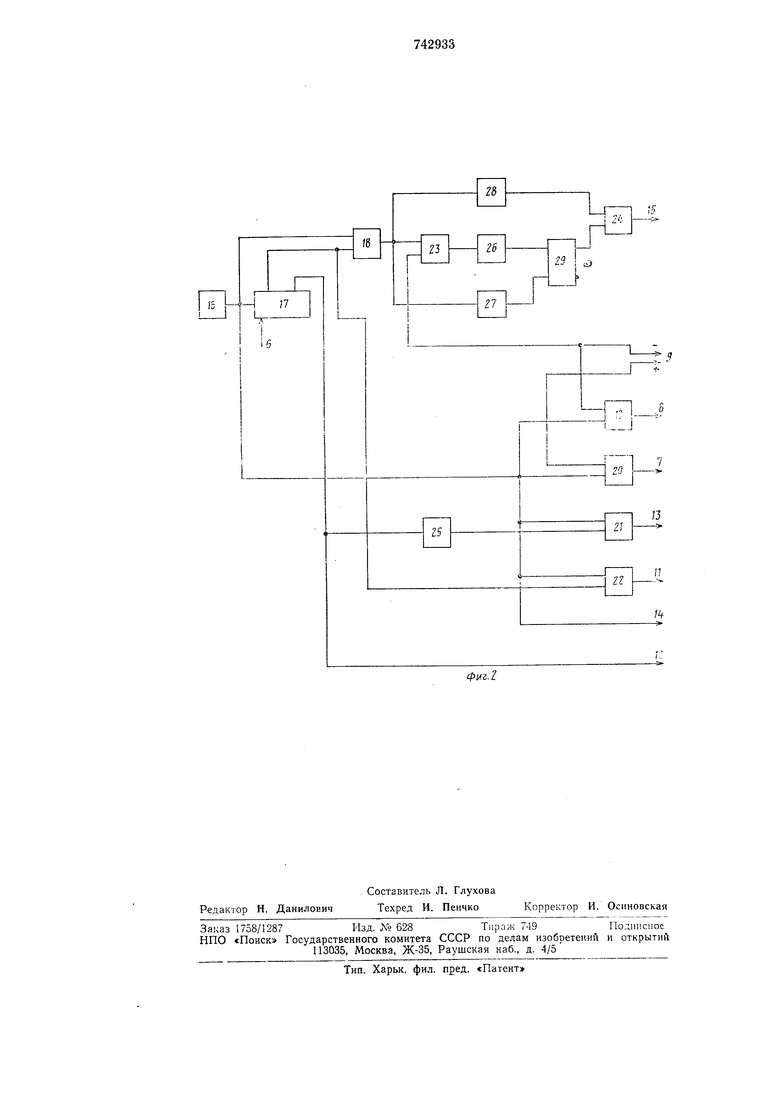

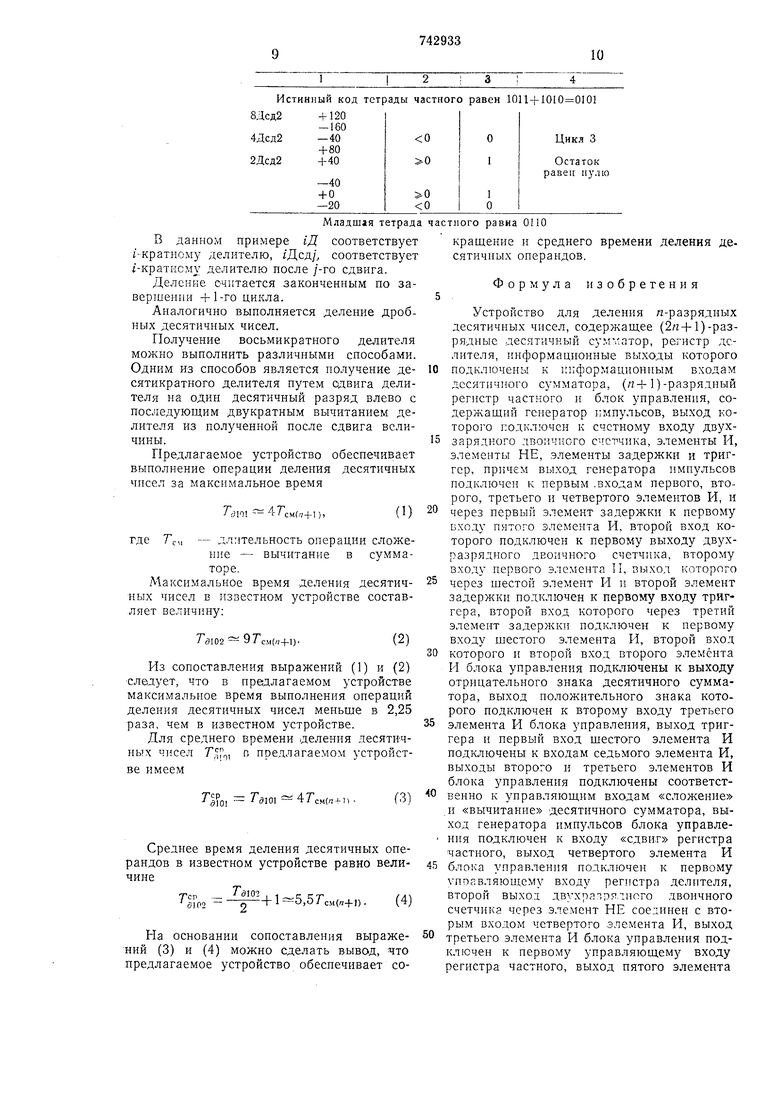

20 вход которого через второй элемент задержки подключен к первому входу щестого элемента И, второй вход которого и второй вход второго элемента И блока управления подключены к выходу отрицатель25ного знака десятичного сумматора, выход положительного знака которого подключен к второму входу третьего элемента И блока управления, выход триггера и первый вход щестого элемента И через третий эле30мент задержки подключены к входам седьмого элемента И, выходы второго и третьего элементов И блока управления подключены соответственно к управляющим входам «сложение и «вычитание десятичного сумматора, выход генератора импульсов блока управления подключен к входу «сдвиг регистра частного, выход четвертого элемента И блока управления подключен к первому управляющему входу регистра делителя, второй выход двухразрядного двоичного счетчика соединен с входом «запись регистра делителя и через элемент НЕ с вторым входом четвертого элемепта И, выход третьего элемента И блока управления подключен к первому управляющему входу регистра частного 2. Известное устройство выполняет онерацпю деления десятичных чисел за счет отработки отдельных десятичных разрядов частного, причем при отработке каждого разряда в младщую тетраду регистра частного добавляется столько единиц, сколько можно выполнить сложений - вычитаний делителя от садерл имого сумматора без изменения его знака, и далее выполняется сдвиг содержимого регистра частного и регистра делителя на четыре разряда. Недостатком данного устройства является то, что в нем затрачивается больщое время на выполнение операции деления десятичных чисел. Целью изобретения является повышение быстродействия устройства. Это достигается тем, что в устройство для деления л-разря.дных десятичных чисел введен дополнительный регистр, разрядность которого на один десятичный разряд меньше разрядности регистра делителя, разрядные вьгходы старших десятичных разрядов которого подключены к информационным входам дополнительного регистра, информационные выходы которого соединены с входами младших десятичных разрядов регистра делителя, управляющий вход - с выходом пятого элемента И блока управления, второй управляющий вход регистра частного подключен к выходу седьмого элемента PI блока управления. На фиг. 1 приве(дена структурная схема устройства для деления разрядных десятичных чисел; на фиг. 2 - схема блока упр.авления. Устройство состоит из следующих элементов:-десятичный сумматор 1, содержащий () десятичный разряд, имеющий информационные разрядные входы, управляющие входы «сложение и «вычитание и парафазный выход знака; -регистр 2 частного, содержащий {«+1) десятичный разряд и имеющий вход «сдвиг, первый управляющий вход, поступление сигнала на который обеспечивает установку единицы в младшем двоичном разряде регистра частного, и второй унравляющий вход, сигнал па котором обеспечивает преобразование обратиого десятичного кода, находящегося в младше.м десятичном р,азряде регистра частного, в прямой код; -регистр 3 делителя, содержащий (2n-f 1) десятичный разряд, предназначенный для хранения десятичных цифр восьмикратиого делителя и получения путем деления на два других его кратных, имеющий цепи деления на два, информационные разрядные выходы, соединенные с информационными входами соответствующих десятичных разрядов сумматора 1, информационные входы для младших 2л десятичных разрядов, первый управляющий вход и управляющий вход «запись ; -дополнительный регистр 4, содержащий 2п десятичных разрядов и предназначенный для хранения восьмикратного делителя, имеющий информационные разрядные входы и выходы и управляющие входы, причем информационные входы дополнительного регистра соединены с соответствующими информационными выходами (-2«)-х десятичных разрядов регистра 3 делителя, входы младщих десятичных разрядов которого подключены к соответствующим информационным выходам регистра 4; -блок управления 5, имеющий вход 6 пуска, выходы 7 и 8, соедлисииые с входами «вычитание и «сложение сумматора 1 соответственно, парафазный вход 9 знака, подключенный к выходу знака десятичного сумматора, выход 7, подсоединенный к первому управляющему входу 10 ре |гистра 2 частного, выход II и 12, соединениые соответственно с управляющим входом регистра 4 и управляющим входом «запись регистра 3, выход 13 соединенный с первым управляющим входом регистра 3, выход 14 и 15, подсоединенные соответственно к входу «сдвиг и второму упр.авляющему входу регистра 2 частного. Схема блока управления 5, обеспечивающая выполнение отдельных циклов деления, состоит из следующих элементов: - генератор 16 импульсов, выход которого соединен с выходом 14 блока управления;-двухразрядный двоичный счетчик 17, имеющий счетный вход, подключенный к выходу генер.атора 16 импульсов, и два выхода; -первый - седьмой элементы И 1824, причем первые входы первого, второго, третьего, четвертого и пятого элементов И подключены к выходу генератора импульсов 16, вторые входы первого и пятого элементов И соединены с первым выходом счетчика 17, вторые входы второго и шестого и второй вход третьего элементов И подсоединены соответственно к парафазному входу 9 отрицательного и положительного знака блока управления, выход первого элемента И подключен к первому входу шестого элемента И, выходы второго, третьего, четвертого, пятого и седьмого элементов И соединены соответственно с выходами 8, 7, 13, 11 и 15 блока управления;-элемент НЕ 25, вход которого соединен с вторым выходом счетчика 17 и выходом 12 блока управления, а выход - с вторым входом четвертого элемента И; -первый - третий элементы задержки 26-28, причем вход первого элемента задержки соединен с выходом шестого элемента И, входы второго и третьего элементов задержки подключены к выходу первого элемента И, выход третьего элемента задержки соединен с первым входом седьмого элемента И; - триггер 29, первый и второй входы которого подключены соответственно к выходам первого и второго элементов задержки, а выход - к второму входу седьмого элемента И. Устройство (см. фиг. 1) обрабатывает десятичную информацию, пре{дставленную в 8-4-2-1. Деление в устройстве выполняется за (п + 1) циклов. Каждый цикл состоит из четырех тактов. На каждом такте определяется соответствуюший двоичный разряд двоично-десятичного изображения текущей десятичной цифры частотного. Деление выполняется методом без восстановления остатков. Устройство работает следующим образом. В исходном состоянии в сумматоре 1 (десятичных разрядах 2-(«+) находится делимое, в старишх (/г+1) десятичных разрядах регистра делителя 3 помещен восьмикратный код делителя, первый десятичный разряд сумматора, разряды регистров 2 и 4 н младшие п десятичных разрядов регистра 3 установлены в нуль. Счетчик 17 и триггер 29 блока управления также установлены в нуль. На первом цикле опре1леляется старший десятичный разряд частного. Первому такту соответствует нулевое состояние счетчика 17 (потенциал на первом выходе счетчика). Поэтому по си|гналу генератора 16 импульсов формируются сигналы на выходах 7 и 11 блока управления. Сигнал с выхода 7 поступает на вход «вычитание десятн чного сумматора .1, обеспечивая вычитание из делимого кода восьмикратного делителя. Знак результата вычитания поступает на парафазный вход 9 знака блока управления. Сигнал с выхода 11 поступает на управляющий вход дополнительного регистра, управляя запоминанием в регистре 4 содержимого 2л старших десятичных разрядов регистра 3 (кода восьмикратного делителя). Кроме того, спгнал с выхода 7 блока уг.рпвлепи;; поступает на первый управляюlUiii; вход регистра 2 частотного, выполняя занесение единицы в младший разряд регистра 2. Данная единица гасится во время первого такта первого цикла и сохраняется во всех остальных случаях. Одновременно по сигналу генератора 16 имиульсов формируется сигнал на выходе 14 блока управления. Кроме того, срабатывает элемент НЕ 25 и четвертый элемент И 21, обеспечнвая формирование сигнала на выходе 13 блока управления. Сигнал с выхода 13 поступает на первый управляющий вход регистра 3 делителя, обеспечивая деление его содержимого иа два Сигнал с выхода 14 блока управления поступает на управляющий вход «сдвиг регистра 2 частного, выполняя сдвиг его содержимого влево на один двоичный разряд. Кроме того, генератора 16 импульсов, поступая на счетный вход двухразрядного двопчного счетчика 17 блока управления, обеспечивает установку в нем кода 01. На этом вынолнение первого такта заканчнвается. Второй, третий, и четвертый такты первого цикла выполняются следующим образом:- если знак результата вычитания в сумматоре 1 положителен, то сигнал с выхода положительного знака сумматора поступает на вход 9 блока управления, обеспечивая срабатывание по очередному сигналу генератора .16 нмпульсов, элемента И 20, сигнал с выхода которого поступает на первый управляющий вход регистра 2 частного и на управляющий вход «вычитание десятичного сумматора 1, обеспечивая установку единицы в младший разряд регистра 2 частного и вычитание из содержимого сумматора 1 содерл имого регистра 3; - если знак результата вычитания в сумматоре 1 отрицателен, то сигнал с выхода отрицательного знака сумматора поступает на вход 9 блока управлення и открывает, по очередному сигналу генератора-16 импульсов, второй элемент И 19 блока управления, сигнал с выхода которого поступает на вход «сложение сумматора I, обеспечивая добавление к содержимому сумматора 1 содержимого регистра 3. Знак результата сложения - вычитаиия поступает на парафазный вход 9 блока управления. Одновременно с выполнением операции сложения - вычитания в сумматоре 1 по очередному сигналу генератора 16 импульсов добавляется единица к содержимому двухразрядного двоичного счетчика 17 и формируются сигналы на выходах 13 и 14 блока управления. Сигнал с выхода 14 поступает на вход «сдвиг регистра 2 частного, обеспечивая сдвиг его содержимого влево на один двоичный разряд. Сигнал с выхода 13 блока зправления поступает иа иервый управляющий вход регистра 3 делителя, управляя делением его содержимого на два. Как только содержимое счетчика 17 станет равным 11, что соответствует четвертому такту данного цикла, вырабатывается сигнал на втором выходе счетчика 17, запрещая работу четвертого элемента И 21 блока управления и обеспечив формирование сигнала на выходе 12 блока управления. Сигнал с выхода 12 поступает на вход «запись регистра 3 делителя, обеспечивая заномпнающие в регистре 3 содержимого регистра 4. В старший десятичный разряд регистра 3 при этом заносится значение нуль. На этом заканчивается цикл. Таким образом, к началу следующего цикла в регистре 3 зафиксирован восьмикратный код делителя, сдвинутый на один десятичный разряд вправо. Второй и все последующие циклы выполняются в зависимости от знака результата операции сложения - вычитания поСиТеднего такта предыдущего цикла, который запоминается в триггере 29 блока управления. На нервом такте следующего цнкла, которому соответствует состояние «О счетчика 17 (потенциал па нервом выходе счетчика), по сигналу теиератора 1G имнульсов открывается первый элемент И 18, обеспечив, в случае отрицательного знака результата сложения - вычитания четвертого такта предыдущего цикла, поступление сигнала через нервый элемент задержки 26 на первый вход триггера 2 (установку триггера в состояние «I), В случае положнтельного знака результата последнего такта предыдущего цикла шестой элемент И 23 окажется закрытым и сигнал генератора 16 импульсов поступит через нервый элемент И 18 и второй элемент задержки 27 на второй вход триггера 29, обеспечив его установку в состояние «О. Если результат сложения - вычитания четвертого такта предыдущего цикла в сумматоре 1 положителец, то данный цикл выполняется аиалогичио первому циклу. Если же результат сложения -- вычитания четвертого такта предыдущего цикла в сумматоре 1 окажется отрицательным, то данный цикл выполняется следующим образом. Все сигналы блока 5 управления на всех четырех тактах вырабатываются аналогичио описанному для нервого цикла. После завершения четвертого такта данного цикла (в начале первого такта следующего цикла) на выходе седьмого элемента И 24 блока управления формируе-гся управляющий сигнал, поступающий па второй управляющий вход регистра част1ГОГО, по которому выполняется лобавлсч;ие пеличипы 1010 в младший десятичный разряд частпого. Десятичный перенос, возникающий при этом, блокируется. В таблице дан пример работы предлагаемого устройства для деления п-разрядных десятичных чисел при условии: делимое А 9120, делитель Д 20, восьмикоатпый делитель 8Д 160.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для деления п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU807282A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

Старшая тетрада частного равна 0100

Цикл 2

Остаток положителен

Истинный код тетрады частного равен 1011-|-1010 0101 Младшая тетрад В данном примере 1Д соответствует г-кратиому делителю, Щсд/, соответствует i-кратмсму делителю после /-го сдвига. Деление считается законченным по завершении + 1-ГО цикла. Аналогично выполняется деление дробных десятичных чисел. Получение восьмикратного делителя можно выполнить различными способами. Одним из способов является получение десятикратного делителя путем сдвига делителя на один десятичный разряд влево с последующим двукратным вычитанием делителя из полученной после сдвига величины. Предлагаемое устройство обеспечивает выполнение операции делепия десятичных чисел за максимальное время т - лт I 310 4 см(/; + 1 ), Гсм - длительность операции сложение - вычитание в сумматоре. Максимальное время деления десятичных чисел Е известном устройстве составляет величину: 9Гсм(/, Из сопоставления выражений (1) и (2) , что в предлагаемом устройстве максимальное время выполнения операций деления десятичных чисел меньше в 2,25 раза, чем в известном устройстве. Для среднего времени деления десятичных чисел 7, п предлагаемом устройстве имеем Среднее время деления десятичных операндов в известном устройстве равно величинеТер - ,5Гс.ч{«-ь1). (4) 6102 На основании сопоставления выражений (3) и (4) можно сделать вывод, что предлагаемое устройство обеспечивает со3тного равна ОНО кращение и среднего времени деления десятичных операндов. Формула изобретения Устройство для деления п-разрядных десятичных чисел, содержащее (2п+1)-разрядные десятичный сумматор, регистр делителя, информационные выходы которого подключены к информационным входам десятичного сумматора, (n-f 1)-разрядный регистр частного и блок управления, содержащий генератор импульсов, выход которого подключен к счетному входу двухзарядного двоичного счетчика, элементы И, элементы НЕ, элементы задержки и триггер, причем выход генератора импульсов подключен к первым .входам первого, второго, третьего и четвертого элементов И, и через первый элемент задержки к первому входу пятого элемента И, второй вход которого подключен к первому выходу двухразрядного двоичного счетчика, второму входу первого элемента П, выход которого через шестой элемепт И и второй элемент задержки подключен к первому входу триггера, второй вход которого через третий элемепт задержки подключен к первому входу шестого элемента П, второй вход которого и второй вход второго элемента П блока управления подключены к выходу отрицательного знака десятичного сумматора, выход иоложительного знака которого подключен к второму входу третьего элемента И блока управления, выход триггера и первый вход шестого элемента И подк.пючены к входам седьмого элемента И, выходы второго и третьего элементов И блока управления подключены соответственно к управляющим входам «слол ение и «вычитание десятичного сумматора, выход генератора импульсов блока управления подключен к входу «сдвиг регистра частного, выход четвертого элемента И блока управления подключен к первому управляющему входу регистра делителя, второй выход двухралря.шого двоичного счетчика через элемент НЕ соединен с вторым входом четвертого элемента И, выход третьего элемента П блока управления подключен к первому управляющему входу регистра частного, выход пятого элемента

И И блока управления подключен к входу «запись регистра делителя, о т л и -ч а ющееся тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный регистр, разрядность которого на один десятичный разряд меньше разрядности регистра делителя, разрядные выходы старших десятичных разрядов которого подключены к информационным входам дополнительного регистра, информационные выходы которого соединены с входами младших десятичных разрядов регистра делителя, управляющий вход -

12

с выходом пятого элемента И блока управления, второй управляюший вход регистра частного подключен к выходу седьмого элемента И блока управления. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР Хо 233296, М. Кл. G 06 F 7/39, 1967. 2.Карцев М. А., Арифметика цифровых машин. - М., «Наука, 1969, с. 525- (прототип) .

Авторы

Даты

1980-06-25—Публикация

1976-05-03—Подача