1

Изобретение может быть использовано в устройствах аналоговой вычислительной техники со смешанным представлением ин;формации, в частности в устройствах время-импульсного типа.

Известные имлульсные делители напряжения на МОП-траизисторах, содержащие два продольных управляемых плеча, соединенных с источниками регулирующего «апряжения, и нагрузочный фильтр на выходе, обладают достаточно большой зависимостью входного сопротивления делителя от изменения входного напряжения, а также большими динамическими и статическими помехами от цепей управления.

Предлагаемый делитель отличается тем, что каждое продольное плечо делителя выполнено на двух МОП-транзисторах с различными каналами проводимости, причем участки стокисток этих транзисторов соединены параллельно.

Это позволяет уменьшить зависимость входного сопротивления делителя от изменения входного налряжения и уменьшить динамические и статические помехи от цепей управления.

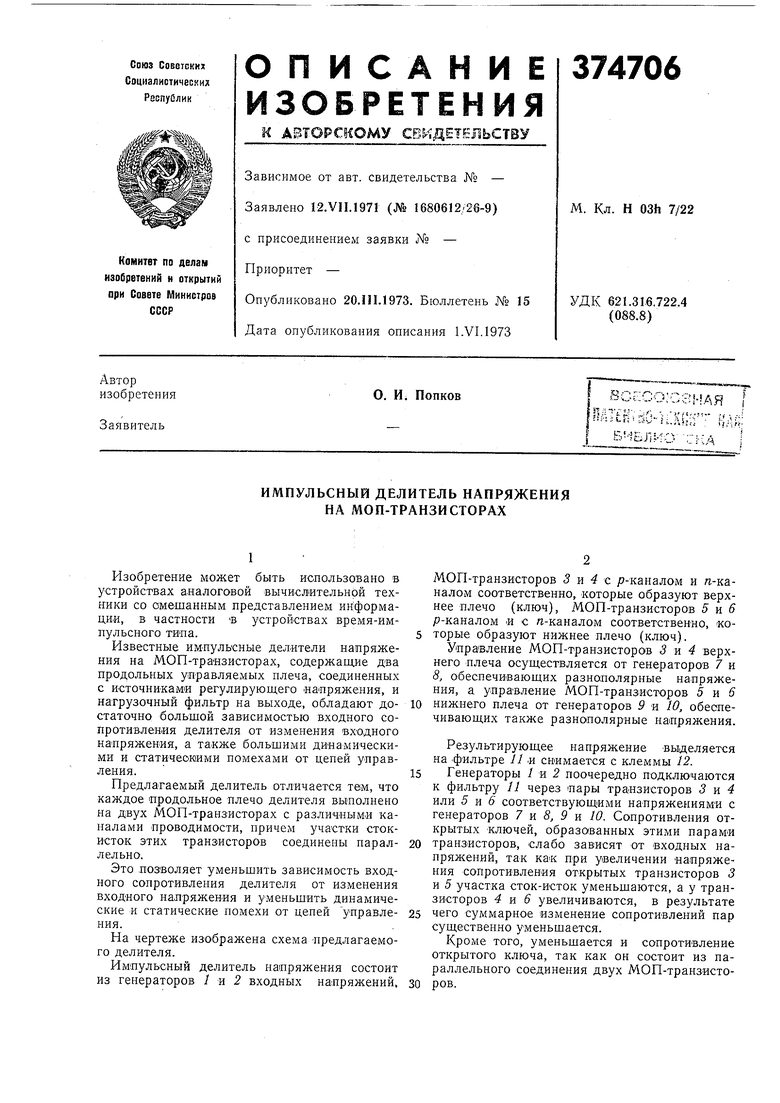

На чертеже изображена схема предлагаемого делителя.

Импульсный делитель напряжения состоит из генераторов 1 н 2 входных напряжений,

МОП-транзисторов и 4 с р-каналом и п-каналом соответственно, которые образуют верхнее плечо (ключ), МОП-транзисторов 5 и 6 р-каналом и с п-каналом соответствен-но, которые образуют нижнее плечо (ключ).

Управление МОП-транзисторов верхнего плеча осуществляется от генераторов 7 и 8, обеспечивающих разнополярные напряжения, а управление МОП-транзисторов 5 и 5 нижнего плеча от генераторов 9 и 10, обеспечивающих также разнополярные напряжения.

Результирующее напряжение выделяется на -фильтре 11 и снимается с клеммы 12.

Генераторы 1 к 2 поочередно подключаются к фильтру 11 через пары транзисторов 3 vi 4 или 5 и 6 соответствующими напряжениями с генераторов 7 н 8, 9 и 10. Сопротивления открытых Ключей, образованных этими парами транзисторов, слабо зависят от входных напрял ений, так при увеличении напряжения сопротивления открытых транзисторов 3 и 5 участка сток-исток уменьшаются, а у транзисторов 4 т 6 увеличиваются, в результате чего суммарное изменение сопротивлений пар существенно уменьшается.

Кроме того, уменьшается и сопротивление открытого ключа, так как он состоит из параллельного соединения двух МОП-транзисторов.

При уменьшении входного напряжения сопротивления МОП-транзисторов 3 и 5 увеличиваются, а сопротивления МОП-транзисторов 4 И 6 уменьшаются, суммарное же сопротивление пар изменяется также незначительно. Динамическая ошибка от цепей управления за счет пролезания фронтов управляюш.их импульсов также уменьшается, так как МОПтранзисторы 3 и 5j 4 и 6 открываются разнополярными перепадами напряжений.

Известно, что помехи переключения от включения я выключения имеют несколько различные длительности и амплитуды, что снижает эффективность компенсации помех методом совмеш,ения процесса выключения одного ключа с включением другого. В предлагаемом варианте МОП-транзисторы 3 и 4 (5 и 6) .как при включении, так и при выключении дают разнополярные помехи, поэтому эффективность компенсации увеличивается.

Статическая ошибка за счет цепей управления уменьшается, так как токи от МОП-транзисторов (5 VL 6 |Имеют противоположные направления и взаимно компенсируются.

Предмет изобретения

Импульсный делитель напряжения на МОП-транзисторах, содержащий два продольных управляемых плеча, соединенных с Источниками регулирующего напряжения, и нагрузочный фильтр на выходе, отличающийся тем, что, с целью уменьшения зависимости входного сопротивления делителя от изменения входного Напряжения и уменьшения динамических и статических помех от цепей управления, каждое продольное плечо делителя выполнено на двух МОП-транзисторах с различными каналами проводимости, причем участки Стокисток этих транзисторов соединены параллельно.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННОЕ РЕЛЕ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ И С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ ПО ТОКУ И ПЕРЕГРЕВА ЭЛЕКТРОННОГО КЛЮЧА | 2008 |

|

RU2380828C1 |

| Пьезополупроводниковый стабилизатор постоянного напряжения | 1980 |

|

SU926636A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМ ТИРИСТОРОМ | 2023 |

|

RU2821266C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Фиксатор уровня | 1984 |

|

SU1182646A2 |

| Способ управления транзисторами многоячейкового преобразователя постоянного напряжения | 1989 |

|

SU1737667A1 |

| СПОСОБ УПРАВЛЕНИЯ СИНУСОИДАЛЬНЫМ ДИММЕРОМ | 2005 |

|

RU2370922C2 |

| ИСТОЧНИК СТАБИЛЬНОГО ТОКА ИЛИ НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 2022 |

|

RU2795478C1 |

| Интегратор | 1978 |

|

SU748439A1 |

| ТЕХНОЛОГИЯ ОПРЕДЕЛЕНИЯ ВЕЩЕЙ | 2010 |

|

RU2453003C2 |

12

Даты

1973-01-01—Публикация