ОБЛАСТЬ ТЕХНИКИ

Данное изобретение касается способа управления синусоидальным диммером для обеспечения его надежной работы и эффективного переноса мощности через индуктивный выходной фильтр диммера.

УРОВЕНЬ ТЕХНИКИ

Лампа может получать питание через диммер (регулятор мощности), в результате чего она будет обеспечивать переменные выбранные уровни интенсивности света. Например, источники света, используемые в театрах, для подсветки архитектурных объектов и для других целей часто получают электропитание через диммеры. Хорошо известны используемые для этой цели диммеры с фазовой отсечкой, которые обычно включают твердотельные ключи, например тиристоры, для соединения источника питания с ламповой нагрузкой. Переменное напряжение источника имеет синусоидальную форму. Схема фазового управления делает твердотельный ключ проводящим в некоторой точке в течение полупериода синусоиды, при этом точка выбирается так, чтобы подать на лампу рабочий импульс питания, требуемый для обеспечения нужной интенсивности света. Операции переключения в диммере с фазовой отсечкой выполняются тиристором на низкой частоте, например, один или два раза на каждый период питающего напряжения, или пятьдесят или шестьдесят раз в секунду.

При использовании диммера с фазовой отсечкой скачкообразное переключение на низкой частоте в течение полупериода питающего напряжения и получаемые в результате скачкообразные изменения амплитуды питающего тока источников света могут вызывать проблемы, связанные с электрическими помехами и механическим шумом нитей накаливания, что требует использования активной фильтрации. В некоторых применениях даже при использовании фильтрации шум, характерный для регулирования с фазовой отсечкой, может быть неприемлемым. Кроме того, диммеры с фазовой отсечкой имеют тот недостаток, что на них могут влиять гармонические искажения напряжения сети электропитания.

Чтобы избежать потенциальных проблем низкочастотных диммеров с фазовой отсечкой, используют технологию широтно-импульсной модуляции (ШИМ) с твердотельными ключами, работающими на более высоких частотах. При использовании этого типа регулируемых источников питания, известных как коммутируемые источники питания или источники питания с ШИМ, интенсивность света изменяется за счет изменения ширины импульса при модуляции рабочего цикла ШИМ. Выходной сигнал после фильтрации выходным нагрузочным фильтром может иметь форму, схожую с формой сигнала источника питания, но с уменьшенной амплитудой. Обычно сигнал входного источника питания и отрегулированный выходной сигнал имеют синусоидальную форму. По этой причине диммеры с широтно-импульсной модуляцией также известны под названием "синусоидальных диммеров".

Хорошо известны асинхронные синусоидальные диммеры. В этом типе диммеров широтно-импульсная модуляция используется для управления высокочастотным переключением коммутирующих устройств, включенных последовательно между источником питания и выходным фильтром с нагрузкой. Выходной фильтр содержит индуктивные компоненты, в которых запасается энергия, когда устройства последовательной коммутации проводят ток. Секция ограничения, подключенная параллельно выходному фильтру и нагрузке, предупреждает нежелательные выбросы напряжения и обеспечивает передачу энергии, запасенной в выходном фильтре, в нагрузку, когда устройства последовательной коммутации находятся в непроводящем состоянии.

Секция ограничения обычного асинхронного синусоидального диммера включает параллельные переключающие устройства со встречно-параллельными быстродействующими переключающими диодами. Диоды обеспечивают функции переключения для включения параллельных устройств ограничительной коммутации синхронно с формой синусоиды источника питания, так что один ключ ограничения остается проводящим при положительном полупериоде синусоиды источника питания, а второй ключ ограничения остается проводящим при отрицательном полупериоде синусоиды источника питания.

Такой асинхронный подход имеет свои недостатки. Одной из проблем является обеспечение точного управления секцией ограничительной коммутации вблизи точки перехода синусоиды источника питания через ноль. Другая проблема возникает, когда нагрузка реактивная или когда нагрузка мала по сравнению с индуктивностью выходного фильтра, и ток и напряжение источника мощности не совпадают по фазе. Диммеры в современных приложениях используются для управления различными типами реактивных нагрузок, например источниками питания для газоразрядных и флуоресцентных ламп. Асинхронные диммеры этого типа описывают патенты США 5424618, 5500576, 5714847 и 6346778.

Альтернативой стандартным асинхронным синусоидальным диммерам являются синхронные диммеры, в которых секция ограничения управляется синхронно сигналом ШИМ, а не формой сигнала источника питания. При таком подходе ключами ограничения управляет противоположный сигнал ШИМ, так что когда последовательные ключи проводят ток, соответствующие ключи ограничения находятся в непроводящем состоянии, а когда последовательные ключи не проводят ток, соответствующие ключи ограничения находятся в проводящем состоянии. Преимущество синхронных диммеров состоит в том, что они эффективнее работают как с резистивной, так и с емкостной нагрузкой.

Потенциальная проблема синхронных диммеров связана с последовательностью чередования последовательной и ограничительной коммутации. Например, если ключ ограничения остается проводящим прежде, чем последовательный ключ перейдет в непроводящее состояние, образуется цепь с низким сопротивлением, параллельная источнику мощности. Это может привести к чрезмерному росту тока и тепловыделения и повреждению компонентов цепи, в том числе ключей. Аналогичная ситуация возникнет, если последовательный ключ станет проводящим прежде, чем ключ ограничения перейдет в непроводящее состояние.

Потенциальную проблему одновременной проводимости последовательного ключа и ключа ограничения можно предупредить задержкой перехода каждого из ключей в проводящий режим на время, достаточное, чтобы гарантировать переход дополняющего ключа в непроводящее состояние. Однако при этом образуется период, в течение которого ни последовательный ключ, ни ключ ограничения не проводят ток. В течение этого периода отсутствие пути протекания тока через выходной фильтр может привести к скачкам напряжения и неблагоприятно воздействовать на срок службы схемы и форму выходного сигнала. Было бы желательно создать способ работы синхронного синусоидального диммера с точным управлением поочередным переключением последовательного ключа и ключа ограничения.

В патенте США 5045774 описывается пример известного синхронного диммера. В этом устройстве двунаправленный последовательный ключ питания и двунаправленный параллельный ключ, или ключ ограничения поочередно работают, управляемые сигналом микропроцессорного управления, прикладываемым через секцию развязки к элементам, управляющим ключом питания и параллельным ключом. Диммер, описанный в этом патенте, не содержит средств, специально предназначенных для предотвращения одновременной проводимости ключей или одновременного отсутствия их проводимости. Для этого типа схем предполагается, что временная последовательность поочередного переключения создается благодаря собственным или детерминированным временным характеристикам нарастания/спада/задержки компонентов цепи, а не путем точного управления.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Главной целью настоящего изобретения является создание улучшенного способа управления синхронным синусоидальным диммером. Другие цели состоят в том, чтобы создать улучшенный способ управления синусоидальным диммером, который позволит обеспечить эффективную подачу электроэнергии в выходной фильтр и нагрузку, как для активной, так и для реактивной нагрузки; создать улучшенный способ управления синусоидальным диммером, который позволит точно управлять последовательностью поочередного переключения устройств последовательной и ограничительной коммутации; создать улучшенный способ управления синусоидальным диммером, который максимально увеличит эффективность передачи энергии в нагрузку и сведет к минимуму нежелательные переходные напряжения; создать улучшенный способ управления синусоидальным диммером, который позволит избежать одновременной проводимости устройств последовательной и ограничительной коммутации; создать улучшенный способ управления синусоидальным диммером, который позволит избежать одновременной непроводимости устройств последовательной и ограничительной коммутации; создать улучшенный способ управления синусоидальным диммером, который устранит затруднения, имеющиеся в существующих способах.

В соответствии с изобретением предлагается способ работы синусоидального диммера, позволяющий получить выходной сигнал мощности от источника питания, имеющего различную форму сигнала, при этом выходной сигнал будет иметь ту же самую форму сигнала, что и источник питания, но с меньшей амплитудой. Способ включает подачу сигнала ШИМ, имеющего рабочий цикл, соответствующий требуемой величине выходного сигнала. Устройство последовательной коммутации между источником питания и интегрирующим фильтром и устройство ограничительной коммутации, шунтирующее интегрирующий фильтр, поочередно переключаются в проводящее состояние. Процедура переключения включает изменение проводимости устройства последовательной коммутации в соответствии с сигналом ШИМ и изменение проводимости устройства ограничительной коммутации в соответствии с противоположным сигналом ШИМ. Каждое поочередное состояние проводимости устройства последовательной коммутации и устройства ограничительной коммутации отделено паузой, во время которой как первая, так и вторая цепь не проводит тока.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Настоящее изобретение поясняется с помощью следующего подробного описания предпочтительного варианта реализации изобретения, проиллюстрированного чертежами, на которых:

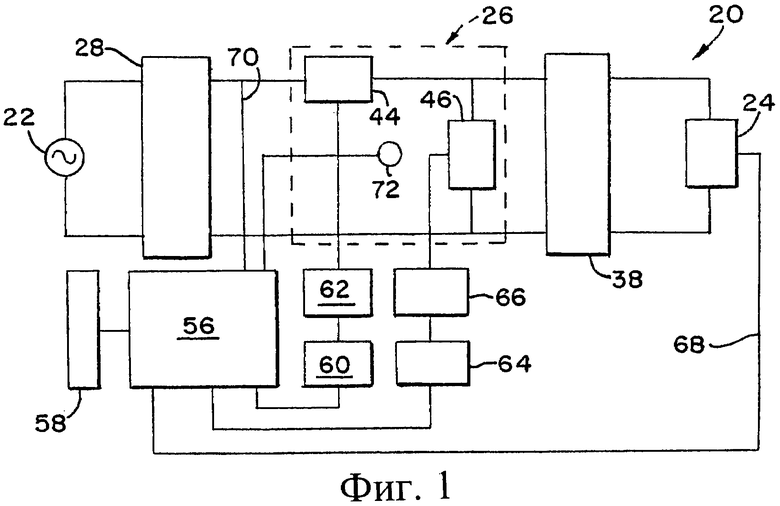

на фиг.1 приведена блок-схема синхронного синусоидального диммера, с помощью которого можно осуществить способ, являющийся предметом данного изобретения;

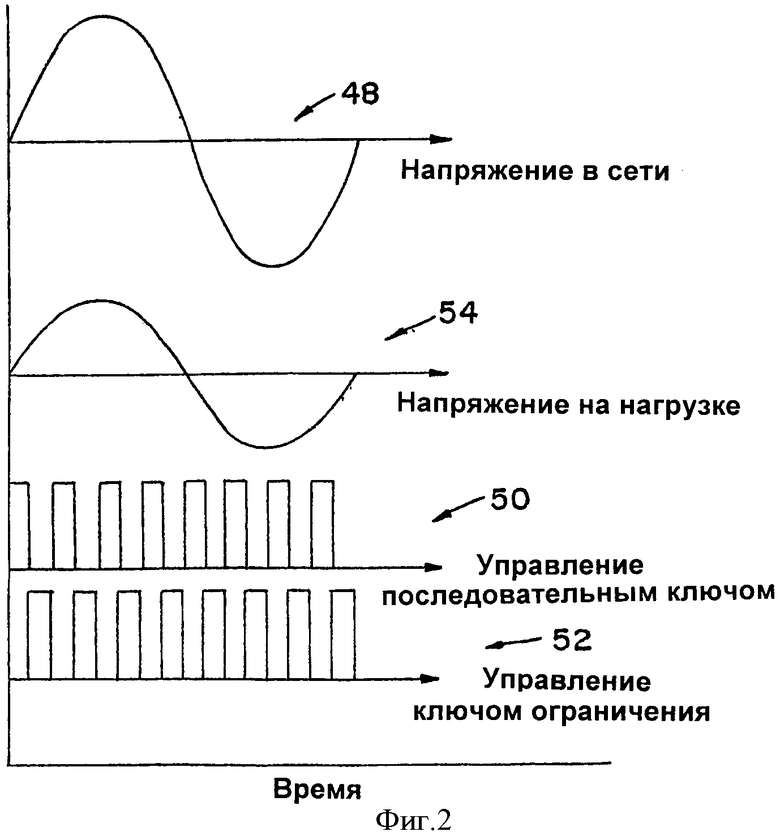

на фиг.2 приведен график, показывающий работу ШИМ в диммере;

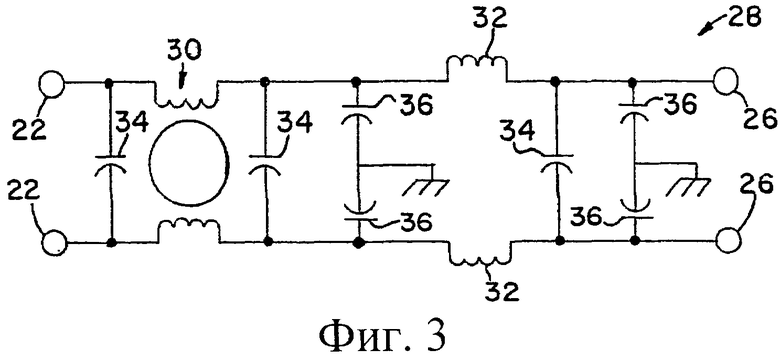

на фиг.3 приведена схема входного линейного фильтра диммера;

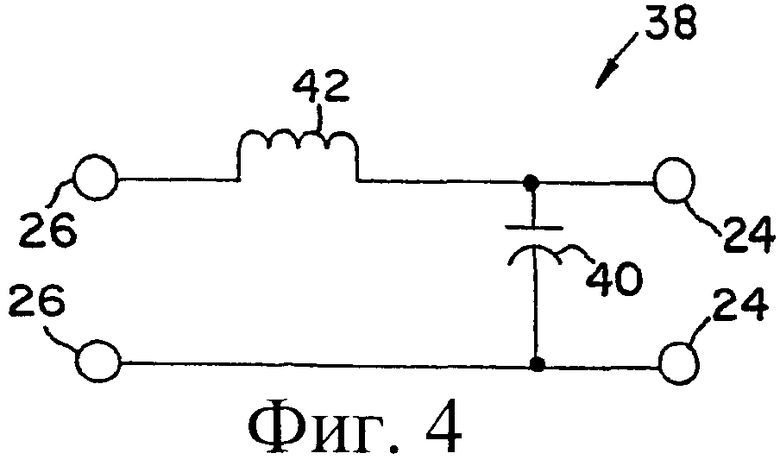

на фиг.4 приведена схема выходного нагрузочного фильтра диммера;

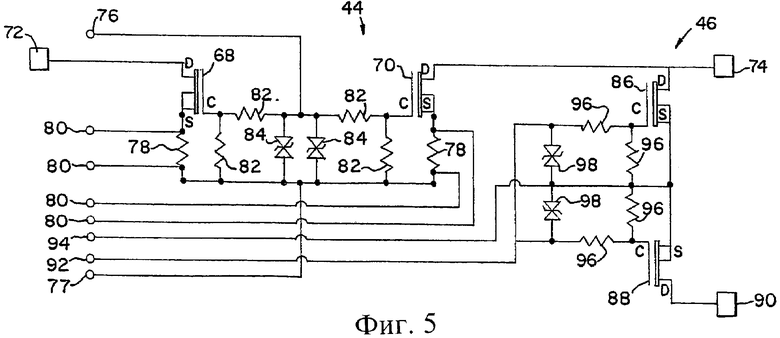

на фиг.5 приведена схема каскада коммутации мощности диммера;

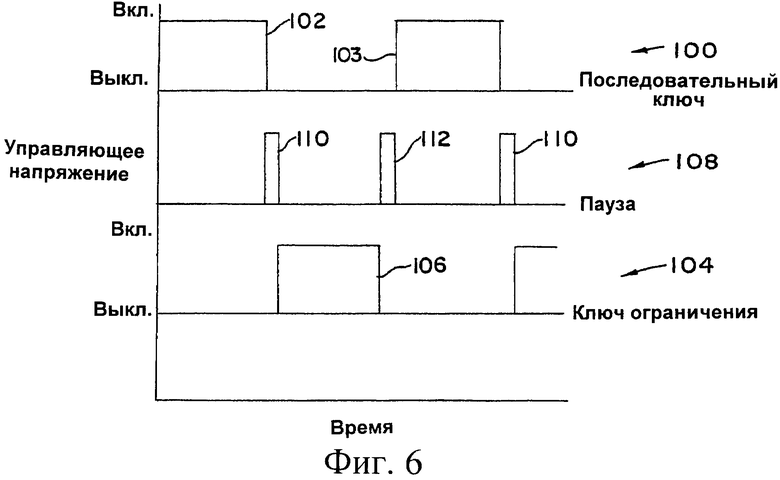

на фиг.6 приведен график, демонстрирующий программно управляемую вставку пауз между чередующимися сигналами управления последовательным ключом и ключом ограничения;

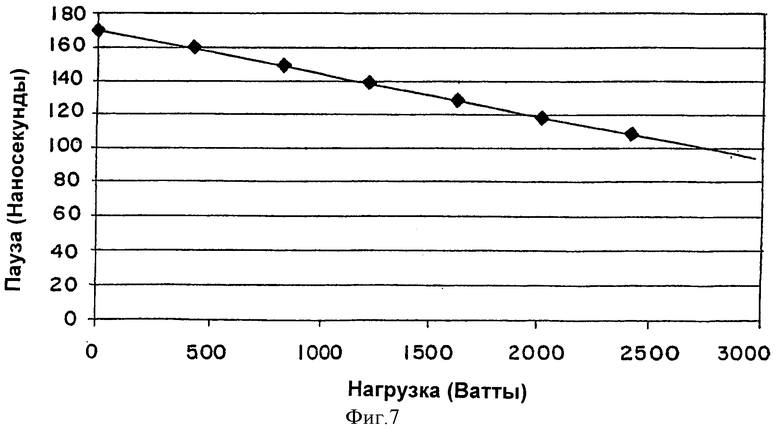

на фиг.7 приведен график, демонстрирующий связь между продолжительностью пауз и мощностью в нагрузке;

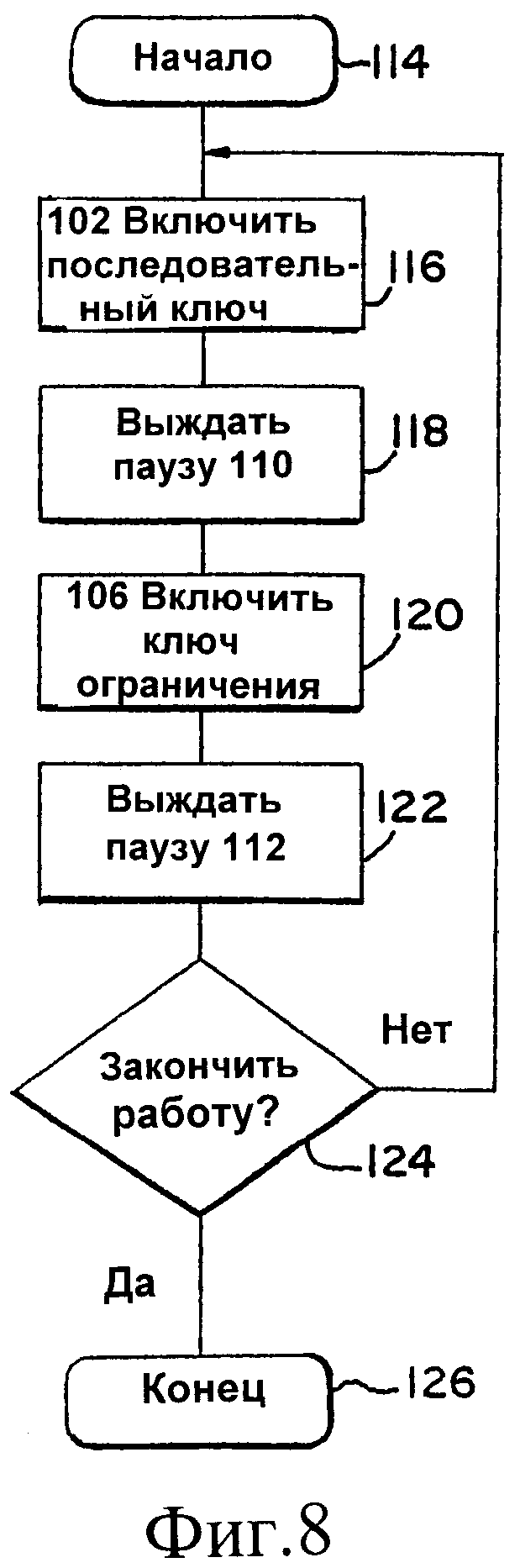

на фиг.8 приведена упрощенная блок-схема алгоритма процедуры, выполняемой программируемым контроллером диммера при управлении последовательным ключом и ключом ограничения в соответствии с данным изобретением;

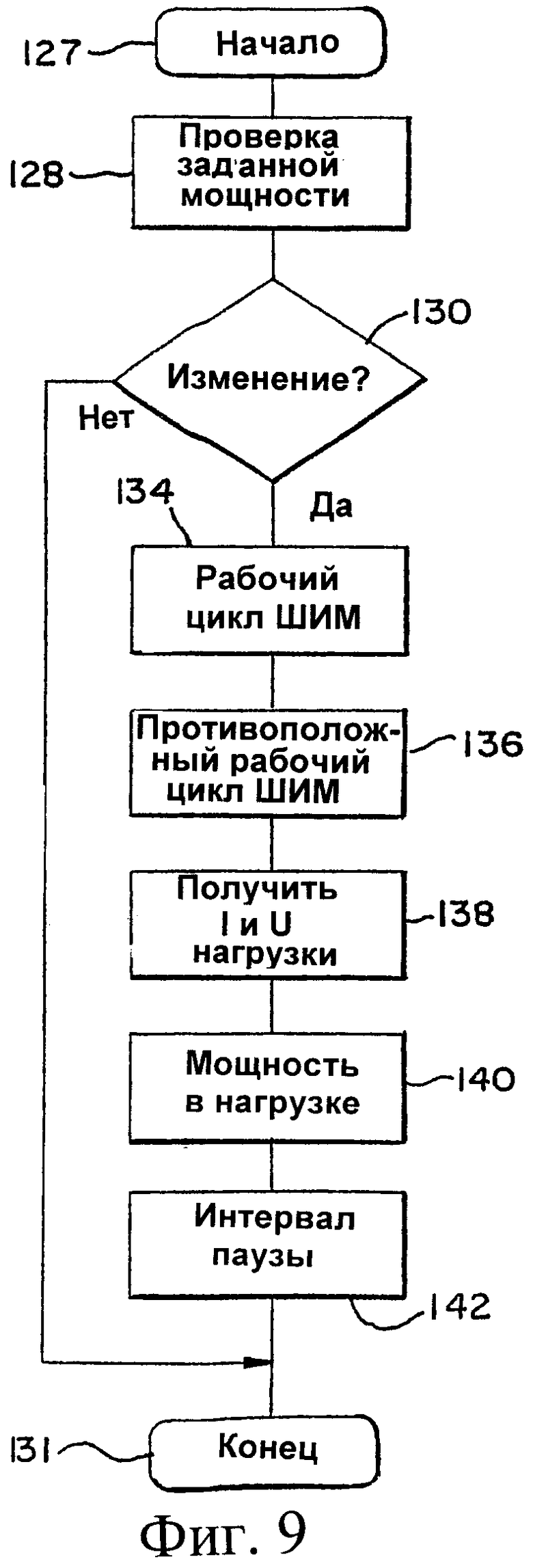

на фиг.9 приведена упрощенная блок-схема алгоритма процедуры, выполняемой программируемым контроллером диммера при подаче управляющих сигналов ШИМ последовательной коммутации, противоположных управляющих сигналов ШИМ ограничительной коммутации и интервалов паузы, используемых в процедуре, показанной на фиг.8.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

На фиг.1 приведена упрощенная блок-схема синхронного синусоидального диммера, обозначенного в целом позицией 20. Диммер 20 подключен к обычной сети 22 электропитания, подающей ток питания синусоидальной формы, например номинальные 120 В переменного напряжения. Диммер 20 подает выходную мощность в нагрузку 2-4. В стандартных приложениях нагрузка 24 может быть резистивной, такой как лампа накаливания, или реактивной, такой как источник питания для газоразрядных или флуоресцентных ламп. Каскад 26 коммутации мощности использует широтно-импульсную модуляцию (ШИМ) для уменьшения входной мощности и подачи уменьшенной выходной мощности на нагрузку.

Входной линейный фильтр 28 фильтрует шумы, которые могут присутствовать в сигнале питания, и обеспечивает подачу свободного от помех переменного тока в каскад коммутации мощности. Кроме того, входной линейный фильтр 28 фильтрует шумы переключения каскада 26 коммутации мощности и предотвращает попадание шумов обратно в сеть 22 электропитания. Предпочтительно, чтобы входной линейный фильтр 28, как показано на фиг.3, был линейным фильтром высокого порядка и содержал дроссель 30 для подавления синфазных помех, дроссели 32 для подавления дифференциальных помех, конденсаторы 34 типа Х для подавления дифференциальных помех линия - нейтраль и конденсаторы типа Y для подавления синфазных помех линия/нейтраль - заземление 36.

Выходной нагрузочный фильтр 38 отфильтровывает частоту переключения ШИМ каскада 26 коммутации мощности и восстанавливает форму выходного напряжения в виде синусоиды одной частоты и переменной амплитуды с такой же частотой, как у синусоиды напряжения питания. Как показано на фиг.4, выходной нагрузочный фильтр обычно может содержать шунтирующий конденсатор, представленный конденсатором 40. Основной частью нагрузочного фильтра является выходной дроссель 42, подключенный последовательно нагрузке 24, который запасает энергию и сглаживает форму выходного сигнала. Чтобы иметь возможность использовать широкий диапазон выходных нагрузок, желательно, чтобы дроссель 42 был дросселем переменной индуктивности. Например, дроссель 42 может иметь индуктивность 10 мГ при выходном токе 0,25 А, индуктивность 1 мГ при выходном токе 10 А и индуктивность 0,5 мГ при выходном токе 20 А.

Каскад 26 коммутации мощности содержит секцию 44 последовательной коммутации, включенную последовательно между источником питания 22 и последовательно соединенными нагрузкой 24 и нагрузочным дросселем 42. Каскад 26 коммутации мощности также содержит секцию 46 ограничительной коммутации, шунтирующую последовательно соединенные нагрузку 24 и выходной дроссель 42. Секция 44 последовательной коммутации поочередно становится проводящей и непроводящей с высокой частотой, которая задается сигналом ШИМ с рабочим циклом (коэффициентом заполнения), выбранным для получения требуемого уровня выходной мощности. Секция 46 ограничительной коммутации поочередно становится проводящей и непроводящей в зависимости от противоположного сигнала ШИМ, так что секция 46 ограничительной коммутации не проводит ток, когда секция 44 последовательной коммутации проводит ток, и, соответственно, секция 44 последовательной коммутации не проводит ток, когда секция 46 ограничительной коммутации его проводит. Предпочтительно, чтобы каскад 26 коммутации мощности работал на высокой частоте, как минимум 20 килогерц, предпочтительно на частоте 50 килогерц.

На фиг.2 графически иллюстрируется работа каскада 26 коммутации мощности. Рабочая частота, показанная на фиг.2, очень низка и не отражает реальной работы ШИМ на высокой частоте, но позволяет графически отобразить работу ШИМ. Кривая 48 показывает синусоидальную форму входного сигнала переменного тока. Кривая 50 показывает управляющий сигнал, переключающий секцию 44 последовательной коммутации поочередно в проводящее и непроводящее состояние в пятидесятипроцентном рабочем цикле. Кривая 52 показывает дополняющий управляющий сигнал для переключения секции 46 ограничительной коммутации поочередно в проводящее и непроводящее состояние. Кривая 54 демонстрирует сигнал в выходной нагрузке, получаемый в результате "нарезки" входного сигнала секцией 44 последовательной коммутации и сглаживания фильтром 38 выходной нагрузки. При пятидесятипроцентном рабочем цикле амплитуда выходного сигнала составляет приблизительно половину амплитуды синусоиды источника электропитания.

Как показано на фиг.1, программируемый контроллер на базе микропроцессора 56 управляет работой секций последовательной коммутации и ограничительной коммутации 44 и 46 с помощью сигналов управления переключением, таких как представленные на фиг.2. Контроллер 56 содержит память для программ и данных или имеет доступ к ней и программируется с помощью инструкций, загружаемых в память для программ в виде данных, поступающих по шине ввода-вывода данных или из устройства 58. Одним из примеров программируемых контроллеров, пригодных для осуществления данного изобретения, является гибридный процессор цифровых сигналов (DSP) модели 56 F803 и контроллер, поставляемый компанией Freestyle Semiconductor, Inc. (Motorola) и описанный в документе «56F803 Evaluation Module Hardware User's Manual, Rev.4, 06/03/2003», включенном в данное описание путем ссылки.

Контроллер 56 под управлением программного обеспечения подает высокочастотные сигналы ШИМ управления переключением на секцию 44 последовательной коммутации через цепь оптической развязки 60 и схему 62 управления. Аналогичным образом контроллер 56 под управлением программного обеспечения подает противоположные высокочастотные сигналы ШИМ для управления переключением на секцию 46 ограничительной коммутации через цепь оптической развязки 64 и схему 66 управления.

Контроллер 56 получает через линию 68 сигналы обратной связи, информирующие его о напряжении и токе нагрузки. Эти сигналы могут использоваться под управлением программы для настройки управляющих сигналов ШИМ и обратного ШИМ для точного регулирования сигнала выходной нагрузки. Кроме того, как будет сказано далее, эти сигналы могут использоваться для управления диммером 20 с целью максимального увеличения эффективности передачи мощности в нагрузку 24 в соответствии с данным изобретением.

По линии 70 контроллер 56 получает сигнал обратной связи, информирующий его о напряжении питания. Этот сигнал может использоваться под управлением программы для обнаружения момента перехода сигнала через ноль и настройки управляющих сигналов ШИМ и обратного ШИМ для точного регулирования сигнала в выходной нагрузке. Датчик 72, связанный с каскадом 26 коммутации мощности, обеспечивает сигнал обратной связи о рабочей температуре, который может использоваться, например, для снижения мощности или выключения прибора при чрезмерном повышении температуры.

Каскад 26 коммутации мощности более подробно показан на фиг.5. Секция 44 последовательной коммутации содержит комплементарную пару полевых МОП-транзисторов 68 и 70, которые работают в качестве высокоскоростного высокочастотного двунаправленного ключа, подключенного последовательно между выводом 72 источника мощности, подключенным к входному линейному фильтру 28, и выводом 74 нагрузки, подключенным к дросселю 42 выходного нагрузочного фильтра 38. Транзисторы 68 и 70 одновременно становятся проводящими или непроводящими согласно высокочастотному управляющему сигналу ШИМ, который подается от контроллера 56 через цепь 60 оптической развязки и схему 62 управления между входным выводом 76 управления затворами и выводом 77 заземления. Резисторы 78 контроля тока, подключенные между выводами земли и истоками полевых МОП-транзисторов 68 и 70, создают на выводах 80 сигналы, используемые в контроллере 56 для защиты от перегрузки по току или других подобных целей. Резисторы 82 работают как делители напряжения и стабилизирующие последовательные резисторы, подключенные к выводам затворов полевых МОП-транзисторов 68 и 70. Двунаправленные стабилитроны 84 обеспечивают защиту от резких скачков напряжения.

Секция 46 ограничительной коммутации содержит комплементарную пару полевых МОП-транзисторов 68 и 70, которые работают в качестве мощного быстродействующего двунаправленного ключа, включенного последовательно между выводом 74 нагрузки и нейтральным выводом 90 нагрузки. Транзисторы 86 и 88 одновременно становятся проводящими или непроводящими согласно противоположному высокочастотному управляющему сигналу ШИМ, который подается от контроллера 56 через цепь оптической развязки 64 и схему 66 управления между входным выводом 92 управления затвором и вывод 94 заземления. Резисторы 96 работают как делители напряжения и стабилизирующие последовательные резисторы, подключенные к выводам истоков полевых МОП-транзисторов 86 и 88. Двунаправленные стабилитроны 84 обеспечивают защиту от резких скачков напряжения.

Хотя для секций последовательной и ограничительной коммутации 44 и 46 могут использоваться и другие типы мощных твердотельных ключей, например IGBT, предпочтительнее использовать полевые МОП-транзисторы из-за их высокого быстродействия и параметров переключения при высокой мощности. Кроме того, двунаправленная природа и высокая скорость переключения полевых МОП-транзисторов делает их более предпочтительными для синхронных диммеров, требующих быстрого переключения как последовательных, так и ограничительных ключей.

В соответствии с данным изобретением контроллер 56 запрограммирован вставлять точно заданные паузы между сигналами управления последовательным ключом и ограничительным ключом. Это проиллюстрировано в целом без соблюдения масштаба на фиг.6. График 100 демонстрирует пару управляющих сигналов 102 включения для последовательной коммутации, которые переводят секцию 44 последовательной коммутации в проводящее состояние. Эти сигналы разделены интервалами выключения, в течение которых секция 44 последовательной коммутации не проводит ток. График 104 демонстрирует пару противоположных управляющих сигналов ШИМ 106 для ограничительной коммутации, которые переводят секцию 46 ограничительной коммутации в проводящее состояние. Сигнал 106 выключения на графике 104 расположен между интервалами выключения на кривой 100.

График 108 на фиг.6 иллюстрирует интервал паузы 110, начинающийся в конце каждого управляющего сигнала 102 последовательной коммутации и заканчивающийся в начале каждого управляющего противоположного сигнала 106 ШИМ. В течение этого интервала паузы ни секция 44 последовательной коммутации, ни секция 46 ограничительной коммутации не получают сигнала включения 102 или 106. Интервал 110 паузы выбирается достаточной продолжительности, чтобы переключение секции 44 последовательной коммутации могло надежно завершиться, и чтобы избежать состояния одновременной проводимости секции 44 последовательной коммутации и секции 46 ограничительной коммутации. Кроме того, интервал паузы выбирается по возможности достаточно кратким, т.е. не длиннее, чем необходимо для того, чтобы надежно завершить операцию переключения. В результате, после того как секция 44 последовательной коммутации переходит в непроводящее состояние, секция 46 ограничительной коммутации переходит в проводящее состояние настолько быстро, насколько возможно, чтобы образовать путь для эффективной передачи в нагрузку 24 энергии, запасенной в дросселе выходного фильтра нагрузки 42. Это позволяет избежать нежелательных всплесков напряжения, которые могут исказить требуемую форму выходной синусоиды и могут привести к повреждению компонентов схемы.

График 108 иллюстрирует также еще один интервал 112 паузы, начинающийся в конце каждого противоположного управляющего сигнала 106 ШИМ и заканчивающийся в начале каждого управляющего сигнала 102 ШИМ последовательной коммутации. Интервал 112 паузы выбирается достаточной продолжительности, чтобы переключение секции 46 ограничительной коммутации могло надежно завершиться, и чтобы избежать состояния одновременной проводимости секции 44 последовательной коммутации и секции 46 ограничительной коммутации. Если позволяют характеристики цепи и требования к рассеянию мощности, интервалы пауз 110 и 112 могут иметь различную длину, однако в настоящее время предпочтительной является одинаковая длина интервалов.

Интервалы пауз 110 и 112 формируются с помощью программного управления при помощи программируемого контроллера 56 на базе микропроцессора. Таким образом, интервалы пауз 110 и 112 имеют точные значения, не зависящие от сложно определяемых времени нарастания, спада и времени задержки компонентов цепи. В результате эффективное переключение и передача энергии в нагрузку 24 повышаются до максимума. На рекомендуемой частоте переключения ШИМ 50 килогерц при использовании интервалов пауз 110 и 112 фиксированной длины, как показано на фиг.6, рекомендуемая продолжительность пауз составляет 150 наносекунд.

Фиксированные интервалы пауз обеспечивают преимущества надежной и эффективной работы, но могут быть изменены, поскольку при возрастании полезной выходной мощности может возникнуть возможность уменьшить продолжительность пауз. В соответствии с особенностью данного изобретения контроллер 56 может быть запрограммирован задавать переменные интервалы 110 и 112 на основании мощности в нагрузке. Как показано на фиг.7, например, интервалы 110 и 112 могут линейно изменяться от максимального значения 170 наносекунд при очень низкой нагрузке или ее отсутствии до 110 наносекунд при выходной нагрузке 2500 ватт. Переменная продолжительность пауз может дополнительно повысить эффективность управления диммером 20.

Процедура, выполняемая программируемым контроллером 56 для управления секцией 44 последовательной коммутации и секцией 46 ограничительной коммутации, приведена на упрощенной блок-схеме на фиг.8. Процедура начинается с блока 114. В блоке 116 контроллер посылает последовательному ключу сигнал 102 включения (см. фиг.6) для переключения полевых МОП-транзисторов 68 и 70 секции последовательной коммутации 44 в проводящее состояние для пропускания тока через диммер 20 от источника 22 мощности к нагрузке 24. Продолжительность сигнала 102 хранится в памяти данных контроллера 56 и приводит к рабочему циклу ШИМ, нужному для получения необходимой синусоидальной формы выходного сигнала на нагрузке 24. По окончании сигнала 102 включения транзисторы 68 и 70 секции 44 последовательной коммутации возвращаются в непроводящее состояние, прерывая ток, идущий к дросселю 42 выходного фильтра и в нагрузку 24.

В блоке 118 контроллер 56 ожидает в течение интервала, равного интервалу 110 паузы. Этот интервал хранится в памяти данных контроллера 56. В течение этого интервала паузы 110 операция переключения секции последовательной коммутации полностью заканчивается.

В конце интервала паузы в блоке 120 контроллер посылает сигнал 106 включения (см. фиг.6) для приведения полевых МОП-транзисторов 86 и 88 секции 46 ограничительной коммутации в проводящее состояние. Это позволяет энергии, запасенной в дросселе 42 выходного нагрузочного фильтра, вызывать протекание тока в дросселе 42 и нагрузке 24. Продолжительность сигнала 106 хранится в памяти данных контроллера 56 и является результатом инвертирования рабочего цикла ШИМ, требуемого для получения необходимой синусоидальной формы выходного сигнала в нагрузке 24. По окончании сигнала 106 включения транзисторы 86 и 88 секции 46 ограничительной коммутации возвращаются в непроводящее состояние, прерывая ток между дросселем 42 и нагрузкой 24.

В блоке 122 контроллер 56 ожидает в течение интервала, равного интервалу 112 паузы. Этот интервал хранится в памяти данных контроллера 56. Если для обеих пауз 110 и 112 используются интервалы одинаковой продолжительности, хранить в памяти данных контроллера 56 необходимо только одно значение. В течение интервала 112 паузы операция переключения секции 46 ограничительной коммутации полностью заканчивается.

Блок принятия решения 124 включен в блок-схему, чтобы показать, что контроллер прекращает посылать управляющие сигналы секциям последовательной коммутации и ограничительной коммутации 44 и 46, например в случае отключения питания диммера 20 или прерывания его в ответ на сигнал обратной связи. Если работа диммера закончена, процедура заканчивается в конечном блоке 126, в противном случае процедура повторяется.

Фиг.9 иллюстрирует упрощенную периодическую процедуру получения или вычисления управляющих сигналов 102 и 106 и интервалов 110 и 112 пауз с последующим их сохранением в памяти данных. Эта процедура начинается с блока 127. Пользователь диммера 20 может выбрать амплитуду выходного сигнала, соответствующую, например, интенсивности света ламповой нагрузки, вводя данные в контроллер 56 по шине данных или с помощью устройства 58. В блоке 130 принятия решения эти входные данные проверяются, чтобы узнать, следует ли внести изменения в амплитуду выходного сигнала. Если нет, то процедура заканчивается в конечном блоке 131. В этом случае значения управляющих сигналов и интервалов пауз, сохраненные в памяти данных, остаются неизменными.

Если поступил запрос на изменение амплитуды, в блоках 132 и 134 устанавливаются новые рабочие циклы ШИМ и противоположной ШИМ. Существуют различные способы выполнения этих шагов. Контроллер 56 может вычислить рабочий цикл и противоположный рабочий цикл с помощью входных данных и сформировать соответствующие значения управляющих сигналов 102 и 106 последовательной коммутации и ограничительной коммутации. С другой стороны, в памяти контроллера может храниться справочная таблица, в которой хранятся значения управляющих сигналов 102 и 106 последовательной коммутации и ограничительной коммутации. В любом случае в блоках 134 и 136 продолжительность управляющих сигналов 102 и 106 последовательной коммутации и ограничительной коммутации сохраняется в памяти данных для доступа к ним из процедуры, показанной на фиг.8, блоки 116 и 120.

Если используются интервалы пауз фиксированной продолжительности, они могут быть сохранены в памяти данных контроллера 56 после ввода данных, поступивших по шине или из устройства 58. После этого интервал паузы из памяти может использоваться контроллером 56 в процедуре, приведенной на фиг.8, в блоках 118 и 122. В этом случае процедура может закончиться на блоке 131 после блока 136.

Если используются интервалы пауз переменной продолжительности, то процедура на фиг.9 также включает блоки 138-142. В блоке 138 контроллер 56 получает значения тока и напряжения нагрузки, получаемые по линии обратной связи 68 (фиг.1). В блоке 140 может быть вычислена или определена на основе значений тока и напряжения нагрузки мощность в нагрузке. В блоке 142 путем вычисления или поиска в таблице в памяти контроллера устанавливается интервал паузы. Например, в память данных может быть загружена таблица, базирующаяся на графике, показанном на фиг.7. В этом блоке значения интервалов пауз 110 и 112 или одно значение интервала паузы сохраняются в памяти данных для использования в процедуре, приведенной на фиг.8, в блоках 118 и 122.

Хотя изобретение было описано со ссылками на детали реализации изобретения, приведенные на чертежах, эти детали не означают ограничения изобретения по сравнению с формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХСТУПЕНЧАТАЯ ЭЛЕКТРОННАЯ НАГРУЗКА | 2009 |

|

RU2404439C1 |

| ИЗВЛЕЧЕНИЕ МОЩНОСТИ ДЛЯ ВСПОМОГАТЕЛЬНОГО УСТРОЙСТВА ИЗ СИГНАЛА, ПОДАВАЕМОГО НА СВЕТИЛЬНИК ОТ ФАЗОВОГО СВЕТОРЕГУЛЯТОРА | 2003 |

|

RU2292677C2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2003 |

|

RU2251786C2 |

| КОМПОНОВКА СХЕМЫ | 2013 |

|

RU2637307C2 |

| СПОСОБ УПРАВЛЕНИЯ ЧЕТЫРЕХКВАДРАНТНЫМ ПРЕОБРАЗОВАТЕЛЕМ С ВЫЧИСЛЕНИЕМ ФАЗ КОММУТАЦИИ И МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2006 |

|

RU2327276C1 |

| СПОСОБ УПРАВЛЕНИЯ ТРЕХФАЗНЫМ ИНВЕРТОРОМ НАПРЯЖЕНИЯ С ШИМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2091979C1 |

| СХЕМНОЕ УСТРОЙСТВО И СИД ЛАМПА, СОДЕРЖАЩАЯ ЭТО СХЕМНОЕ УСТРОЙСТВО | 2013 |

|

RU2638958C2 |

| СПОСОБ УПРАВЛЕНИЯ ИМПУЛЬСНЫМ СТАБИЛИЗАТОРОМ НАПРЯЖЕНИЯ | 2011 |

|

RU2460114C1 |

| СХЕМА ПРИВОДА ШАГОВОГО ДВИГАТЕЛЯ И СПОСОБ УПРАВЛЕНИЯ ПРИВОДОМ ШАГОВОГО ДВИГАТЕЛЯ | 2004 |

|

RU2357354C2 |

| ТРЕХФАЗНЫЙ ИСТОЧНИК БЕСПЕРЕБОЙНОГО ПИТАНИЯ БОЛЬШОЙ МОЩНОСТИ | 2010 |

|

RU2529017C2 |

Изобретение относится к области приборостроения и может найти применение в системах электропитания. Технический результат - расширение функциональных возможностей. Для достижения данного результата входной линейный фильтр (28) отделяет источник (22) переменного синусоидального тока от каскада (26) коммутации мощности. Секция (44) последовательной коммутации и секция (46) ограничительной коммутации содержат комплементарные пары (68-70 и 86-88) мощных быстродействующих полевых МОП-транзисторов. Секция (44) последовательной коммутации включена последовательно между входным линейным фильтром (28) и дросселем (42) выходного нагрузочного фильтра (38), который включен между каскадом (26) коммутации мощности и нагрузкой (24). Секция ограничительной коммутации (46) подключена параллельно дросселю (42) и нагрузке (24). Программируемый контроллер на базе микропроцессора (56) формирует управляющие сигналы (102, 106) для обеспечения поочередной проводимости секций последовательной и ограничительной коммутации. 3 н. и 14 з.п. ф-лы, 9 ил.

1. Способ управления синусоидальным диммером для формирования выходного сигнала мощности из сигнала источника мощности, имеющего различную форму, включающий

подачу сигнала широтно-импульсной модуляции, имеющего рабочий цикл, соответствующий требуемой величине выходного сигнала;

поочередное переключение в проводящее состояние устройства последовательной коммутации между источником питания и интегрирующим фильтром и устройства ограничительной коммутации, шунтирующего интегрирующий фильтр;

при этом указанное переключение включает приведение устройства последовательной коммутации в проводящее состояние в соответствии с указанным сигналом широтно-импульсной модуляции и приведение устройства ограничительной коммутации в проводящее состояние в соответствии с противоположным ему сигналом широтно-импульсной модуляции; и

разделение каждого из чередующихся проводящих состояний устройства последовательной коммутации и устройства ограничительной коммутации интервалом паузы, в котором как первая, так и вторая цепь находятся в непроводящем состоянии.

2. Способ по п.1, в котором указанные выходной сигнал мощности и сигнал источника мощности имеют синусоидальную форму.

3. Способ по п.2, в котором указанное переключение и разделение выполняют посредством программируемого контроллера на базе микропроцессора, имеющего память, и указанный интервал паузы хранят в этой памяти.

4. Способ по п.3, в котором интервалы пауз, следующие за проводящим состоянием устройства последовательной коммутации, имеют такую же длину, как интервалы пауз, следующие за проводящим состоянием устройства ограничительной коммутации.

5. Способ по п.4, в котором частота широтно-импульсной модуляции превышает приблизительно двадцать килогерц.

6. Способ по п.5, в котором частота широтно-импульсной модуляции составляет около пятидесяти килогерц.

7. Способ по п.5, в котором интервалы пауз находятся в диапазоне от приблизительно 100 до приблизительно 180 наносекунд.

8. Способ по п.5, в котором интервалы пауз имеют продолжительность около 150 наносекунд.

9. Способ по п.5, в котором интервалы пауз имеют фиксированную продолжительность.

10. Способ по п.5, также содержащий подачу информации о выходной мощности по обратной связи в контроллер и изменение интервала паузы в контроллере в соответствии с изменениями информации о выходной мощности, поступающей по обратной связи.

11. Способ по п.10, в котором интервал паузы увеличивают при уменьшении выходной мощности.

12. Способ управления синусоидальным диммером для формирования выходного сигнала мощности из сигнала источника мощности, имеющего различную форму, содержащий

подачу сигнала широтно-импульсной модуляции, имеющего рабочий цикл, соответствующий требуемой величине выходного сигнала мощности;

поочередное переключение в проводящее состояние устройства последовательной коммутации между источником питания и интегрирующим фильтром и устройства ограничительной коммутации, шунтирующего интегрирующий фильтр;

при этом указанное переключение включает приведение устройства последовательной коммутации в проводящее состояние в соответствии с указанным сигналом широтно-импульсной модуляции и приведение устройства ограничительной коммутации в проводящее состояние в соответствии с противоположным ему сигналом широтно-импульсной модуляции; и

введение после каждого проводящего состояния устройства последовательной коммутации интервала паузы, в котором как первая, так и вторая цепь находятся в непроводящем состоянии;

причем указанное переключение и последующие шаги выполняются программируемым контроллером на базе микропроцессора, имеющим память, в которой хранится указанный интервал паузы.

13. Синхронный синусоидальный диммер для использования с нагрузкой и источником мощности переменного тока, содержащий

входной линейный фильтр для подключения к источнику мощности;

выходной нагрузочный фильтр, имеющий выходной нагрузочный дроссель, подключаемый последовательно нагрузке;

каскад коммутации мощности между указанным входным линейным фильтром и указанным выходным нагрузочным фильтром, указанный каскад коммутации мощности имеет секцию последовательной коммутации, включенную последовательно указанному выходному нагрузочному фильтру и нагрузке, и секцию ограничительной коммутации, подключенную параллельно указанному выходному нагрузочному фильтру и нагрузке;

программируемый контроллер на базе микропроцессора, имеющий вход и память, указанный контроллер формирует управляющие сигналы последовательной и ограничительной коммутации для поочередного приведения указанных секций последовательной и ограничительной коммутации в проводящее состояние с рабочим циклом широтно-импульсной модуляции, базирующимся на информации о мощности в нагрузке, поступившей на указанный вход программируемого контроллера;

при этом в указанной памяти хранится интервал паузы, используемый указанным контроллером для разделения указанных управляющих сигналов последовательной и ограничительной коммутации.

14. Синхронный диммер по п.13, в котором указанный интервал паузы фиксирован.

15. Синхронный диммер по п.14, в котором указанный интервал паузы составляет приблизительно 150 наносекунд.

16. Синхронный диммер по п.13, также содержащий цепь обратной связи по выходной мощности между нагрузкой и указанным контроллером, при этом указанный контроллер изменяет указанный интервал паузы в соответствии с изменениями выходной мощности.

17. Синхронный диммер по п.13, в котором как указанная секция последовательной коммутации, так и указанная секция ограничительной коммутации содержат комплементарные пары полевых МОП-транзисторов.

| US 4998046 А, 05.03.1991 | |||

| US 5424618 А, 13.06.1995 | |||

| US 5500576 А, 19.03.1996 | |||

| US 5714847 A, 03.02.1998 | |||

| US 6346778 B1, 12.02.2002. |

Авторы

Даты

2009-10-20—Публикация

2005-09-15—Подача