,

Изобретение относится к области кодирования и преобразования информации.

Известен управляемый делитель частоты повторения импульсов с дробно-рациональлыми коэффициентами деления, содержащий qразрядный двоичный умножитель частоты, вход независимой переменной которого подключен через схему запрета ко входу делителя.

Известное устройство имеет недостаточно высокую надежность.

Цель изобретения - повышение надежности работы делителя.

Цель достигается тем, что устройство содержит удвоитель частоты, две вентильные схемы, инвертор, схему «ИЛИ и схему сдвига кодов, входами приема кодов соединенную с кодовыми шинами знаменателя заданного коэффициен1та деления, а двоичный умножнтель, соединенный входами приема кодов подинтегральной функции с кодовыми шинами числителя, а выходом - со входом запрещения схемы запрета, содержит дополнительный двоичный разряд в счетчике импульсов независимой переменной и дополнительную группу вентилей, состоящую из q-{- потенциально-импульсных вентилей, соединенных импульсными входами с параллельными выходами счетчика импульсов независимой переменной, причем выходы выдачи параллельных

кодов схемы сдвига кодов соединены с потенциальными входами дополнительной группы вентилей, выходы которых объединены и подключены к управляемым входам вентильных схем; кодовая щива старшего разряда (9+1)-разрядного знаменателя (щива признака равенства числа разрядов числителя и знаменателя заданного коэффициента деления) соединена со входом инвертора и входом запрещения первой вентильной схемы, выход которой соединен со входом удвоителя частоты, а выход инвертора соединен со входом управления сдвигом схемы сдвига кодов и со входом запрещения второй вентильной схемы, выход которой соединен со входом схемы «ИЛИ, вторым входом соединенной с выходом удвоителя частоты , а выходом - с выходом делителя.

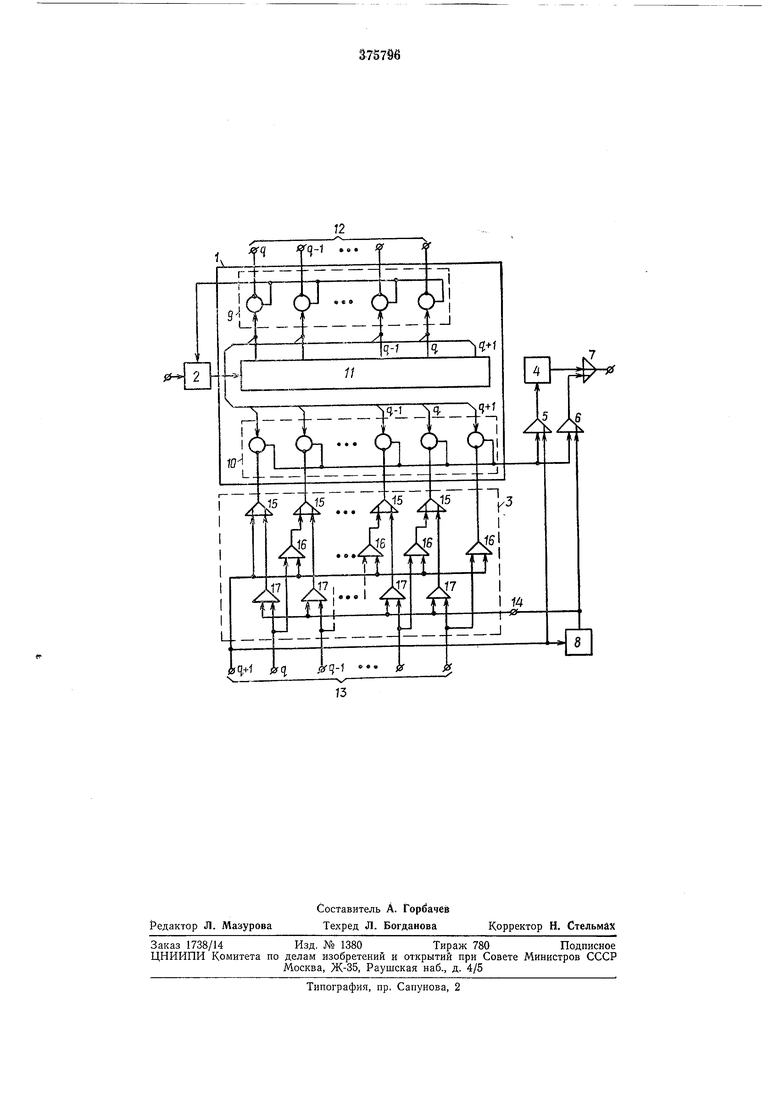

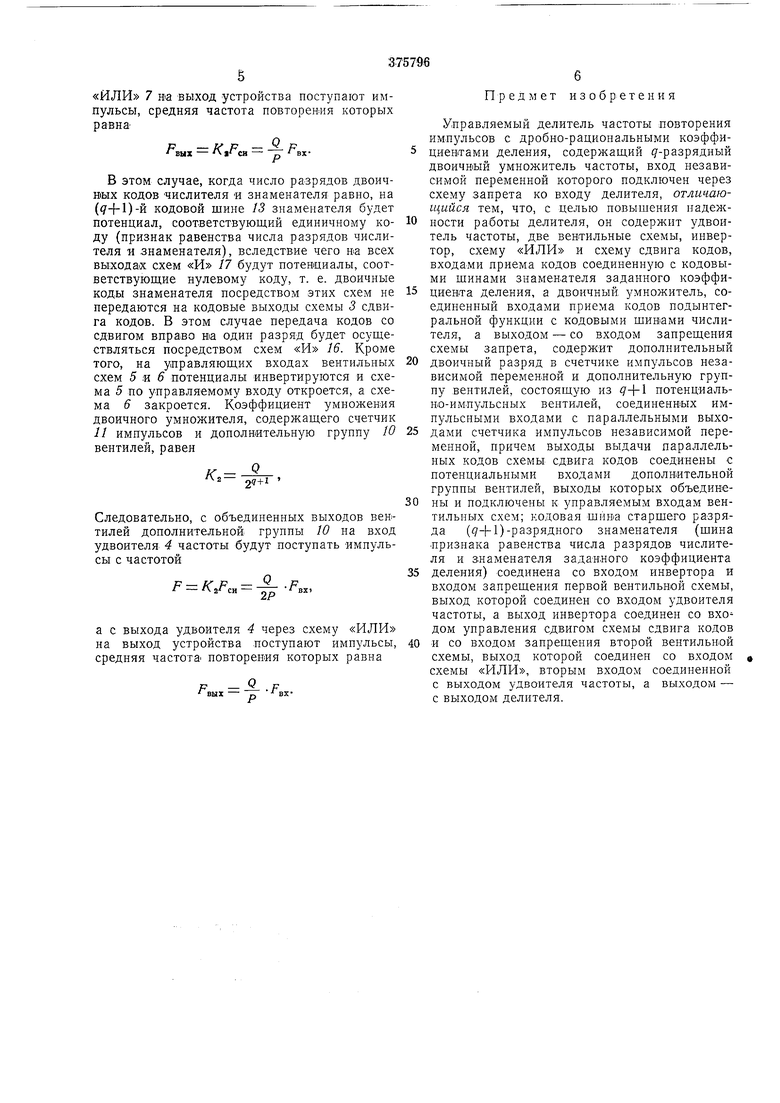

На чертеже приведена функциональная схема управляемого делителя частоты повторения импульсов с дробно-рацион альными коэффициеитами деления.

Устройство состоит из двоичного умножи теля /, схемы 2 запрета, схемы 3 сдвига кодов, удвоителя 4 частоты, вентильных схем 5 и 6, схемы «ИЛИ 7 и инвертора 8. Двоичный умножитель / содержит основную г.рутту 9 и дополнительную группу JO потенциальноимпульсных вентилей и счетчик 11 импульсов независимой перемеввой, имеющий q младших основных двоичных разрядов и (|7+1)-й старший дополнительный двоичный разряд. q вентилей основной и донолнительной групп 9 VI 10 импульсными входами подключены к q младшим разрядам счетчика // имнульсов независимой переменной, а (9+О-и вентиль дополнительной группы 10 подключен импульсным входом к выходу (9+1)-го разряда счетчика // импульсов. Устройство имеет кодовые шины 12 числителя, соединенные с потенциальными входами вентилей основной группы. Кодовые шины 13 знаменателя соединены со входами приема кодов схемы 3 сдвига кодов, вход управления сдвигом которой соединен с клеммой 14. Схема 3 сдвига кодов содержит группу схем «ИЛИ /5 и две группы схем и 17. Для правильной работы устройства необходимо соблюдать следующие условия + 1, где Р, Q - числа, представляющие в двоичном коде соответственно числитель и знаменатель заданного дробного коэффициента деления; т - число двоичных разрядов числителя;п - число двоичных разрядов знаменателя. Исходя из заданных условий и учитывая то, что со стороны ввода кодов числителя двоичный умножитель / «меет q разрядов, а со стороны ввода кодов знаменателя-(9+1) разрядов, число двоичных разрядов числителя должно быть равно 9+1. т. е. на шинах 12 ввода кодов числителя необходимо установить код q младших разрядов заданного (9+1) -разрядного кода числителя, что следует из того, что 9 - разрядный двоичный умножитель, с включенной на входе схемой 2 запрета, представляет собой делитель частоты с дробными коэффициентами деления /Сь ограниченными следующими условиями: ,1, причем условие выполняется, когда дробная часть коэффициента деления равна нулю. Устройство может работать в двух несколько отличительных режимах. Исходя из этого и рассмотрим работу устройства, предполагая, что для первого режима /п /г 9 + 1 для второго режима. На кодовые шины 12 в виде потенциалов подается двоичный код младших разрядов (9+1)-разрядного числителя, т. е. единица, находящаяся в старшем разряде числителя, отбрасывается. Так как для первого режима числа разрядов двоичного кода знаменателя меньше числа двоичвых разрядов числителя, то на кодовой ()-и шине 13 знаменателя наблюдается потенциал соответствующий нулевому коду. Этот потенциал поступает на входы схем «И 16, схемы 3 сдвига кодов, вход инвертора 8 и управляющий вход вентильной схемы 5. На выходах схем «И 16 будут потенциалы, соответствующие нулевому коду, т. е. передача кодов знаменателя через схемы «И .16, «ИЛИ 15 на кодовые входы двоичного умножителя / не производится. Потенциал, поступающий на управляющий вход вентильной схемы 5, запрещает прохождение выходных импульсов двоичного умножителя / на вход удвоителя 4 частоты. На выходе инвертора 8 |будет потенциал, соответствующий единичному коду, вследствие чего через схемы «И 17, «ИЛИ 15 происходит передача кодов знаменателя на кодовые входы двоичного умножителя /, т. е. ва: потенциальные входы дополнительной группы 10 вентилей. Кроме того, выходной потенциал инвертора 8 поступает на управляющий вход вентильной схемы 6, открывает ее, и импульсы с выходов вентилей дополнительной группы 10 че|рез схему «ИЛИ 7 поступают на выход устройства. Для всех КОДОВ знаменателя с числом двоичных разрядов ва потенциальный вход (7+1)-го вентиля, входящего в дополнительную группу 10 вентилей, будет поступать потенциал, соответствующий нулевому, коду, т. е. этот вентиль и дополнительный старший разряд счетчика 11 не будут участвовать в формировании выходной последовательности импульсов. Учитывая то, что 9-разряднЫЙ двоичный умножитель с включенной на входе схемой 2 запрета представляет собой делитель частоты с дробными коэффициентами деления, для рассматриваемого случая можно записать значение средней частоты повторения импульсов на входе счетчика // импульсов 21 Р --Lii- L.P R /С, Р где FBX - частота на входе устройства (на входе схемы 2 запрета); - частота на входе счетчика 11 импульсов (на выходе схемы 2 запрета). Счетчик 11 импульсов совместно с q вентилями дополнительной группы 10 составляют двоичный умножитель частоты с коэффициентом умножения К 21 из чего следует, что с объединенных выходов вентилей дополнительной- группы 10 через открытую вентильную схему 6 и cxeMV «ИЛИ 7 иа выход устройства поступают импульсы, средняя частота повтореиия которых равна 17 д с , У С вых - си - вхВ этом случае, когда число разрядов двоичных кодов Числителя и знаменателя равно, на (q+l)-K кодовой щине /5 знаменателя будет потенциал, соответствующий единичному коду (признак равенства числа разрядов числителя и знаменателя), вследствие чего ва всех выходах схем «И 17 будут потенциалы, соответствующие нулевому коду, т. е. двоичные коды знаменателя посредством этих схем не передаются на кодовые выходы схемы 3 сдвига кодов. В этом случае передача кодов со сдвигом вправо ва один разряд будет осуществляться посредством схем «И 16. Кроме того, на управляющих входах вентильных схем 5 я 6 потенциалы инвертируются и схема 5 по управляемому входу откроется, а схема 6 закроется. Коэффициент умножения двоичного умножителя, содержащего счетчик 11 импульсов и дополнительную группу 10 вентилей, равен Следовательно, с объединенных выходов вентилей дополнительной группы 10 на вход удвоителя 4 частоты будут поступать -импульсы с частотой - „р BXt а с выхода удвоителя 4 через схему «ИЛИ на выход устройства поступают импульсы, средняя частота повторения которых равна Г --5-.F вых - р вхПредмет изобретения Управляемый делитель частоты повторения импульсов с дробно-рациональными коэффициевтами деления, содержащий -разрядный двоичный умножитель частоты, вход независимой переменной которого подключен через схему запрета ко входу делителя, отличающийся тем, что, с целью повышения надежности работы делителя, он содержит удвоитель частоты, две вентильные схемы, инвертор, схему «ИЛИ и схему сдвига кодов, входами приема кодов соединенную с кодовыми шинами знаменателя заданного коэффициевта деления, а двоичный, умножитель, соединенный входами приема кодов подынтегральной функции с кодовыми шинами числителя, а выходом - со входом запрещения схемы запрета, содержит дополнительный двоичный разряд в счетчике импульсов независимой переменной и дополнительную группу вентилей, состоящую из д-}-1 потенциально-импульсных вентилей, соединенных импульсными входами с параллельными выходами счетчика импульсов независимой переменной, причем выходы выдачи параллельных кодов схемы сдвига кодов соединены с потенциальными входами дополнительной группы вентилей, выходы которых объединены и подключены к управляемым входам вентильных схем; кодовая шнна старшего разряда (7+1)-разрядного знаменателя (шина признака равенства числа разрядов числителя и з-наменателя заданного коэффициента деления) соединена со входом инвертора и входом запрещения первой вентильной схемы. ВЫХОД которой соединен со входом удвоителя частоты, а выход инвертора соединен со вхо дом управления сдвигом схемы сдвига кодов и со входом запрещения второй вентильной схемы, выход которой соединен со входом схемы «ИЛИ, вторым входом соединенной с выходом удвоителя частоты, а выходом - с выходом делителя.

jyq

Л,

г

151

CH Cb

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1973 |

|

SU396834A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1971 |

|

SU316198A1 |

| Импульсно-дискретное устройство для изменения частоты следования импульсов | 1977 |

|

SU621100A1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Измеритель скорости распространения ультразвуковых колебаний в материалах | 1973 |

|

SU484456A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Устройство для измерения частоты и сдвига фаз | 1974 |

|

SU525031A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ ПОВТОРЕНИЯ ИМПУЛЬСОВ | 1972 |

|

SU436444A1 |

| Делитель частоты следования импульсов с управляемым дробным коэффициентом деления | 1982 |

|

SU1043827A1 |

)jq.+1 A(J q-1

-, -.-,.. - .- -

J3

Даты

1973-01-01—Публикация